## **Discontinued Product**

This device is no longer in production. The device should not be purchased for new design applications. Samples are no longer available.

Date of status change: June 30, 2017

## **Recommended Substitutions:**

For existing customer transition, and for new customers or new applications, contact Allegro Sales.

NOTE: For detailed information on purchasing options, contact your local Allegro field applications engineer or sales representative.

Allegro MicroSystems reserves the right to make, from time to time, revisions to the anticipated product life cycle plan for a product to accommodate changes in production capabilities, alternative product availabilities, or market demand. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

### **Features and Benefits**

- Active current sharing between LED strings for  $\pm 0.6\%$  accuracy and matching

- Drives up to 12 series  $\times$  6 parallel = 72 LEDs ( $V_f$  = 3.2 V,  $I_f$  = 20 mA) at 5 V

- Each individual current sink is capable of 35 mA

- Adjustable overvoltage protection (OVP)

- 600 kHz to 2 MHz adjustable switching frequency

- Open or shorted LED string protection

- Open Schottky diode protection

- Overtemperature, cycle-by-cycle current limit, undervoltage, and soft start time-out protections

- Selectable latched/auto-restart protection modes

- No audible MLCC noise during PWM dimming

- No pull-up resistors required for LED modules that use ESD capacitors

Continued on the next page...

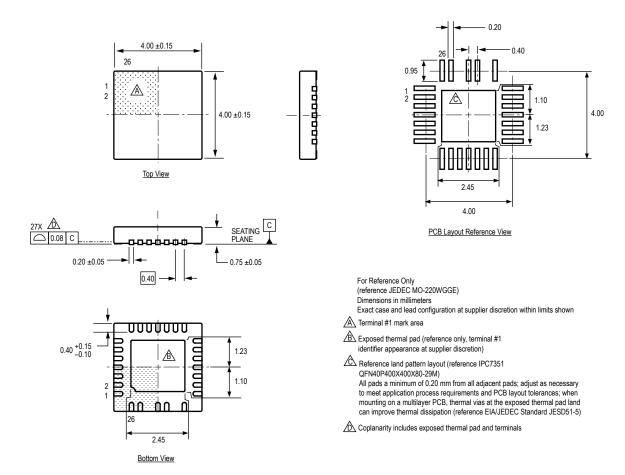

## Package: 26 contact MLP/QFN (suffix EC)

## **Description**

The A8503 is a multi-output WLED/RGB LED driver for medium-size LCD backlighting. It integrates a current-mode boost converter with internal power switch and six current sinks. The boost converter can provide output voltages up to 47 V. The boost converter can drive up to 72 LEDs at 20 mA per LED with a battery voltage down to 5 V. The LED sinks are capable of sinking up to 35 mA each, and can also be paralleled together to achieve even higher LED currents. The A8503 provides protection against overvoltage, open diode, open or shorted LED string, and overtemperature. A dual level cycle-by-cycle current limit function provides soft start and protects against overloads. A soft start timeout monitor is provided to enhance protection when starting up into a fault condition.

When the MODE pin is set low, the A8503 latches on a fault, and can be re-enabled only by cycling the input voltage,  $V_{\rm IN}$ , or by toggling the EN pin. Connecting the MODE pin high provides auto-restart after fault events. The A8503 features

Continued on the next page...

## **Applications**

- Notebook and sub-notebook displays

- LCD monitors

- LCD panels

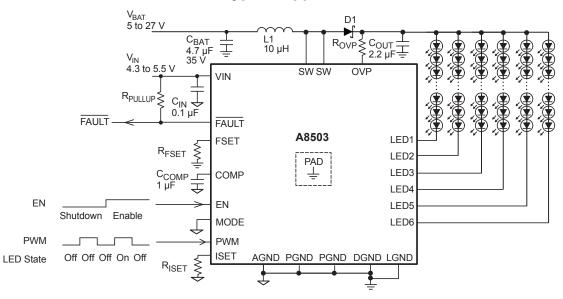

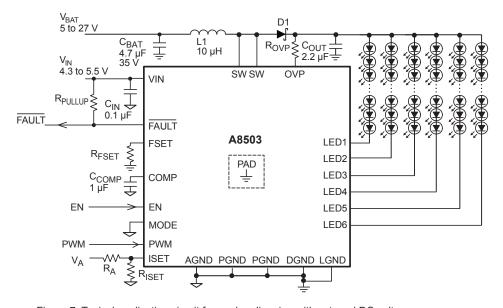

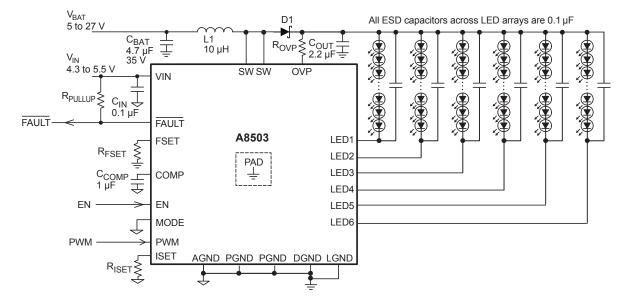

## **Typical Application**

Figure 1. Typical application circuit

## High Efficiency 6-Channel, 2 MHz, WLED/RGB Driver for Medium Displays, with Integrated 55 V Power Switch

### Features and Benefits (continued)

- Extends battery life

- Efficiency optimized for 3-cell notebooks

- 0.1 μA shutdown current

- Unique architecture eliminates external voltage divider and associated battery drain

- Rugged and small footprint solution

- $^{\circ}$  55 V, 2 A DMOS switch in 4 mm  $\times$  4 mm package—allows IPC-2221/2 / IPC-D-275 compliant PCB layout

### **Description (continued)**

EN (enable) and PWM (dimming) pins to comply with popular notebook backlight control interfaces.

The device is offered in a 26-contact, 4 mm  $\times$  4 mm, 0.75 mm nominal overall height QFN, with exposed pad for enhanced thermal dissipation. It is lead (Pb) free, with 100% matte tin leadframe plating.

#### **Selection Guide**

| Part Number  | Packing                    | Package                                     |

|--------------|----------------------------|---------------------------------------------|

| A8503GECTR-T | 1500 pieces per 7-in. reel | 26-contact QFN/MLP with exposed thermal pad |

### **Absolute Maximum Ratings**

| Characteristic                | Symbol               | Notes   | Rating     | Units |

|-------------------------------|----------------------|---------|------------|-------|

| SW Pins                       | V <sub>SW</sub>      |         | -0.3 to 57 | V     |

| LED1 through LED6 Pins        | V <sub>LEDx</sub>    |         | -0.3 to 34 | V     |

| OVP Pin                       | V <sub>OVP</sub>     |         | -0.3 to 47 | V     |

| Remaining Pins                |                      |         | -0.3 to 7  | V     |

| Operating Ambient Temperature | T <sub>A</sub>       | Range G | -40 to 105 | °C    |

| Maximum Junction Temperature  | T <sub>J</sub> (max) |         | 150        | °C    |

| Storage Temperature           | T <sub>stg</sub>     |         | -55 to 150 | °C    |

#### **Thermal Characteristics**

| Characteristic             | Symbol         | Test Conditions*                                   | Value | Units |

|----------------------------|----------------|----------------------------------------------------|-------|-------|

| Package Thermal Resistance | $R_{	heta JA}$ | EC package, on 4-layer PCB based on JEDEC standard | 35    | °C/W  |

<sup>\*</sup>Additional thermal information available on the Allegro website

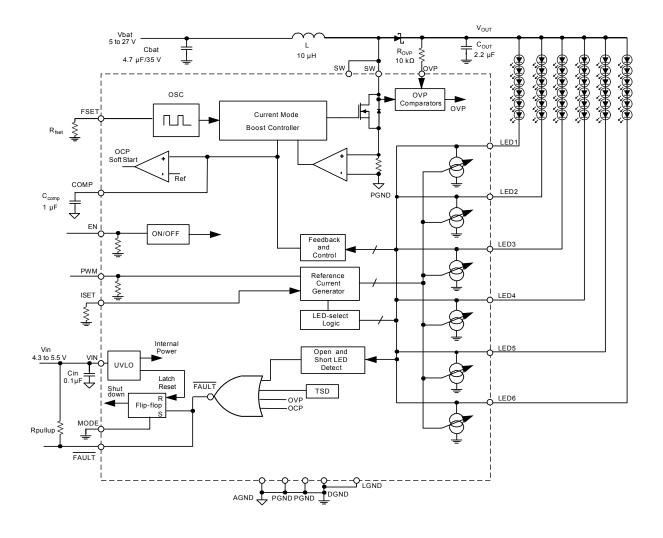

## **Functional Block Diagram**

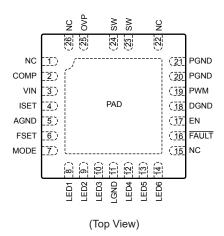

## **Pin-out Diagram**

### **Terminal List Table**

| Name  | Number                                                                                                                               | Function                                                                                                                                                             |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AGND  | 5                                                                                                                                    | Connect to common star ground                                                                                                                                        |  |  |  |  |

| COMP  | 2                                                                                                                                    | Compensation pin; connect 1 µF capacitor to AGND or common star ground                                                                                               |  |  |  |  |

| DGND  | 18                                                                                                                                   | Digital ground; connect to common star ground                                                                                                                        |  |  |  |  |

| EN    | 17                                                                                                                                   | Device enable                                                                                                                                                        |  |  |  |  |

| FAULT | 16                                                                                                                                   | During normal operation, this pin is high (high impedance); at a fault event, this pin pulls low                                                                     |  |  |  |  |

| FSET  | 6                                                                                                                                    | Set switching frequency; connect R <sub>FSET</sub> from FSET to AGND                                                                                                 |  |  |  |  |

| ISET  | 4                                                                                                                                    | Sets 100% current through LED string; connect R <sub>ISET</sub> from ISET to AGND                                                                                    |  |  |  |  |

| LEDx  | 8,9,10,11,<br>12,13,14 LED current sinks; connect unused LEDx pins to ground                                                         |                                                                                                                                                                      |  |  |  |  |

| LGND  | 11                                                                                                                                   | Power ground pin for LEDx current sinks; connect to common star ground                                                                                               |  |  |  |  |

| MODE  | 7                                                                                                                                    | Apply V <sub>IL</sub> for latching faults, apply V <sub>IH</sub> for auto-restart; see Fault Mode table                                                              |  |  |  |  |

| NC    | 1, 15, 22, 26                                                                                                                        | Not connected internally                                                                                                                                             |  |  |  |  |

| OVP   | 25                                                                                                                                   | Connect this pin to output capacitor +ve node through $R_{OVP}$ to enable overvoltage protection; select $R_{OVP} > 10 \text{ k}\Omega$ ( $V_{OVP}$ is 44 V typical) |  |  |  |  |

| PAD   | Exposed thermal pad, common star ground for PGND, DGND, LGND, and AGND; connect to copplane of the application PCB for heat transfer |                                                                                                                                                                      |  |  |  |  |

| PGND  | 20, 21                                                                                                                               | Power ground; connect both pins to common star ground                                                                                                                |  |  |  |  |

| PWM   | 19                                                                                                                                   | PWM LED-current control; apply logic level PWM for dimming                                                                                                           |  |  |  |  |

| SW    | 23, 24                                                                                                                               | DMOS switch drain node; tie SW pins together on the PCB                                                                                                              |  |  |  |  |

| VIN   | 3                                                                                                                                    | Input supply for the IC; decouple with a 0.1 µF ceramic capacitor                                                                                                    |  |  |  |  |

## High Efficiency 6-Channel, 2 MHz, WLED/RGB Driver for Medium Displays, with Integrated 55 V Power Switch

**ELECTRICAL CHARACTERISTICS**¹ Valid using circuit shown in figure 1,  $T_A = T_J = 25$ °C except • indicates specifications guaranteed from −40°C to 105°C,  $V_{IN} = 5.0$  V, EN = PWM =  $V_{IH}$ ,  $R_{ISET} = 12.4$  kΩ,  $R_{FSET} = 34$  kΩ, MODE = AGND, unless otherwise noted

| Characteristics                                    | Symbol Test Conditions |                                                                      |   | Min. | Typ. <sup>2</sup> | Max. | Unit |

|----------------------------------------------------|------------------------|----------------------------------------------------------------------|---|------|-------------------|------|------|

| Input Voltage Range                                | V <sub>IN</sub>        |                                                                      | • | 4.2  | _                 | 5.5  | V    |

| Undervoltage Lockout Threshold                     | V <sub>UVLO</sub>      | V <sub>IN</sub> falling                                              | • | _    | _                 | 4.0  | V    |

| Undervoltage Lockout Hysteresis Window             | V <sub>UVLOHYS</sub>   |                                                                      |   | _    | 0.1               | _    | V    |

|                                                    |                        | Switching, at no load                                                |   | _    | 7                 | _    | mA   |

| Supply Current                                     | I <sub>VIN</sub>       | Shutdown, EN= V <sub>IL</sub> , T <sub>A</sub> = 25°C                |   | _    | 0.1               | 1    | μA   |

|                                                    |                        | Standby, EN = V <sub>IH</sub> , PWM = V <sub>IL</sub>                | • | _    | 1                 | 2    | mA   |

| Boost Controller                                   |                        |                                                                      |   |      |                   |      |      |

| Switching Frequency                                | f <sub>SW</sub>        |                                                                      | • | 1.2  | 1.5               | 1.9  | MHz  |

| Minimum Switch Off-Time                            | t <sub>off(min)</sub>  |                                                                      |   | _    | 72                | _    | ns   |

| Minimum Switch On-Time                             | t <sub>on(min)</sub>   |                                                                      |   | _    | 72                | _    | ns   |

| Logic Input Levels (EN and PWM pins)               |                        |                                                                      |   |      |                   |      |      |

| Input Voltage Level Low                            | V <sub>IL</sub>        |                                                                      | • | _    | _                 | 0.4  | V    |

| Input Voltage Level High                           | V <sub>IH</sub>        |                                                                      | • | 1.5  | _                 | _    | V    |

| Input Leakage Current                              | I <sub>ILKG</sub>      | EN = PWM = 5 V                                                       |   | _    | 100               | _    | μA   |

| Overvoltage Protection                             |                        |                                                                      |   |      |                   |      |      |

| Output Overvoltage Threshold                       | V <sub>OVP</sub>       |                                                                      |   | _    | 44                | _    | V    |

| Overvoltage Protection Leakage Current             | I <sub>OVPLKG</sub>    | $V_{OVP}$ = 22 V, $R_{OVP}$ = 0 $\Omega$ , EN = $V_{IL}$             |   | _    | 0.1               | _    | μA   |

| Overvoltage Protection Sense Current               | I <sub>OVPH</sub>      |                                                                      |   | _    | 240               | _    | μA   |

| Boost Switch                                       |                        |                                                                      |   |      |                   |      |      |

| Switch On-Resistance                               | R <sub>DS(on)</sub>    | I <sub>SW</sub> = 1 A                                                |   | _    | 250               | _    | mΩ   |

| Switch Leakage Current                             | I <sub>SWLKG(B)</sub>  | V <sub>SW</sub> = 22 V                                               |   | _    | 0.1               | _    | μA   |

| Switch Current Limit                               | I <sub>SWLIM</sub>     |                                                                      |   | -    | 2.7               | -    | Α    |

| LED Current Sinks                                  |                        |                                                                      |   |      |                   |      |      |

| LEDx Pin Regulation Voltage                        | V <sub>LEDx</sub>      |                                                                      |   | _    | 600               | _    | mV   |

| I <sub>SET</sub> to I <sub>LEDx</sub> Current Gain | A <sub>ISET</sub>      | I <sub>SET</sub> = 100 μA                                            |   | _    | 320               | _    | A/A  |

| ISET Pin Voltage                                   | V <sub>ISET</sub>      |                                                                      |   | _    | 1.235             | _    | V    |

| ISET Allowable Current Range                       | I <sub>SET</sub>       |                                                                      | • | 33   | _                 | 110  | μA   |

| LEDx Current Accuracy <sup>3</sup>                 | Err <sub>ILEDX</sub>   | LED1 through LED6 = 0.6 V, at 100% Current                           | • | -3   | ±0.6              | 3    | %    |

| LEDx Current Matching <sup>4</sup>                 | $\Delta I_{LEDX}$      | I <sub>SET</sub> = 100 μA, LED1 though LED6 = 0.6 V, at 100% Current | • | -3   | ±0.6              | 3    | %    |

| Switch Leakage Current (LEDx)                      | I <sub>SWLKG(L)</sub>  | V <sub>LEDx</sub> = 12 V, EN = 0                                     |   | _    | 0.1               | _    | μΑ   |

| LED Short-Detect Voltage                           | V <sub>SC</sub>        | LEDx pin voltage level that forces latched shutdown, MODE = low      |   | _    | 18.7              | _    | V    |

## High Efficiency 6-Channel, 2 MHz, WLED/RGB Driver for Medium Displays, with Integrated 55 V Power Switch

**ELECTRICAL CHARACTERISTICS¹** (continued) Valid using circuit shown in figure 1, T<sub>A</sub> = T<sub>J</sub> = 25°C except ● indicates specifications guaranteed from -40°C to 105°C,  $V_{IN} = 5.0 \text{ V}$ ,  $EN = PWM = V_{IH}$ ,  $R_{ISET} = 12.4 \text{ k}\Omega$ ,  $R_{FSET} = 34 \text{ k}\Omega$ , MODE = AGND, unless otherwise noted

| Characteristics Symbol         |                        | Test Conditions                                                                                                        |   | Min. | Typ. <sup>2</sup> | Max. | Unit            |

|--------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------|---|------|-------------------|------|-----------------|

| Soft Start                     |                        |                                                                                                                        |   |      |                   |      |                 |

| Soft Start Boost Current Limit | I <sub>SW(SS)</sub>    | Initial soft start current for boost switch                                                                            |   | -    | 0.4               | -    | Α               |

| Soft Start LEDx Current Limit  | I <sub>LED(SS)</sub>   | Current through enabled LEDx pins during soft start                                                                    |   | -    | 2.6               | -    | mA              |

| Soft Start Timeout             | t <sub>TO(SS)</sub>    | The longest duration the boost is allowed to operate during soft start                                                 |   | -    | 131,072           | -    | Clock<br>Cycles |

| Thermal Shutdown Threshold     | T <sub>SHDN</sub>      | T <sub>J</sub> rising                                                                                                  |   | -    | 165               | -    | °C              |

| Thermal Shutdown Hysteresis    | T <sub>SHDN(hys)</sub> |                                                                                                                        |   | -    | 45                | -    | °C              |

| FAULT Pin                      |                        |                                                                                                                        |   |      |                   |      |                 |

| FAULT Pull-Down Voltage        | V <sub>FAULT</sub>     | Voltage on $\overline{\text{FAULT}}$ pin with fault enabled, 10 k $\Omega$ pull-up resistor, to 3.3 V                  | • | -    | _                 | 0.4  | V               |

| FAULT Pull-Down Resistance     | R <sub>FAULT</sub>     | Resistance between $\overline{\text{FAULT}}$ pin and ground with fault enabled, $I_{\text{FAULT}}$ = 100 $\mu\text{A}$ |   | _    | 77                | -    | Ω               |

$<sup>^{1}</sup>$ Specifications over the range  $T_A$  = -40°C to 105°C; guaranteed by design and characterization.

$<sup>^2</sup>$ Typical values are at  $T_A = 25$ °C.

$<sup>^3</sup>$ LED accuracy is defined as  $100 \times (I_{SET} \times 320 - I_{LED(av)}) / (I_{SET} \times 320)$ ,  $I_{LED(av)}$  measured as the average of  $I_{LED1}$  through  $I_{LED6}$ .  $^4$ LED current matching is defined as  $(I_{LEDx} - I_{LED(av)}) / I_{LED(av)}$ , with  $I_{LED(av)}$  as defined in footnote 3.

## **Characteristic Performance**

High Efficiency Boost Converter

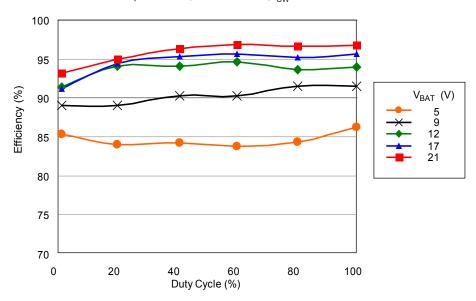

### **PWM Efficiency**

at Various Input Voltage Levels ( $V_{BAT}$ )  $V_{IN}$  = 5 V, six channels with 9 series LEDs each, 20 mA per channel, PWM = 200 Hz,  $f_{SW}$  = 1.5 MHz

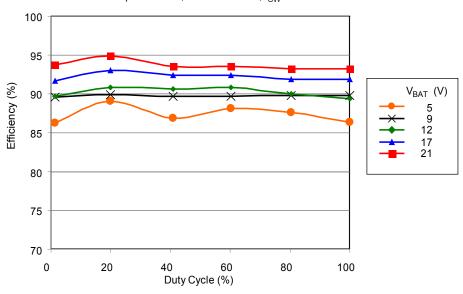

## **PWM Efficiency**

at Various Input Voltage Levels ( $V_{BAT}$ )  $V_{IN}$  = 5 V, six channels with 9 series LEDs each, 20 mA per channel, PWM = 200 Hz,  $f_{SW}$  = 980 kHz

## **Characteristic Performance**

High Efficiency Boost Converter

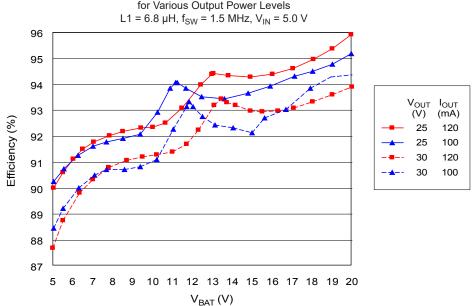

## Efficiency (P<sub>OUT</sub>/P<sub>BAT</sub>) versus Battery Supply Voltage for Various Output Power Levels

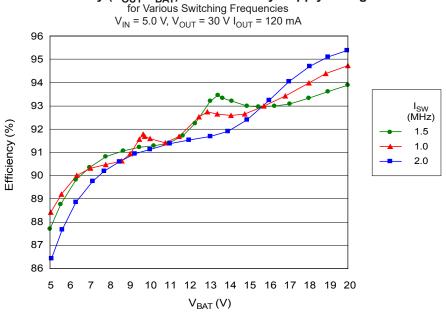

## Efficiency (P<sub>OUT</sub>/P<sub>BAT</sub>) versus Battery Supply Voltage

## **Characteristic Performance**

$I_{\text{OUT}}$

200 µs

## **Characteristic Performance**

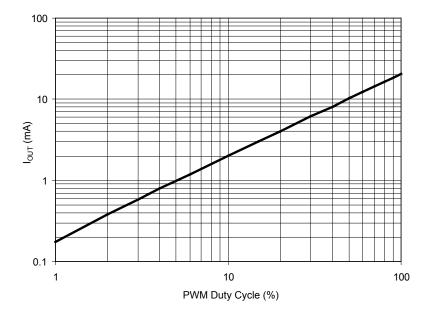

Average LED Current a Various PWM Duty Cycles  $V_{IN}$  = 5.0 V,  $V_{BAT}$  = 12 V, PWM = 200 Hz, Output = six LED channels with 10 series LEDs each

## **Functional Description**

The A8503 is a multi-output WLED/RGB LED driver for backlighting medium-size displays. It has an integrated boost converter to increase input supply voltage, allowing it to drive up to 12 LEDs per channel on 6 channels with a  $V_f(max)$  of 3.2 V at 20 mA per LED, at 5 V supply. The boost converter is a fixed frequency current-mode converter. The switching frequency can be set in a range from 600 kHz to 2 MHz, by an external resistor,  $R_{FSET}$ , connected between FSET and ground. The integrated boost DMOS switch is rated for 55 V, 2 A. This switch is protected against overvoltage, and has pulse-by-pulse current limiting. The current limiting is independent of duty cycle.

The A8503 has six well-matched current sinks that provide regulated current through the LEDs, for uniform display brightness. The boost converter is controlled by monitoring all LEDx pins simultaneously and continuously. All LED sinks are rated for 34 V to allow PWM dimming control.

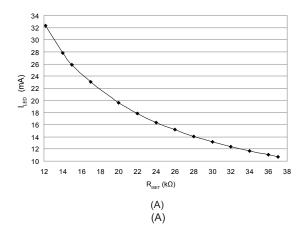

### **LED Current Setting**

The maximum LED current can be set, to 32 mA/channel, through the ISET pin. Connect a resistor,  $R_{\rm ISET}$ , between this pin and ground to set the reference current level,  $I_{\rm SET}$ . The value of  $I_{\rm SET}$  (mA) is determined by:

$$I_{SET} = 1.235 / R_{ISET} (k\Omega)$$

.

The resulting current is multiplied internally by a gain of 320, then is mirrored to all enabled LEDx pins. This sets the maximum current through LEDx, referred as the 100% Current, as shown in figure 2A. The LEDx current can be reduced from the 100% Current value by applying an external PWM signal on the PWM pin (see figure 2B).

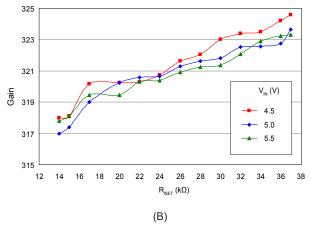

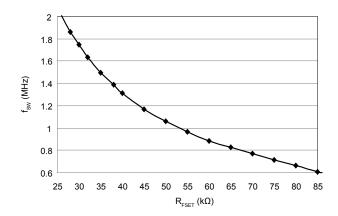

### **Boost Switching Frequency Setting**

Connect an external resistor between the FSET pin and AGND, to set boost switching frequency,  $f_{SW}$ . The value of the boost switching frequency,  $f_{SW}$  (MHz), is determined by:

$$f_{SW} = 52 / R_{FSET} (k\Omega)$$

.

The typical R<sub>FSET</sub> versus frequency curve is shown in figure 3.

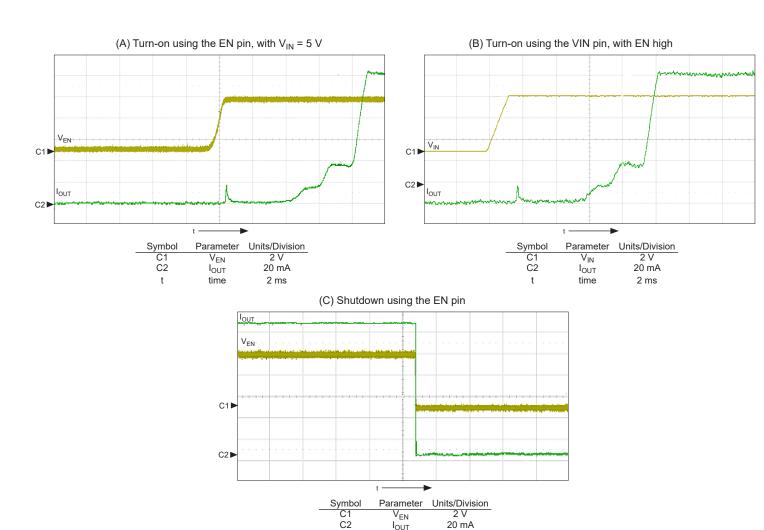

#### **Enable**

The IC turns on when a high signal is applied on the EN pin and turns off when this pin is pulled low.

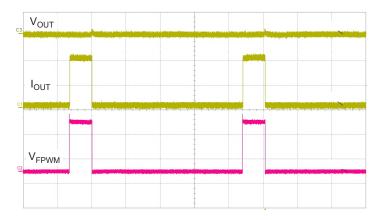

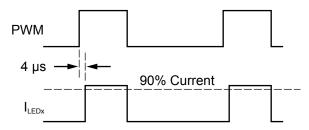

### **PWM Dimming**

The A8503 has a very wide range of PWM signal input. It can accept a PWM signal from 100 Hz to 5 kHz. When a PWM high signal is applied, the LEDx pins sink 100% Current. When the

Figure 2. Effect of value of  $R_{\rm ISET}$  on current through an LED string. Panel A shows level of 100% current, and panel B shows LEDx gain.

Figure 3. Switching frequency setting versus  $R_{FSET}$  ( $V_{IN}$  = 5 V,  $V_{BAT}$  = 12 V).

PWM signal is low, the LED sinks turn off. Referring to figure 5, there is a 4  $\mu$ s ramp-up delay between when the PWM signal is applied and when the current reaches the 90% level. Increase the applied PWM pulse-width by 3  $\mu$ s to compensate for this delay.

### **Startup Sequence**

When EN is pulled high, the IC enters soft start. The IC first tries to determine which LEDx pins are being used, by raising the LEDx pin voltage with a small current. After a duration of 512 switching cycles, the LEDx pin voltage is checked. Any LEDx channel with a drain voltage smaller then 100 mV is removed from the control loop.

After the first PWM positive trigger, the boost current is limited to 0.4 A and all active LEDx pins sink  $^{1}\!/_{12}$  of the set current until output voltage reaches sufficient regulation level. When the device comes out of soft start, boost current and the LEDx pin currents are set to normal operating level. Within a few cycles, the output capacitor charges to the voltage required to supply full LEDx current. After  $V_{OUT}$  reaches the required level, LEDx current toggles between 0% and 100% with each PWM command signal.

In case of a heavy overload on output voltage at startup, the device may stay in soft start mode indefinitely, if the output voltage cannot rise to the LED regulation level and the MODE pin is tied high. To avoid this scenario, A8503 has a soft start timeout when the MODE pin is tied low. With the MODE pin low, if the device does not finish soft start during 131,072 switching cycles, it is shut down.

### **LED Open and Short Detect**

All unused LED pins should be connected to ground to prevent any undesired faults from triggering. For LED short detect, any enabled LEDx pins that have a voltage exceeding the short circuit detect voltage,  $V_{SC}$ , causes the device to shut down irrespective of what mode the A8503 is in. The open LED fault will be triggered as soon as an enabled LEDx pin does not have sufficient current flowing through it to stay in regulation. This will result in increased output voltage until the LED is back in regulation or overvoltage protection (OVP) is tripped. If OVP is tripped, depending on the mode of operation, the A8503 will either shut down (MODE = low) or will remove the LED string from operation and continue to operate normally (MODE = high). Please refer to the Fault Mode table for latched and non-latched fault conditions.

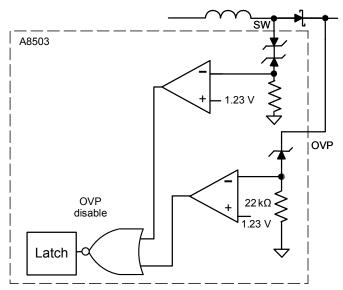

#### **Overvoltage Protection**

The A8503 has two independent overvoltage protection features to protect the device against output overvoltage. The overvoltage level can be set, from 44 to 50 V typical, with an external resistor, ROVP. When the current though the OVP pin exceeds 240  $\mu A,$

the OVP comparator goes high and the device shuts down in an OVP fault state when the MODE pin is low. If the MODE pin is high, the OVP fault disables all LEDx strings that are below regulation, thus preventing them from controlling the boost output voltage.

The device also offers open Schottky diode protection. If for any reason the voltage on the SW pins exceeds more than 57 V, the IC shuts down and remains latched irrespective of the MODE pin level. The overvoltage protection circuit is shown in figure 6.

Calculate the value for  $R_{OVP}$  as follows:

$$R_{\text{OVP}} = (V_{\text{OVP}} - 44) / 240 \,\mu\text{A}$$

,

where  $V_{OVP}$  is the desired typical OVP level in V, and  $R_{OVP}$  is in  $\Omega$ .

#### **Overcurrent Protection**

The IC provides pulse-by-pulse current limiting at 2.7 A for the boost MOSFET. If the overcurrent fault state persists, the boost control loop will force the compensating capacitor to rise in voltage until it reaches the overcurrent fault level. This fault shuts down the IC and is latched when MODE pin is low (MODE = AGND). If MODE pin is high, the overcurrent fault forces the device into soft start.

Figure 4. PWM Pin Dimming,  $f_{PWM}$  = 200 Hz, duty cycle = 10%. C1,  $I_{OUT}$  50 mA / div; ; C2,  $V_{FPWM}$  (signal on PWM pin) 2 V / div; C3,  $V_{OUT}$  5 V / div, AC coupled.

Figure 5. I<sub>LEDx</sub> versus PWM input

### **Input UVLO**

The device is shut down when input voltage,  $V_{IN}$ , falls below  $V_{UVLO}$ .

## **Thermal Shutdown Protection (TSD)**

The device shuts down when junction temperature exceeds 165°C. If the MODE pin is low, the thermal shutdown will latch the device off until EN is pulled low or UVLO is triggered. The

A8503 will recover automatically when the MODE pin is high and the junction temperature falls below 120°C.

### **Fault Mode**

The MODE pin controls the latching of faults as shown in the Fault Mode table. Latched faults are reset when EN is pulsed low or  $V_{\text{IN}}$  falls below UVLO level.

Figure 6. Overvoltage protection circuitry

## **Fault Mode Table**

| Protection                         | MODE =<br>AGND | MODE =       | Description                                                                                                                                                                                                                                                                                                                  |

|------------------------------------|----------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overvoltage Protection             | Latched        | Auto-restart | Fault occurs when OVP pin exceeds V <sub>OVP</sub> threshold. Used to protect the output voltage from damaging the part.                                                                                                                                                                                                     |

| Open Diode Protection              | Latched        | Latched      | Fault occurs when SW node exceeds the safe operating voltage of the boost DMOS switch. Typical value is 57 V.                                                                                                                                                                                                                |

| Pulse-by-Pulse Current<br>Limiting | Auto-restart   | Auto-restart | Fault occurs when the current through the DMOS switch exceeds I <sub>SWLIM</sub> , 2.7 A typical. The DMOS switch is turned off on a cycle-by-cycle basis.                                                                                                                                                                   |

| Overcurrent Protection             | Latched        | Auto-restart | Fault occurs when the COMP pin exceeds the overcurrent detect threshold. Multiple pulse-by-pulse current limits will cause the COMP pin voltage to rise. After a time period determined by the COMP current and the compensation capacitor, the COMP voltage will exceed the overcurrent detect threshold and force a fault. |

| Overtemperature<br>Protection      | Latched        | Auto-restart | Fault occurs when the die temperature exceeds the overtemperature threshold, 165°C typical.                                                                                                                                                                                                                                  |

| Shorted LED Protection             | Latched        | Latched      | Fault occurs when the LEDx pin voltage exceeds V <sub>SC</sub> , 18.7 V typical.                                                                                                                                                                                                                                             |

| V <sub>IN</sub> UVLO               | No             | No           | Fault occurs when $V_{\text{IN}}$ drops below $V_{\text{UVLO}}$ , 4.0 V typical. This fault resets all latched faults.                                                                                                                                                                                                       |

| Soft Start Timeout                 | Latched        | Auto-restart | Fault occurs if the IC is unable to finish soft start within approximately 131,000 clock cycles (approximately 74 ms at 1.73 MHz) after EN is set high.                                                                                                                                                                      |

## **Application Information**

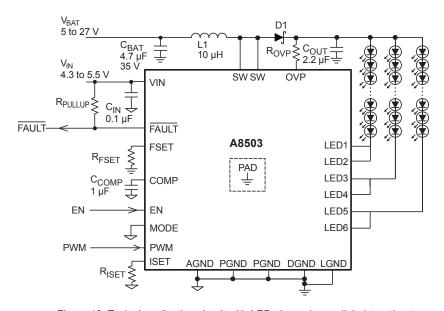

A typical application circuit for dimming an LCD monitor backlight with 72 LEDs is shown in figure 1. Figure 7 shows two dimming methods: digital PWM control (PWM signal on the PWM pin) and analog PWM control, with the analog signal,  $V_{\rm A}$ , applied to the ISET pin through a resistor,  $R_{\rm A}$ .

The current flowing through R<sub>A</sub> can be calculated as:

$$I_{A} = (V_{A} - V_{SET}) / R_{A}$$

.

This current changes the reference current, I<sub>SET</sub>, as follows:

$$I_{\text{SET}} = V_{\text{SET}} / R_{\text{SET}} - (V_{\text{A}} - V_{\text{SET}}) / R_{\text{A}}.$$

LED current can be changed by changing  $V_A$ . ISET can be changed in the range from 33 to 100  $\mu A$ .

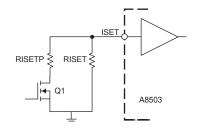

### **Application Circuit for 1000:1 Dimming Level**

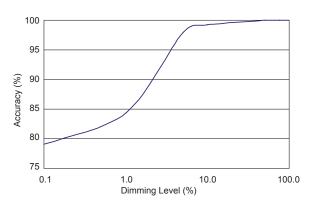

A wider dimming range can be achieved by changing the reference current,  $\rm I_{SET}$ , while using PWM dimming. For higher output, current levels turn on Q1 (see figure 8).  $\rm R_{ISET}$  and  $\rm R_{ISETP}$  set the 100% current level. This current level can be set up to 32 mA, and then it can be dimmed by applying 100% to 0.33% duty cycle on the PWM pin. The reference current can be reduced by turning off Q1. LED current can be dimmed to 10 mA by reducing reference current through the ISET pin. This provides a 1000:1 combined dimming level range. Figure 9 shows the accuracy,  $\rm Err_{LEDX}$ , that results using this circuit.

Figure 8. Configuration for 1000:1 dimming.

Figure 9. Typical accuracy, normalized to the 100% current level, versus dimming level, with  $F_{PWM}$  = 100 Hz.

Figure 7. Typical application circuit for analog dimming with external DC voltage source  $V_A$ . This method of dimming can be combined with digital PWM dimming.

Figure 10. Typical application circuit with LED channels paralleled together to achieve higher LED current (up to 64 mA per string).

Figure 11. Typical application circuit for LED modules with ESD capacitors with values up to 10 nF.

# High Efficiency 6-Channel, 2 MHz, WLED/RGB Driver for Medium Displays, with Integrated 55 V Power Switch

**Recommended Components Table**

| Component           | Rating                               | Part Number         | Source                  |  |

|---------------------|--------------------------------------|---------------------|-------------------------|--|

| C <sub>BAT</sub>    | 4.7 μF / 35 V, X5R ceramic capacitor | GMK316F475ZG-T      | Taiyo Yuden             |  |

| C <sub>COMP</sub>   | 1 μF / 10 V                          |                     |                         |  |

| C <sub>IN</sub>     | 0.1 μF / 10 V                        |                     |                         |  |

| C <sub>OUT</sub>    | 2.2 μF / 50 V, X7R                   | GRM31CR71H225KA88L  | Murata                  |  |

| D1                  | Schottky diode 60 V, 1.5 A           | 10MQ060NTRPBF       | International Rectifier |  |

| R <sub>FSET</sub>   | 34 kΩ, 1%                            |                     |                         |  |

| R <sub>ISET</sub>   | 19.6 kΩ, 1% (for 20 mA LED current)  |                     |                         |  |

| R <sub>OVP</sub>    | 10 kΩ                                |                     |                         |  |

| R <sub>PULLUP</sub> | 10 kΩ                                |                     |                         |  |

| L1                  | 10 μH, 1.3 A                         | SLF6028T-100M1R3-PF | TDK                     |  |

| Alternate inductors | 6.8 μH, 1.3 A                        | D53LC A915AY-6R8M   | Toko                    |  |

|                     | 4.7 μH, 1.6 A                        | NP04SZB 4R7N        | Taiyo Yuden             |  |

## Package EC, 26-contact QFN

Copyright 2019, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website: www.allegromicro.com