## 8-CHANNEL SATURATED SINK DRIVER

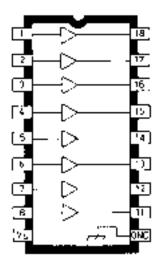

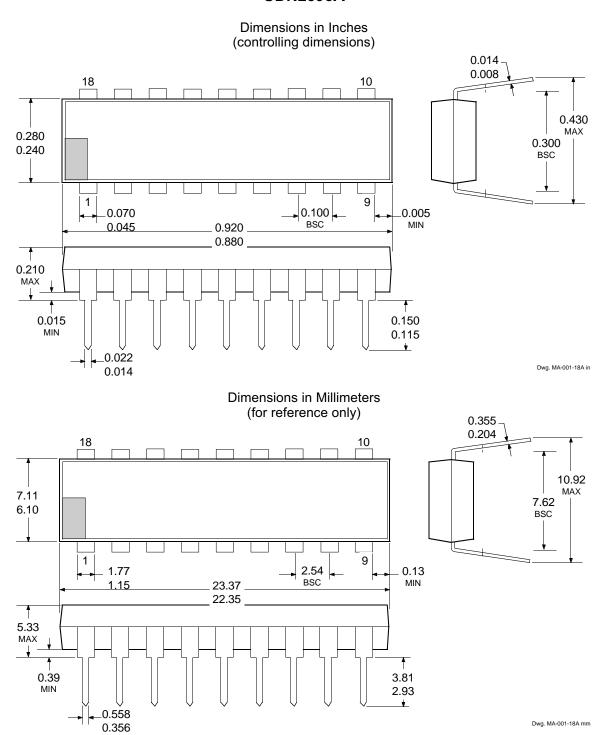

**UDN2595A** (DIP)

Dwg. No. A-11,407

#### **ABSOLUTE MAXIMUM RATINGS**

at 25°C Free-Air Temperature for any one driver (unless otherwise noted)

| Output Voltage, V <sub>CE</sub>                     |

|-----------------------------------------------------|

| Supply Voltage, V <sub>S</sub> 20 V                 |

| Input Voltage, V <sub>IN</sub> 20 V                 |

| Output Current, l <sub>C</sub> 200 mA               |

| Ground Terminal Current, I <sub>GND</sub> 1.6 A     |

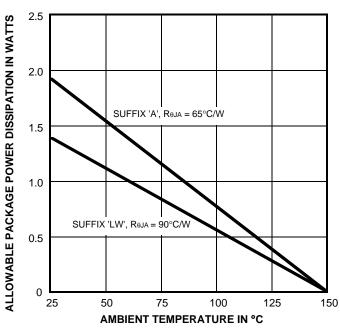

| Package Power Dissipation, P <sub>D</sub> See Graph |

| Operating Temperature Range, $T_A$ 20°C to +85°C    |

| Storage Temperature Range, To                       |

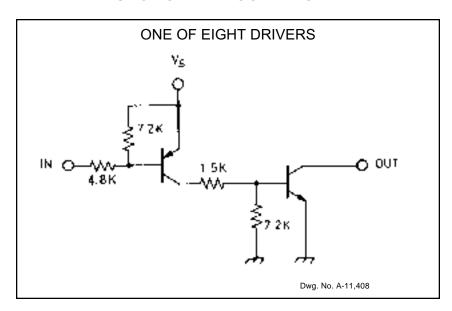

Developed for use with low-voltage LED and incandescent displays requiring low output saturation voltage, the UDN2595A and A2595SLW meet many interface needs, including those exceeding the capabilities of standard logic buffers. The eight non-Darlington outputs of each driver can continuously and simultaneously sink load currents of 100 mA at ambient temperatures of up to +75°C.

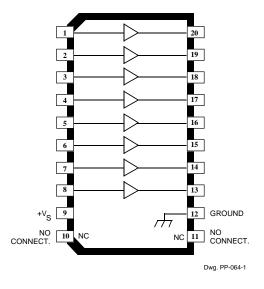

The eight-channel driver's active-low inputs can be driven directly from TTL, Schottky TTL, DTL, 5 to 16 V CMOS, and NMOS logic. All input connections are on one side of the package, output connections on the other, for simplified printed wiring board layouts.

These drivers are packaged in plastic DIPs (suffix A) or surface-mountable wide-body SOICs (suffix LW), and are rated for operation over the temperature range of -20°C to +85°C. The A2595SLW is also available for operation to -40°C. To order, change the suffix from 'SLW' to 'ELW'.

## **FEATURES**

- Non-Inverting Function

(Input Low = Output ON)

- 200 mA Current Rating

- 100 mA Continuous and Simultaneous (All outputs) to +85°C

- Low Saturation Voltage

- TTL, CMOS, NMOS Compatible

- Efficient Input/Output Pin Format

- DIP or SOIC Packaging

Always order by complete part number:

| Part Number | Package                |

|-------------|------------------------|

| UDN2595A    | 18-Pin DIP             |

| A2595SLW    | 20-Lead Wide-Body SOIC |

### **FUNCTIONAL BLOCK DIAGRAM**

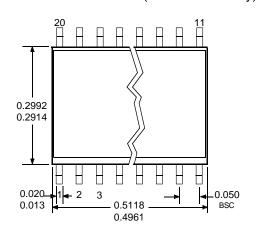

## A2595SLW (SOIC)

Dwg. GS-009-1B

## ELECTRICAL CHARACTERISTICS at $T_A = +25^{\circ}C$ , $V_S = 5.0 \text{ V}$ (unless otherwise noted).

|                           |                      |                                                                           | Limits |      |       |

|---------------------------|----------------------|---------------------------------------------------------------------------|--------|------|-------|

| Characteristic            | Symbol               | Test Conditions                                                           | Min.   | Max. | Units |

| Output Leakage<br>Current | I <sub>CEX</sub>     | V <sub>IN</sub> ≥ 4.5 V, V <sub>OUT</sub> = 20 V, T <sub>A</sub> = 25°C   | _      | 50   | μΑ    |

|                           |                      | V <sub>IN</sub> ≥ 4.6 V, V <sub>OUT</sub> = 20 V, T <sub>A</sub> = 70°C   | _      | 100  | μΑ    |

| Output Saturation         | V <sub>CE(SAT)</sub> | V <sub>IN</sub> = 0.4 V, I <sub>OUT</sub> = 50 mA                         | _      | 0.5  | V     |

| Voltage                   |                      | V <sub>IN</sub> = 0.4 V, I <sub>OUT</sub> = 100 mA                        | _      | 0.6  | V     |

| Input Current             | I <sub>IN(ON)</sub>  | V <sub>IN</sub> = 0.4 V, I <sub>OUT</sub> = 100 mA                        | _      | -1.6 | mA    |

|                           |                      | $V_{IN}$ = 0.4 V, $I_{OUT}$ = 100 mA, $V_{S}$ = 15 V                      | _      | -5.0 | mA    |

| Input Voltage             | V <sub>IN(ON)</sub>  | I <sub>OUT</sub> = 100 mA, V <sub>OUT</sub> ≤ 0.6 V                       | _      | 0.4  | ٧     |

|                           | V <sub>IN(OFF)</sub> | I <sub>OUT</sub> = 100 μA, T <sub>A</sub> = 70°C                          | 4.6    | _    | V     |

| Input Capacitance         | C <sub>IN</sub>      |                                                                           | _      | 25   | pF    |

| Supply Current            | I <sub>S</sub>       | V <sub>IN</sub> = 0.4 V, I <sub>OUT</sub> = 100 mA                        | _      | 6.0  | mA    |

|                           |                      | V <sub>IN</sub> = 0.4 V, I <sub>OUT</sub> = 100 mA, V <sub>S</sub> = 15 V | _      | 20   | mA    |

NOTES: 1. Negative current is defined as coming out of the specified device pin.

2. The  $V_{IN(ON)}$  voltage limit guarantees a minimum output sink current per the specified conditions.

3. l<sub>S</sub> is measured with any one of eight drivers turned ON.

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

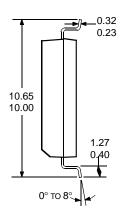

### **UDN2595A**

- NOTES: 1. Exact body and lead configuration at vendor's option within limits shown.

- 2. Lead spacing tolerance is non-cumulative.

- 3. Lead thickness is measured at seating plane or below.

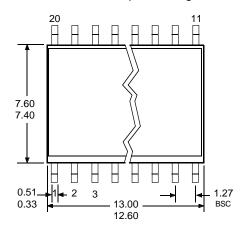

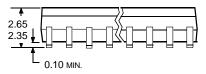

## **A2595SLW**

# Dimensions in Inches (for reference only)

Dwg. MA-008-20 in

## Dimensions in Millimeters (controlling dimensions)

Dwg. MA-008-20 mm

NOTES: 1. Exact body and lead configuration at vendor's option within limits shown.

2. Lead spacing tolerance is non-cumulative.