# **COMPLEMENTARY-OUTPUTS** HALL-EFFECT LATCH

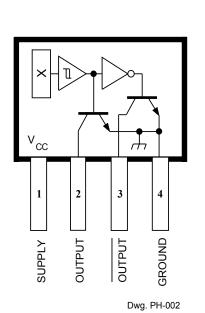

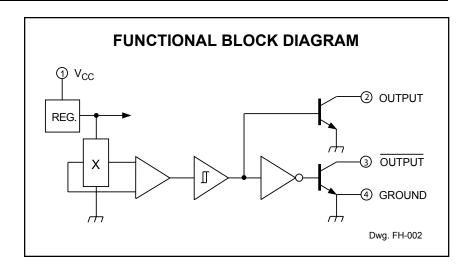

Type UGN3275K latching Hall-effect sensor ICs are bipolar integrated circuits designed for electronic commutation of brushless dc motors. They feature dual complementary outputs. The latches are typically used to sense matched magnetic flux densities of alternating polarity from multipole ring magnets.

Each sensor IC includes a Hall voltage generator, operational amplifier, Schmitt trigger, voltage regulator, and dual bipolar output transistors. The regulator allows use of the integrated circuit with supply voltages of 4.5 V to 24 V.

If the Hall cell is exposed to a magnetic flux density greater than the operate threshold (B<sub>OP</sub>), OUTPUT goes low (turns on) and OUTPUT goes high (turns off). The outputs will hold (latch) this state until magnetic field reversal exposes the Hall cell to a magnetic flux density below the release threshold (BRP) when OUTPUT will go high (off) and OUTPUT will go low (on). This state is also latched. Under any condition one output is on while the other is off. Because the operating state switches only with magnetic field reversal, and not merely with a change in the strength, these integrated circuits qualify as true Hall-effect latches.

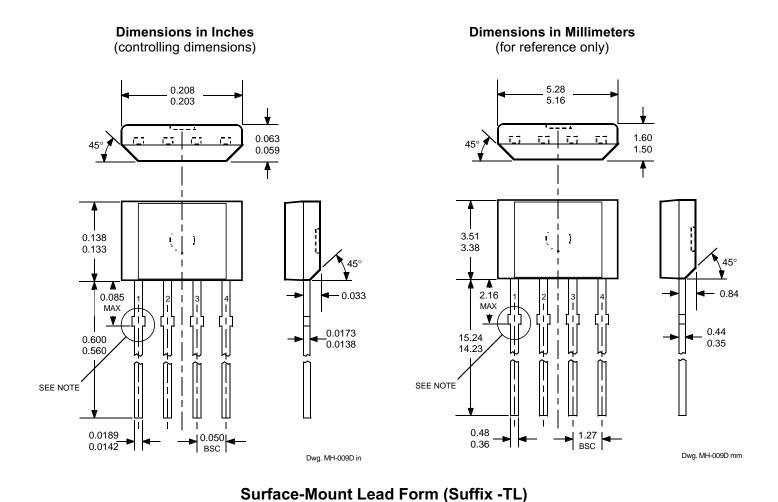

These complementary-output Hall-effect latches are supplied in a four-pin plastic SIP, 0.200" (5.08 mm) wide, 0.130" (3.3 mm) high, and 0.060" (1.54 mm) thick.

Pinning is shown viewed from branded side.

#### **ABSOLUTE MAXIMUM RATINGS**

| Power Supply, V <sub>CC</sub> 25 V               |

|--------------------------------------------------|

| Magnetic Flux Density, B Unlimited               |

| Output OFF Voltage, V <sub>OUT</sub> 25 V        |

| Output ON Current, I <sub>OUT</sub> <b>50 mA</b> |

| Operating Temperature Range,                     |

| T <sub>A</sub> 20°C to +85°C                     |

| Storage Temperature Range,                       |

| T <sub>S</sub> 65°C to +150°C                    |

#### **FEATURES**

- Operable with Multipole Ring Magnets

- High Reliability

- Small Size

- Output Compatible with All Digital Logic Families

- 4.5 V to 24 V Operation

- High Hysteresis Level Minimizes Stray-Field Problems

- Complementary Outputs

Always order by complete part number: | UGN3275K |.

## 3275 COMPLEMENTARY-OUTPUTS HALL-EFFECT LATCH

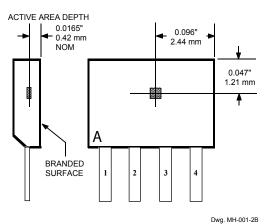

#### **ELEMENT LOCATION**

# ELECTRICAL CHARACTERISTICS at T $_{\rm A}$ = +25 $^{\circ}$ C, V $_{\rm CC}$ = 4.5 V to 24 V (unless otherwise noted).

| Characteristic            | Symbol                | Test Conditions                                       | Min. | Тур. | Max. | Units |

|---------------------------|-----------------------|-------------------------------------------------------|------|------|------|-------|

| Supply Voltage            | V <sub>CC</sub>       | Operating                                             | 4.5  | _    | 24   | V     |

| Output Saturation Voltage | V <sub>OUT(SAT)</sub> | $V_{CC}$ = 4.5 V, $I_{OUT}$ = 20 mA, B > $B_{OP}$     | _    |      | 400  | mV    |

| Output Leakage Current    | I <sub>OFF</sub>      | $V_{OUT}$ = 24 V, $V_{CC}$ = 24 V, B < $B_{RP}$       | _    | _    | 10   | μΑ    |

| Supply Current            | I <sub>cc</sub>       | V <sub>CC</sub> = 24 V, B < B <sub>RP</sub>           | _    | _    | 7.0  | mA    |

| Output Rise Time          | t <sub>r</sub>        | $V_{CC}$ = 12 V, $R_L$ = 820 $\Omega$ , $C_L$ = 20 pF | _    | 0.04 | 0.4  | μs    |

| Output Fall Time          | t <sub>f</sub>        | $V_{CC}$ = 12 V, $R_L$ = 820 $\Omega$ , $C_L$ = 20 pF | _    | 0.18 | 0.4  | μs    |

#### **MAGNETIC CHARACTERISTICS**

|                |                  | T <sub>A</sub> = +25°C |      | T <sub>A</sub> = -20°C 1 |      |       |

|----------------|------------------|------------------------|------|--------------------------|------|-------|

| Characteristic | Symbol           | Min.                   | Max. | Min.                     | Max. | Units |

| Operate Point  | B <sub>OP</sub>  | 25                     | 250  | 15                       | 250  | G     |

| Release Point  | B <sub>RP</sub>  | -250                   | -25  | -250                     | -15  | G     |

| Hysteresis     | B <sub>hys</sub> | 100                    | _    | 100                      | _    | G     |

NOTES: 1. As used here, negative flux densities are defined as less than zero (algebraic convention).

2. 1 gauss (G) is exactly equal to 0.1 millitesla (mT).

2.41 ±0.13

0.051 MAX

NOTES: 1. Tolerances on package height and width represent allowable mold offsets. Dimensions given are measured at the widest point (parting line).

- 2. Exact body and lead configuration at vendor's option within limits shown.

- 3. Height does not include mold gate flash.

0.095 ±0.005

- 4. Recommended minimum PWB hole diameter to clear transition area is 0.035" (0.89 mm).

- 5. Where no tolerance is specified, dimension is nominal.

- 6. Supplied in bulk pack (500 pieces per bag).

# 3275 COMPLEMENTARY-OUTPUTS HALL-EFFECT LATCH

### HALL-EFFECT SENSOR ICS

|                                                   |                                   | LATCHI                                 | NG HALL-EFFEC                  | T DIGITA       | L SWITCHES |                             |

|---------------------------------------------------|-----------------------------------|----------------------------------------|--------------------------------|----------------|------------|-----------------------------|

| Partial<br>Part<br>Number                         | Operate<br>Point (G)<br>Over Oper | Release<br>Point (G)<br>. Voltage & Te | Hysteresis<br>(G)<br>mp. Range | Oper.<br>Temp. | Packages   | Replaces<br>and<br>Comments |

| UGN3175                                           | 15 to 180                         | -180 to -15                            | >80 (Typ 180)                  | S              | LT, UA     |                             |

| UGN3177                                           | 25 to 150                         | -150 to -25                            | >50 (Typ 180)                  | S              | LT, UA     |                             |

| A3185x                                            | 140 to 300                        | -300 to -140                           | 280 to 600                     | E/L            | LT, UA     |                             |

| A3187x                                            | 50 to 175                         | -175 to -50                            | 100 to 350                     | E/L            | LT, UA     | 3077, 3175, 3177            |

| A3188x                                            | 80 to 200                         | -200 to -80                            | 160 to 400                     | E/L            | LT, UA     |                             |

| A3189x                                            | 50 to 250                         | -250 to -50                            | 100 to 500                     | E/L            | LT, UA     | 3075, 3076                  |

| A3280x                                            | 5 to 40                           | -40 to -5                              | 10 to 80                       | E/L            | LH, LT, UA | chopper stabilized          |

| A3281x                                            | 15 to 90                          | -90 to -15                             | 30 to 180                      | E/L            | LH, LT, UA | chopper stabilized          |

| A3283x                                            | 100 to 180                        | -180 to -100                           | <400 (Typ 300)                 | E/L            | LH, LT, UA | chopper stabilized          |

| "PROTECTED" LATCHING HALL-EFFECT DIGITAL SWITCHES |                                   |                                        |                                |                |            |                             |

| Partial                                           | Operate                           | Release                                | Hysteresis                     | _              |            |                             |

| Part                                              | Point (G)                         | Point (G)                              | (G)                            | Oper.          | Daalaanaa  | 0                           |

| Number                                            | Over Oper                         | . Voltage & Te                         | mp. Kange                      | Temp.          | Packages   | Comments                    |

| A3195x                                            | 40 to 200                         | -200 to -40                            | >110 (Typ 220)                 | E, L           | U, LT      | active pulldown             |

| A3197x                                            | 40 to 200                         | -200 to -40                            | >110 (Typ 230)                 | E, L           | U, LT      | open-collector output       |

Notes: 1) Typical data is at  $T_A = +25^{\circ}C$  and nominal operating voltage.

2) "x" = Operating Temperature Range [suffix letter or (prefix)]: S (UGN) = -20°C to +85°C, E = -40°C to +85°C, J = -40°C to +115°C, K (UGS) = -40°C to +125°C, L (UGL) = -40°C to +150°C.

The products described herein are manufactured under one or more of the following U.S. patents: 5,045,920; 5,264,783; 5,442,283; 5,389,889; 5,581,179; 5,517,112; 5,619,137; 5,621,319; 5,650,719; 5,686,894; 5,694,038; 5,729,130; 5,917,320; and other patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro products are not authorized for use as critical components in life-support appliances, devices, or systems without express written approval.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties that may result from its use.