# Device Comparisons of A3953 and A4973

The Allegro® A4973 is intended as the "next generation" A3953. The most notable design upgrade is the transition from bipolar to DMOS technology. DMOS offers smaller geometries, higher power densities and better switching performance than bipolar technologies.

As a result of these upgrades some parameters have changed which may require BOM changes. In most applications only the sense resistor and REF voltage need to be changed. For customers who are using the A3953 and must convert to the A4973 this document shows what changes need to be made to existing circuits in order to use the new device in a similar way.

The data shown here is for reference only. Refer to the datasheets of the individual devices for parameters and detailed functional descriptions. If data in this document does not match the associated device datasheet, then please be aware that the datasheet is the governing specification document in all cases.

Package B, 16-pin DIP with exposed tabs

Package LB, 16-pin SOIC with internally fused pins

Figure 1. Both the A4973 and the A3953 are provided in the 16-pin DIP (B) and 16-pin SOIC (LB) packages, shown here (not to scale).

### **Table of Contents**

| Functional Block Diagrams                   | 2 |

|---------------------------------------------|---|

| 3                                           |   |

| Absolute Maximum Ratings                    | 3 |

| V <sub>SENSE</sub> Range                    | 3 |

| V <sub>BB</sub> Range                       | 3 |

| Reference Voltage and Current Regulation    | 3 |

| V <sub>REF</sub> Range                      | 3 |

| R <sub>SENSE</sub> Selection                | 3 |

| V <sub>SAT</sub> versus R <sub>DS(on)</sub> | 3 |

| Voltage Drop                                | 4 |

| Supply Currents                             | 4 |

| Thermals                                    | 4 |

| Minimum Regulated Output Current            | 5 |

| Decay Modes and Brake                       | 5 |

| Brake Modes                                 | 5 |

| Input Logic Levels                          | 5 |

# **Functional Block Diagrams**

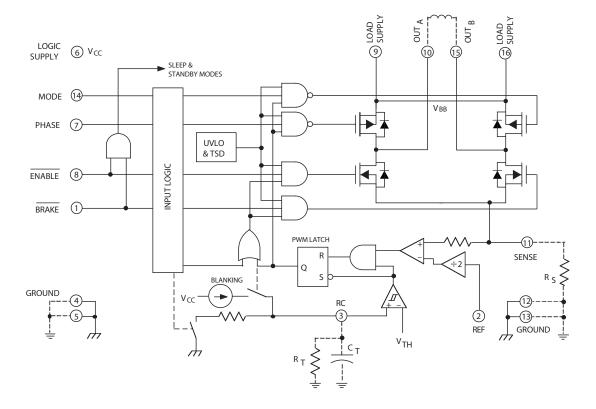

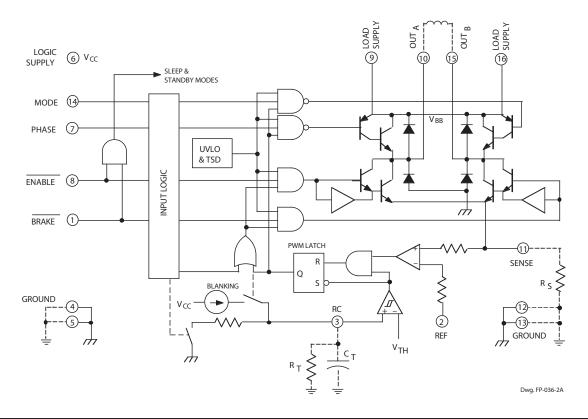

## A4973

#### A3953

## **Absolute Maximum Ratings**

Some of the absolute maximum ratings have changed from the A3953 to the A4973. The differences are shown in table 1.

## **V<sub>SENSE</sub>** Range

The absolute maximum voltage on the SENSE pin has been reduced from 1 V ( $V_{CC} = 5$  V) for the A3953 down to 500 mV for the A4973. This makes it necessary for some customers to reduce the size of the current sensing resistor,  $R_{SENSE}$ , so that under maximum load current the voltage on the SENSE pin does not exceed 500 mV.

# V<sub>BB</sub> Range

The A3953 was capable of operating down to  $V_{BB}$  equal to the logic input minimum of 3V. Due to the DMOS gate thresholds on the A4973, the supply must be at least 5 V (see table 2). At  $V_{BB}$  < 8 V the output on-resistance will be higher than specified (see table 3).

## **Reference Voltage and Current Regulation**

Current regulation is controlled via the voltage on the REF pin and the selected sense resistor. The A3953 did not have a divider. The A4973 has a divider (divide by 2) before the reference voltage is compared to the voltage on the SENSE pin. When the sense voltage reaches the reference voltage level, the PWM latch is tripped.

## **V<sub>REF</sub> Range**

The addition of the internal reference divider on the A4973 requires a different voltage be applied to the REF input.

The new I<sub>TRIP</sub> formula is:

$$I_{TRIP} \approx V_{REF} / (2 \times R_{SENSE})$$

(1)

### R<sub>SENSE</sub> Selection

As noted above, the maximum allowable  $V_{SENSE}$  voltage is decreased from 1 V to 500 mV. When calculating the value for  $R_{SENSE}$  the upper limit is defined by the maximum load current and the maximum allowable sense voltage. For example, if 1 A load current is required, the largest sense resistor that can be used is calculated as:

$$R_{SENSE}$$

(max) = 500 (mV) / 1 (A) = 0.5 ( $\Omega$ ) (2)

This results in maximum sense resistor of  $0.5 \Omega$ . Picking a value slightly lower will provide a guard band for resistor tolerances.

# V<sub>SAT</sub> versus R<sub>DS(on)</sub>

One of the largest differences between the A3953 and the A4973 is the change from bipolar to DMOS topology. This results in significant improvements to die size. The A4973 bridge is made with a P-channel high side and an N-channel low side.

$R_{DS(on)}$  changes significantly with temperature, increasing as temperature rises. For every 100°C rise,  $R_{DS(on)}$  increases by a factor of 1.6 times. The A4973  $R_{DS(on)}$  is specified for  $V_{BB}$  down to 8 V. For  $V_{BB}$  less than 8 V,  $R_{DS(on)}$  will be higher (see table 3).

**Table 1. Absolute Maximum Ratings Comparison**

| Characteristic             | Symbol             | Notes                   | Rat   | l lmi4 |      |

|----------------------------|--------------------|-------------------------|-------|--------|------|

|                            |                    |                         | A4973 | A3953  | Unit |

| Sense Voltage              | V <sub>SENSE</sub> | V <sub>CC</sub> = 5.0 V | 0.5   | 1.0    | V    |

|                            |                    | V <sub>CC</sub> = 3.3 V | 0.5   | 0.4    | V    |

| Output Current, Continuous | I <sub>OUT</sub>   |                         | ±1.5  | ±1.3   | Α    |

Table 2. V<sub>BB</sub> Comparison

| Characteristic            | Symbol          | Test Conditions | Limit | Unit            |      |

|---------------------------|-----------------|-----------------|-------|-----------------|------|

|                           |                 |                 | A4973 | A3953           | Onit |

| Load Supply Voltage Range | V <sub>BB</sub> |                 | 5     | V <sub>CC</sub> | V    |

#### **Voltage Drop**

Bipolar devices are defined by  $V_{CE}$  but DMOS devices are defined by  $R_{DS(on)}$ . The voltage drop across the A4973 bridge is a function of current and the  $R_{DS(on)}$  at the specific junction temperature. In order to make the change from the A3953 to the A4973 as transparent as possible the  $R_{DS(on)}$  of the source plus sink drivers was selected to have similar voltage drops under similar load conditions. Tables 3 and 4 compare the A3953 bipolar bridge and the A4973 DMOS bridge.

Note that the voltage drop across the A4973 bridge at 1.5 A is 1.5 V. At first glance the performance appears better than the A3953 which would have the same voltage drop at 0.85 A output current. The difference is that the  $R_{DS(on)}$  in the A4973 increases with increasing temperature, resulting in a larger voltage drop at higher temperatures. Assuming an operating temperature rise of 100°C above ambient, the expected  $R_{DS(on)}$  would be 1.6  $\Omega$ , resulting in a total voltage drop of 2.4 V at 1.5 A. A total drop of 2.4 V at operating temperature is close to the 2.6 V drop across the A3953 at the same output current.

#### **Supply Currents**

The A3953 has bipolar output transistors, with base drive supplied by  $V_{CC}$ . The A4973 has MOS output transistors, with gate drive supplied by the load supply,  $V_{BB}$ . This change reduces the current required of the logic supply,  $V_{CC}$ , but increases the current required by  $V_{BB}$  to  $\approx$  480  $\mu A$ . The additional current required by  $V_{BB}$  is generally miniscule compared to the current drawn to drive the load.

#### **Thermals**

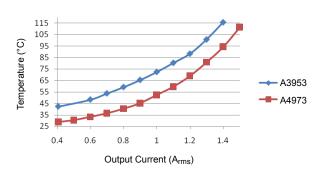

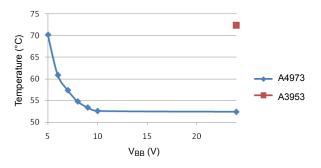

As stated previously, the A4973 utilizes MOS technology for the output transistors, as opposed to the bipolar transistors of the A3953. The A4973 was found to run cooler than the A3953 when both were run with  $V_{CC}$  = 5 V and  $V_{BB}$  = 24 V (see figure 2). The A4973 does run hotter as  $V_{BB}$  is reduced, but still runs cooler than the A3953 at 1 A output current (see figure 3).

Figure 2. Temperature versus Output Current

Figure 3. Temperature versus Load Supply Voltage

Table 3. A4973 Output Resistance (DMOS Bridge)

| Characteristic       | Symbol | Test Conditions                                                                                  | Limits |      |      | Unit |

|----------------------|--------|--------------------------------------------------------------------------------------------------|--------|------|------|------|

|                      |        | rest conditions                                                                                  | Min.   | Тур. | Max. | Unit |

| Output On Resistance |        | Total sink and source, I <sub>OUT</sub> = 1.5 A,<br>V <sub>BB</sub> > 8 V, T <sub>J</sub> = 25°C | _      | 1    | 1.4  | Ω    |

Table 4. A3953 Output Saturation (Bipolar Bridge)

| Characteristic            | Symbol               | Test Conditions                    | Limits |      |      | Unit |

|---------------------------|----------------------|------------------------------------|--------|------|------|------|

|                           |                      |                                    | Min.   | Тур. | Max. | Unit |

| Output Saturation Voltage | V <sub>CE(SAT)</sub> | Source, I <sub>OUT</sub> = -0.85 A | -      | 1.0  | 1.2  | V    |

|                           |                      | Source, I <sub>OUT</sub> = -1.5 A  | _      | 1.3  | 1.5  | V    |

|                           |                      | Sink, I <sub>OUT</sub> = 0.85 A    | -      | 0.5  | 0.6  | V    |

|                           |                      | Sink, I <sub>OUT</sub> = 1.5 A     | -      | 1.3  | 1.5  | V    |

## **Minimum Regulated Output Current**

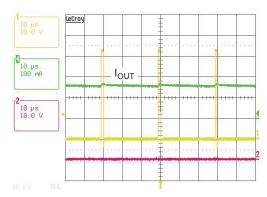

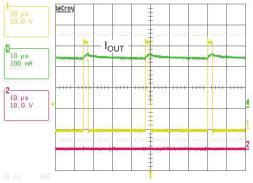

The minimum regulated output current is determined by grounding the reference input while driving a load. The current cannot get down to zero due to the blanking time. With RC values of 30 k $\Omega$  and 1000 pF, the A4973 is able to regulate to a lower current, 160 mA, than the A3953 can. The A3953 can only regulate down to 260 mA. See figures 4 and 5.

## **Decay Modes and Brake**

After the current has reached the  $I_{TRIP}$  value, the current will decay based on the fixed RC pin and MODE pin settings.

The A3953 has a MODE pin which enables or disables current control during braking. This feature actively limits the current recirculated in the sink drivers during the off-time.

The A4973 does not have the ability to measure the current while the current is decaying, because of the DMOS process structures: the body diodes of the DMOS will conduct the current. Therefore the MODE pin on the A4973 is used to select fast decay or slow decay during the fixed off-time cycle.

#### **Brake Modes**

The A3953 has two distinct brake modes. Mode high brake monitored the current and would PWM the brake to keep it from going over the peak current setting. Mode low brake offered no current control. The A4973 brake is equivalent to the mode low brake of the A3953. This mode requires the customer to ensure that the braking current does not exceed the absolute maximum current of the A4973 (1.5 A).

## Input Logic Levels

The A4973 uses CMOS type inputs with thresholds that vary with the logic supply voltage. The A3953 has TTL inputs. At higher logic supply voltages the logic high requirement may not be guaranteed. See table 5.

Figure 4. A4973 regulation of I<sub>OUT</sub> (green trace)

Figure 5. A3953 regulation regulation of I<sub>OUT</sub> (green trace)

Table 5. V<sub>IN</sub> Comparison

| Characteristic      | Symbol             | Test Conditions | Limits                    |                           |       |      |      |

|---------------------|--------------------|-----------------|---------------------------|---------------------------|-------|------|------|

|                     |                    |                 | A4973                     |                           | A3953 |      | Unit |

|                     |                    |                 | Min.                      | Max.                      | Min.  | Max. |      |

| Logic Input Voltage | V <sub>IN(1)</sub> |                 | V <sub>CC</sub> ×<br>0.55 | _                         | 2.0   | _    | V    |

|                     | $V_{IN(0)}$        |                 | _                         | V <sub>CC</sub> ×<br>0.27 | -     | 0.8  | V    |

Copyright ©2011, Allegro MicroSystems, Inc. Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current. Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website: www.allegromicro.com