## Shifting the Offset Voltage of Current Sensors

By Alex Latham, Systems Engineer Allegro MicroSystems

Most of the Allegro<sup>TM</sup> unidirectional current sensor ICs are trimmed such that the zero ampere output is at  $0.1 \times V_{CC}$ . The advantage of having the output voltage at  $0.1 \times V_{CC}$ is that the output can swing slightly lower than this value before saturating, allowing the user to measure zero ampere and slightly negative current. If Allegro were to attempt to trim the output to be zero volts at zero amperes, the

output driver of the part would saturate above zero volts, deteriorating the ability to measure currents very close to zero amperes. This application note documents a simple operational amplifier circuit which can be used to subtract out the  $0.1 \times V_{CC}$  offset of many of the Allegro current sensor ICs, as well as to shift the offset voltage to any required value.

## **Application Circuit**

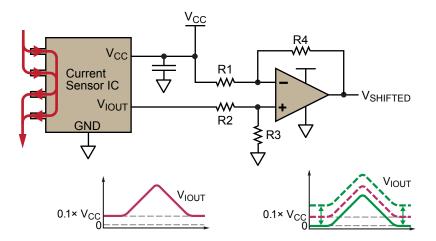

Figure 1 shows a simple differential op-amp circuit, which can be used to remove the offset from Allegro unidirectional current sensor ICs. The resistors must be chosen such that:

$$V_{\text{SHIFTED}} = V_{\text{IOUT}} - 0.1 \times V_{\text{CC}}$$

(1)

This example shows how to subtract the built-in offset of  $0.1 \times V_{CC}$  from the output of the IC. By choosing the correct resistor values, any fraction of  $V_{CC}$  can be subtracted from the output of the IC.

Figure 1. Current sensor with differential op-amp for removing the built-in offset of 0.1 ×  $V_{CC}$ . A summing amplifier can be used to increase the offset.

The equation describing the differential op-amp circuit is:

$$V_{\text{SHIFTED}} = \frac{(R4 + R1) R3}{(R3 + R2) R1} V_{\text{IOUT}} - \frac{R4}{R1} V_{\text{CC}}$$

(2)

Combining equations 1 and 2 means that:

$$\frac{R4}{R1} = 0.1$$

(3)

and

$$\frac{(R4+R1)R3}{(R3+R2)R1} = 1$$

(4)

Choosing values for R1 through R4 such that they satisfy equations 3 and 4 will result in the correct shift in the output of the sensor. Example values are:

•  $R1 = 100 \text{ k}\Omega$

- $R2 = 10 k\Omega$

- $R3 = 100 \text{ k}\Omega$

- $R4 = 10 k\Omega$

While this circuit configuration will subtract the inherent offset of the sensor IC, the output voltage,  $V_{SHIFTED}$ , will not be exactly zero volts at zero amps. This is due to the external op-amp saturating at some voltage higher than zero. Because of this, it is

important to use an op-amp which is as close as possible to being a true rail-to-rail op-amp or supply it with a sufficient negative supply instead of ground.

These types of op-amps are readily available and provide much better rail-to-rail performance than the output of most of the Allegro sensor ICs. This is due to the output stage of the Allegro sensor ICs being optimized to provide a highly linear analog output, proportional to the sensed current, rather than rail-to-rail capability.

## Lab Results

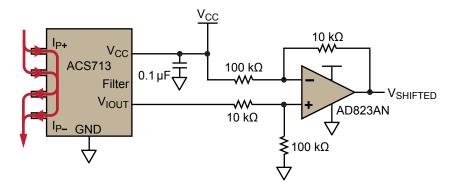

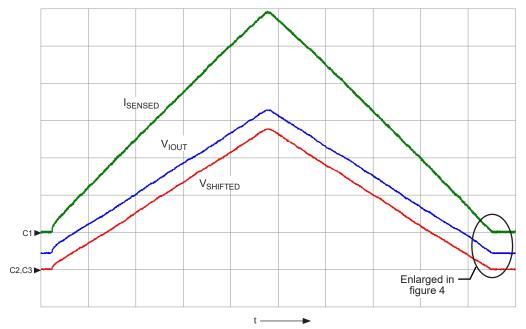

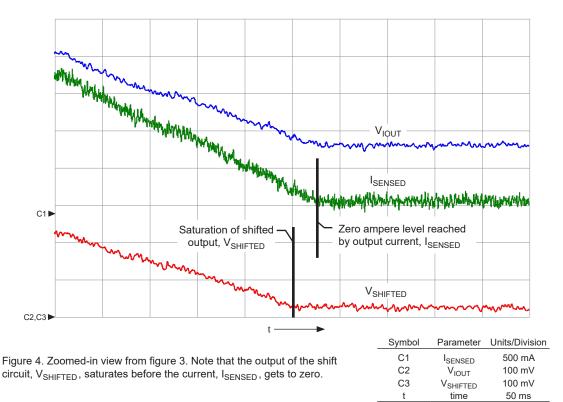

The circuit described above was used to shift the output of the ACS713-30A, so that it had no inherent offset voltage. The schematic is given in figure 2. A rail-to-rail op-amp, the AD823AN, was used in order to have the output of the circuit get as close to zero volts as possible at zero amperes. Figure 3 shows a scope trace of the shift circuit working as intended, and figure 4 shows a zoomed in-view of figure 3, highlighting the saturation of the output of the shift circuit. The op-amp is only able to get down to approximately 30 mV. As the sensitivity of the ACS713-30A is 133 mV/A, this corresponds to about 225 mA, which is very close to the current level at which the shifted output saturates, showing the expected behavior.

Figure 2. Schematic of ACS713 with output shifting circuit

Figure 3. Shifting of ACS713 output: I\_{SENSED} is the current flowing through the IC.  $V_{\rm IOUT}$  is the output of the ACS713.  $V_{\rm SHIFTED}$  is the output of the shift circuit.

| Symbol | Parameter            | Units/Division |

|--------|----------------------|----------------|

| C1     | ISENSED              | 5 A            |

| C2     | VIOUT                | 1 V            |

| C3     | V <sub>SHIFTED</sub> | 1 V            |

| t      | time                 | 1 s            |

## **Revision History**

| Number | Date           | Description               |

|--------|----------------|---------------------------|

| _      | March 23, 2012 | Initial release           |

| 1      | May 4, 2022    | Updated document branding |

Copyright 2022, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com