with SPI, I<sup>2</sup>C Interfaces, and Advanced Low-Power Management

#### **FEATURES AND BENEFITS**

- Flexible operating modes

- Can measure input in any one, two, or three axes

- 15-bit angle output from any selectable two-axis plane

- Low root-mean-square (RMS) angle noise for high system resolution

- SPI and I<sup>2</sup>C interfaces for easy system integration

- Up to 10 MHz serial peripheral interface (SPI)

- Up to 1 MHz inter-integrated circuit (I<sup>2</sup>C)

- Ideal for battery-powered, low-voltage applications

- 2.65 to 3.6 V analog supply operation

- 1.8 to 3.6 V digital supply operation

- Low-leakage sleep ICC

- Low-power duty cycle mode options for additional power savings

- Flexible multifunction pin for interrupt and sample-start functionality

- Interrupt pin provides digital output when user-defined threshold is exceeded

- On-chip EEPROM for storing factory and customerconfigured settings

- -40°C to 125°C operation

- AEC-Q100, Grade 1 automotive qualified

#### **APPLICATIONS**

- Valve position

- Shifter

- Human-machine interface (HMI)

#### **DESCRIPTION**

The A31331 three-axis Hall-effect sensor integrated circuit (IC) is a flexible magnetic sensor capable of measuring the applied flux density in any one, two, or three axes, as well as calculating the angle in up to any of two user-defined planes. The A31331 comes in a standard field configuration of  $\pm 600$  G. Additionally, the device is available preconfigured for SPI or I<sup>2</sup>C. The magnetic temperature coefficient is customer-programmable to support various magnet properties.

For ease of use, the A31331 supports two different digital interfaces: four-wire SPI or I<sup>2</sup>C. For high-speed applications, the SPI can operate at up to 10 MHz, and the I<sup>2</sup>C interface can operate at up to 1 MHz. The I<sup>2</sup>C address can be set by external resistors (16 unique addresses), or it can be programmed into EEPROM via I<sup>2</sup>C (127 unique addresses), allowing for multiple devices on the same bus.

Power management of the A31331 is highly configurable, allowing for system-level optimization of supply current and performance. Low-leakage sleep current makes the A31331 well-suited for portable, battery-operated applications.

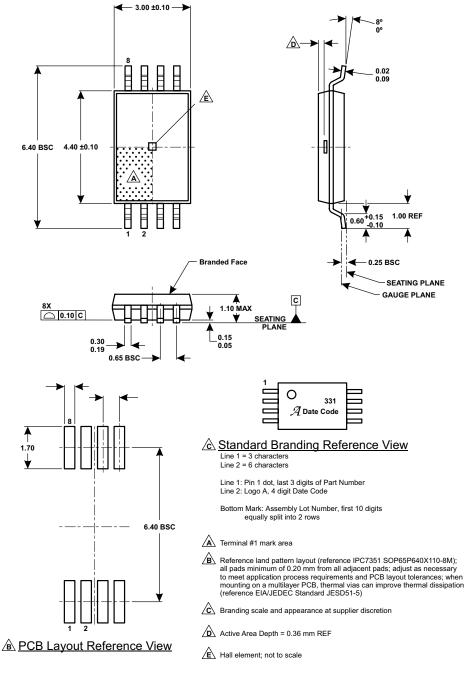

The A31331 is supplied in an eight-pin thin-shrink small-outline package (TSSOP). The package is lead (Pb) free with 100% matte tin leadframe plating.

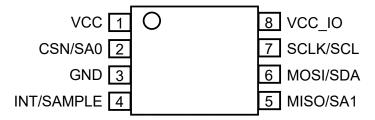

#### PACKAGE: 8-Pin TSSOP (LE)

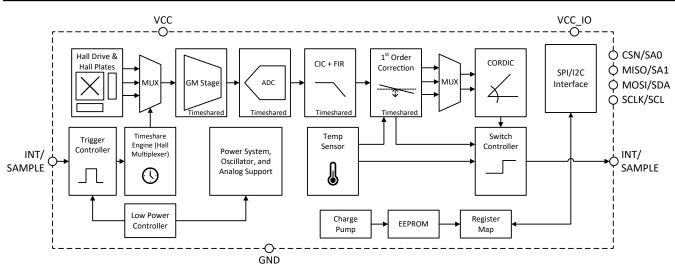

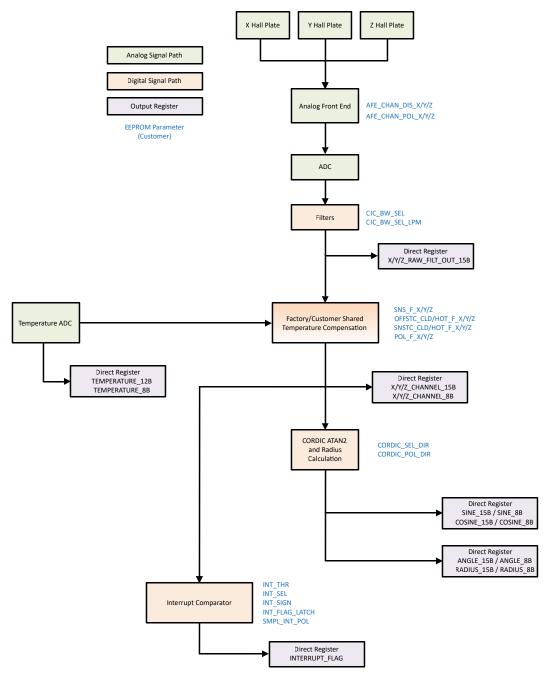

Figure 1: Functional Block Diagram

## with SPI, I<sup>2</sup>C Interfaces, and Advanced Low-Power Management

#### **SELECTION GUIDE**

| Part Number            | Default Interface | Supported Field Range (G) (Typ.) [1][2] | Packing <sup>[3]</sup>       |

|------------------------|-------------------|-----------------------------------------|------------------------------|

| A31331KLEATR-XYZ-IC-06 | I <sup>2</sup> C  | ±600                                    | 4000 pieces per 12 inch reel |

| A31331KLEATR-XYZ-SI-06 | SPI               | ±600                                    | 4000 pieces per 13-inch reel |

<sup>[1] 1</sup> gauss (G) = 0.1 millitesla (mT).

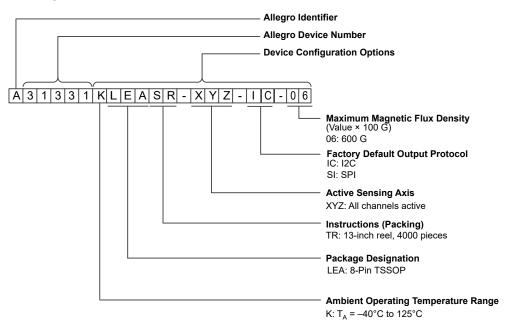

#### **NAMING SPECIFICATION**

<sup>[2]</sup> For alternate field range options, contact Allegro.

<sup>[3]</sup> Contact Allegro™ for alternate packing options.

## with SPI, I<sup>2</sup>C Interfaces, and Advanced Low-Power Management

### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic                 | Symbol               | Notes                                            | Rating              | Unit   |

|--------------------------------|----------------------|--------------------------------------------------|---------------------|--------|

| Forward Supply Voltage         | V <sub>CC</sub>      |                                                  | 3.6                 | V      |

| Reverse Supply Voltage         | V <sub>RCC</sub>     |                                                  | -0.5                | V      |

| Forward IO Supply Voltage      | V <sub>CC(IO)</sub>  |                                                  | V <sub>CC</sub>     | V      |

| Reverse IO Supply Voltage      | V <sub>RCC(IO)</sub> |                                                  | -0.5                | V      |

| All Other Pins Forward Voltage | V <sub>IN</sub>      | Digital IO Pins, SDA, SCL, SA0, SA1, SCLK, MISO, | V <sub>CC(IO)</sub> | V      |

| All Other Pins Reverse Voltage | V <sub>R</sub>       | MOSI, CSN                                        | -0.5                | V      |

| Operating Ambient Temperature  | T <sub>A</sub>       | Range K                                          | -40 to 125          | °C     |

| Maximum Junction Temperature   | T <sub>J(MAX)</sub>  |                                                  | 165                 | °C     |

| Storage Temperature [1]        | T <sub>stg</sub>     |                                                  | -65 to 170          | °C     |

| EEPROM Write Count [2]         | _                    | Number of times EEPROM can be written            | 100                 | writes |

<sup>[1]</sup> Stress beyond the absolute maximum rating might result in permanent device damage. Exposure to absolute maximum rating conditions for extended periods of time might affect device reliability.

#### THERMAL CHARACTERISTICS [1]

| Characteristic                 | Symbol         | Test Conditions                                                   |     | Unit |

|--------------------------------|----------------|-------------------------------------------------------------------|-----|------|

| Package Thermal Resistance [2] | $R_{	heta JA}$ | On four-layer printed circuit board (PCB) based on JEDEC standard | 145 | °C/W |

<sup>[1]</sup> Thermal characteristics might require derating at maximum conditions.

<sup>[2]</sup> EEPROM writes are not supported at temperatures greater than 85°C.

<sup>[2]</sup> Additional thermal information is available on the Allegro website.

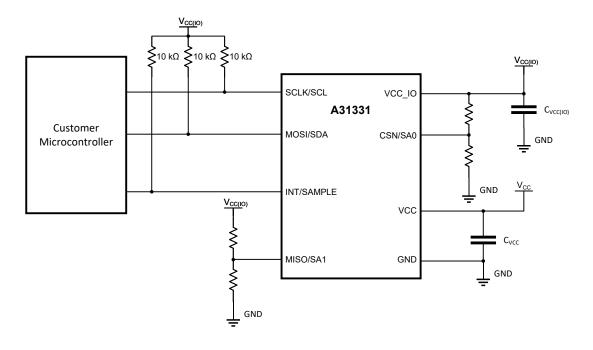

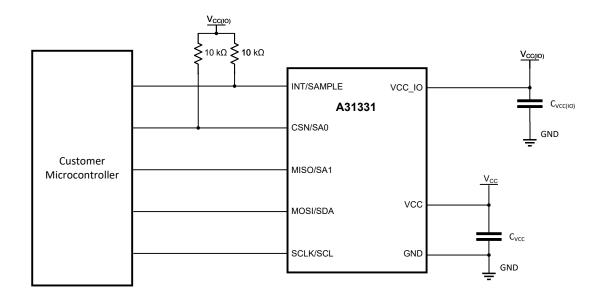

(a) I2C Interface

(b) SPI Interface

**Figure 2: Typical Application Circuits**

with SPI, I<sup>2</sup>C Interfaces, and Advanced Low-Power Management

#### PINOUT DIAGRAM AND TERMINAL LIST

Package LE, 8-Pin TSSOP Pinout Diagram

#### **Terminal List Table**

| Number | Name           | Function                                                                                                                                                                                                                                  |

|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | VCC            | Power supply input. Bypass VCC to GND with a 0.1 µF capacitor.                                                                                                                                                                            |

| 2      | CSN/SA0        | CSN: SPI chip select, active low. SA0: I <sup>2</sup> C address select 0. To select the device address, connect a resistive divider to SA0. For more information about addressing, see the Application Information section.               |

| 3      | GND            | Ground signal terminal.                                                                                                                                                                                                                   |

| 4      | INT/<br>SAMPLE | INT: Interrupt output. For more information about the interrupt function, see the Application Information section. SAMPLE: Sample trigger Input. For more information about the sample function, see the Application Information section. |

|        |                | If this functionality is not used and is disabled, it is recommended to tie this pin to ground.                                                                                                                                           |

| 5      | MISO/SA1       | MISO (controller-in peripheral-out): SPI output SA1: I <sup>2</sup> C address select 1. To select the device address, connect a resistive divider to SA1. For more information about addressing, see the Application Information section. |

| 6      | MOSI/SDA       | MOSI (controller-out peripheral-in): SPI input. SDA: I <sup>2</sup> C serial data input/output. Open-drain.                                                                                                                               |

| 7      | SCLK/SCL       | SCLK: SPI serial clock input.<br>SCL: I <sup>2</sup> C serial clock input.                                                                                                                                                                |

| 8      | VCC_IO         | Voltage reference for digital input/output (IO) pins.                                                                                                                                                                                     |

### with SPI, I<sup>2</sup>C Interfaces, and Advanced Low-Power Management

ELECTRICAL CHARACTERISTICS: Valid at T<sub>A</sub> = 25°C, V<sub>CC</sub> = V<sub>CC IO</sub> = 3 V, C<sub>BYPASS</sub> = 0.1 μF, unless otherwise specified

| Characteristics                    | Symbol                    | Test Conditions                                                             | Min. | Тур. | Max.            | Unit                 |

|------------------------------------|---------------------------|-----------------------------------------------------------------------------|------|------|-----------------|----------------------|

| ELECTRICAL CHARACTERISTI           | cs                        |                                                                             |      | `    |                 |                      |

| Complex Valtage                    |                           | Typical operation                                                           | 2.65 | 3    | 3.6             | V                    |

| Supply Voltage                     | V <sub>CC</sub>           | EEPROM programming [1]                                                      | 2.8  | _    | 3.5             | V                    |

| Supply Voltage Ramp <sup>[2]</sup> | V <sub>CC_RAMP</sub>      | Ramp rate from 0 to 3.3 V                                                   | 0.1  | _    | 10000           | μs                   |

| Digital Supply Voltage             | V <sub>CC_IO</sub>        | $V_{CC\_IO} \le V_{CC}$                                                     | 1.7  | _    | V <sub>cc</sub> | V                    |

|                                    | I <sub>CC(ACTIVE)</sub>   | Active state                                                                | _    | 3.8  | 4.75            | mA                   |

|                                    | I <sub>CC(INACTIVE)</sub> | OP_MODE = 5, 6; inactive state                                              | _    | 25   | _               | μA                   |

|                                    | _                         | Average current in LPDCM; OP_MODE = 6,<br>SLEEP_CNT = 7, CIC_BW_SEL_LPM = 6 | _    | 25   | _               | μА                   |

| Supply Current [3]                 | I <sub>CC(LPDCM)</sub>    | Average current in LPDCM; OP_MODE = 6,<br>SLEEP_CNT = 0, CIC_BW_SEL_LPM = 0 | _    | 2    | _               | mA                   |

|                                    | I <sub>CC(SLEEP)</sub>    | V <sub>CC</sub> = 3 V, OP_MODE = 3, 4 [4]                                   | _    | 2.5  | _               | μA                   |

|                                    | I <sub>CC(EE)</sub>       | V <sub>CC</sub> = V <sub>CC(MAX)</sub> , EEPROM programming occurring [2]   | _    | 6.2  | _               | mA                   |

|                                    | I <sub>CC_IO</sub>        | Current consumption on VCC_IO                                               | _    | 25   | _               | μA                   |

| Power-On Reset                     | V <sub>POR</sub>          | Minimum V <sub>CC</sub> before turn-on                                      | _    | 2.51 | _               | V                    |

| Power-On Delay Time [5]            | t <sub>POD</sub>          | $T_A$ = 25°C, after $V_{CC}$ reaches $V_{CC(MIN)}$ , BW select = 0          | 1    | _    | _               | ms                   |

| EEPROM Write Delay Time            | t <sub>EEP</sub>          | Wait after writing to EEPROM                                                | _    | 50   | -               | ms                   |

| Linearity Sensitivity Error        | E <sub>LIN</sub>          | Through full range of B <sub>IN</sub>                                       | _    | ±1.7 | _               | %                    |

| INT PIN CHARACTERISTICS            |                           |                                                                             |      |      |                 |                      |

| INT Output On Resistance           | R <sub>ON</sub>           |                                                                             | _    | 90   | _               | Ω                    |

| INT Input Current                  | I <sub>INT(IN)</sub>      | V <sub>IN</sub> = 0 V to V <sub>CC</sub>                                    | -1   | 0    | 1               | μA                   |

| INT Pull Up Resistance             | R <sub>INT(PU)</sub>      |                                                                             | 2.4  | 10   | _               | kΩ                   |

| INT Pull Up Voltage                | V <sub>INT(PU)</sub>      |                                                                             | _    | 3    | 3.6             | V                    |

| ADDRESS PIN CHARACTERISTICS [2]    |                           |                                                                             |      |      |                 |                      |

| Address Value 0 Reference          | V <sub>ADDR0</sub>        | SA0, SA1                                                                    | _    | 0    | 0.1             | × V <sub>CC_IO</sub> |

| Address Value 1 Reference          | V <sub>ADDR1</sub>        | SA0, SA1                                                                    | 0.23 | 0.33 | 0.43            | × V <sub>CC_IO</sub> |

| Address Value 2 Reference          | V <sub>ADDR2</sub>        | SA0, SA1                                                                    | 0.57 | 0.67 | 0.77            | × V <sub>CC_IO</sub> |

| Address Value 3 Reference          | V <sub>ADDR3</sub>        | SA0, SA1                                                                    | 0.9  | 1    | _               | × V <sub>CC_IO</sub> |

| Address Pin Input Resistance       | R <sub>ADD(IN)</sub>      | SA0, SA1                                                                    | 0.8  | 1    | 1.2             | МΩ                   |

<sup>[1]</sup> Parameter is tested at wafer probe only.

<sup>[2]</sup> Parameter not measured at final test. Determined by design and characterization.

<sup>[3]</sup> I<sub>CC</sub> varies based on lower-power duty cycle settings. For more information about power modes, see the Application Information section.

<sup>[4]</sup> In OP\_MODE = 4: I<sub>CC(SLEEP)</sub> occurs during the idle window. When a conversion is requested, the device draws the same current as I<sub>CC(ACTIVE)</sub>. The average I<sub>CC</sub> is dependent on the user-set sampling rate.

<sup>[5]</sup> Minimum time to delay after power-on before initiating communications. The device does not respond to I<sup>2</sup>C or SPI inputs until after the power-on delay time, t<sub>POD</sub>, which varies based on the bandwidth (BW) select code, where code 0 is the longest duration.

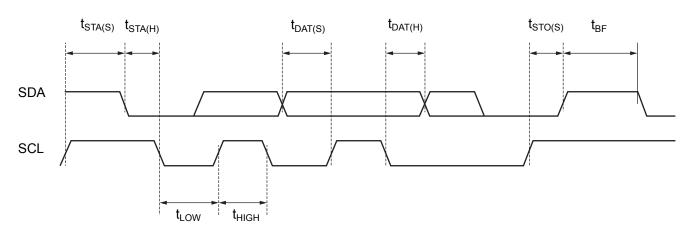

I<sup>2</sup>C INTERFACE CHARACTERISTICS [¹]: Valid at  $T_A$  = 25°C,  $V_{CC}$  =  $V_{CC\_IO}$  = 3 V,  $C_{BYPASS}$  = 0.1 μF,  $R_{PU}$  = 10 kΩ, and I<sup>2</sup>C clock speed (FCLK) = 400 kHz, unless otherwise specified

| Characteristics                             | Symbol               | Test Conditions                                                 | Min. | Тур. | Max. | Unit |

|---------------------------------------------|----------------------|-----------------------------------------------------------------|------|------|------|------|

| Bus Free Time Between Stop and Start        |                      | OP_MODE = 0, 1, 2                                               | 1.3  | _    | _    | μs   |

| bus Free Time between Stop and Start        | t <sub>BF</sub>      | OP_MODE = 5, 6                                                  | 25   | -    | _    | μs   |

| Hold Time Start Condition                   | t <sub>STA(H)</sub>  |                                                                 | 0.6  | -    | _    | μs   |

| Setup Time for Repeated Start Condition     | t <sub>STA(S)</sub>  |                                                                 | 0.6  | -    | _    | μs   |

| SCL Low Time                                | t <sub>LOW</sub>     |                                                                 | 1.3  | _    | _    | μs   |

| SCL High Time                               | t <sub>HIGH</sub>    |                                                                 | 0.6  | _    | _    | μs   |

| Data Setup Time                             | t <sub>DAT(S)</sub>  |                                                                 | 100  | _    | _    | ns   |

| Data Hold Time                              | t <sub>DAT(H)</sub>  |                                                                 | 0    | _    | 900  | ns   |

| Setup Time for Stop Condition               | t <sub>STO(S)</sub>  |                                                                 | 0.6  | _    | _    | μs   |

| Logic Input Love Love (SDA SCI Dine)        | V                    | I2C_THRESH_SEL = 0;<br>3 V-compatible mode                      | _    | _    | 0.9  | V    |

| Logic Input Low Level (SDA, SCL Pins)       | V <sub>I(L)</sub>    | I2C_THRESH_SEL = 1;<br>1.8 V-compatible mode                    | -    | _    | 0.54 | V    |

| La sia la sat High Lasa L (ODA OOL Bira)    | .,                   | I2C_THRESH_SEL = 0;<br>3 V-compatible mode                      | 2.1  | _    | _    | V    |

| Logic Input High Level (SDA, SCL Pins)      | V <sub>I(H)</sub>    | I2C_THRESH_SEL = 1;<br>1.8 V-compatible mode                    | 1.26 | _    | _    | V    |

| Logic Input Current                         | I <sub>I2C(IN)</sub> | $V_{IN} = 0 \text{ V to } V_{CC}, R_{PU} = 2.4 \text{ k}\Omega$ | -1   | 0    | 1    | μA   |

| Output Voltage (SDA Pin)                    | V <sub>O(L)</sub>    | I <sub>LOAD</sub> = 1.5 mA                                      | _    | _    | 0.36 | V    |

| Clock Frequency (SCL Pin)                   | f <sub>CLK</sub>     |                                                                 | _    | 400  | 1000 | kHz  |

| Output Fall Time (SDA Pin)                  | t <sub>f</sub>       | $R_{PU} = 2.4 \text{ k}\Omega, C_{BUS} = 100 \text{ pF}$        | _    | _    | 250  | ns   |

| I <sup>2</sup> C Pull-Up Resistance         | R <sub>I2C(PU)</sub> |                                                                 | 2.4  | 10   | _    | kΩ   |

| I <sup>2</sup> C Pull-Up Voltage            | V <sub>I2C(PU)</sub> |                                                                 | 1.8  | 3    | 3.3  | V    |

| Total Capacitive Load for SDL and SDA Buses | C <sub>BUS</sub>     |                                                                 | _    | _    | 100  | pF   |

[1] I<sup>2</sup>C interface characteristics are not measured at final test. Determined by design and characterization.

Figure 3: I<sup>2</sup>C Interface Timing Diagram

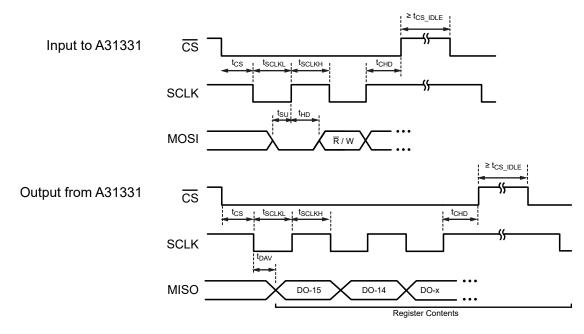

| SPI INTERFACE CHARACTERISTICS: Valid at T <sub>A</sub> = 25° | °C. Cpypage = 0.1 µF. unless otherwise noted |

|--------------------------------------------------------------|----------------------------------------------|

|--------------------------------------------------------------|----------------------------------------------|

| Characteristics               | Symbol               | Test Conditions                                                                    | Min. | Тур. | Max. | Unit                 |

|-------------------------------|----------------------|------------------------------------------------------------------------------------|------|------|------|----------------------|

| SPI INTERFACE SPECIFICATIONS  |                      |                                                                                    |      |      |      |                      |

| SPI Packet Size               | N <sub>SPI</sub>     | Number of bits per SPI transaction, with and without cyclic redundancy check (CRC) | 16   | _    | 20   | bits                 |

| Digital Input High Voltage    | V <sub>IH</sub>      | MOSI, SCLK, CSN pins                                                               | 0.65 | _    | 1    | × V <sub>CC_IO</sub> |

| Digital Input Low Voltage     | V <sub>IL</sub>      | MOSI, SCLK, CSN pins                                                               | -    | _    | 0.35 | × V <sub>CC_IO</sub> |

| SPI Output High Voltage       | V <sub>OH</sub>      | MISO pins, C <sub>L</sub> = 10 pF                                                  | -    | _    | _    | V                    |

| SPI Output Low Voltage        | V <sub>OL</sub>      | MISO pins, C <sub>L</sub> = 10 pF                                                  | _    | _    | -    | V                    |

| SPI Clock Frequency           | f <sub>SPI</sub>     |                                                                                    | 0.1  | _    | 10   | MHz                  |

| SPI Duty Cycle                | D <sub>fSCLK</sub>   | SPICLK <sub>DC</sub>                                                               | 40   | -    | 60   | %                    |

| SPI Frame Rate                | t <sub>SPI</sub>     |                                                                                    | 5.8  | -    | 588  | kHz                  |

| Chip Select to First SCK Edge | t <sub>CS</sub>      | Time from CSN going low to SCLK falling edge                                       | 50   | _    | _    | ns                   |

| Chin Coloct Idla Tima         |                      | OP_MODE = 0, 1, 2                                                                  | 425  | _    | _    | ns                   |

| Chip Select Idle Time         | t <sub>CS_IDLE</sub> | OP_MODE = 5, 6                                                                     | 37.5 | _    | _    | μs                   |

| Data Out Valid Time           | t <sub>DAV</sub>     | Data output valid after SCLK falling edge                                          | _    | 30   | _    | ns                   |

| MOSI Setup Time               | t <sub>SU</sub>      | Input setup time before SCLK rising edge                                           | 25   | _    | -    | ns                   |

| MOSI Hold Time                | t <sub>HD</sub>      | Input hold time after SCLK rising edge                                             | 50   | _    | _    | ns                   |

| MISO Off Time                 | t <sub>off</sub>     | Time from CSN going high to MISO tri-stating                                       | _    | 45   | _    | ns                   |

| SCLK to CS Hold Time          | t <sub>CHD</sub>     | Hold SCLK high time before CS rising edge                                          | 5    | _    | _    | ns                   |

| Load Capacitance              | C <sub>L</sub>       | Loading on digital output (MISO) pin, V <sub>CC_IO</sub> = 3.3 V                   | _    | _    | 10   | pF                   |

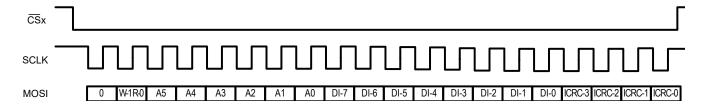

Figure 4: SPI Interface Timings: Input (Top) and Register Output (Bottom)

## with SPI, I<sup>2</sup>C Interfaces, and Advanced Low-Power Management

# A31331KLEA-XYZ-06 PERFORMANCE CHARACTERISTICS: Valid at $V_{CC}$ = 3 V, and $C_{BYPASS}$ = 0.1 $\mu$ F, unless otherwise specified

| Characteristics                     | Symbol                    | Test Conditions                                       | Min.  | Тур.  | Max. | Unit [1] |

|-------------------------------------|---------------------------|-------------------------------------------------------|-------|-------|------|----------|

| NOMINAL PERFORMANCE                 |                           |                                                       |       |       |      |          |

| Optimized Sensing Range             | B <sub>IN</sub>           |                                                       | _     | ±600  | _    | G        |

| Sensitivity                         | SENS                      | T <sub>A</sub> = 25°C                                 | _     | 24.82 | _    | LSB/G    |

| Sensitivity Temperature Coefficient | SENS <sub>TC</sub>        | -40°C < T <sub>A</sub> < 125°C                        | _     | 0.04  | _    | %/°C     |

| Zero-Field Offset Code              | OFF                       | B <sub>IN</sub> = 0 G, -40°C < T <sub>A</sub> < 125°C | -     | 0     | _    | LSB      |

| NOISE CHARACTERISTICS [2]           |                           |                                                       |       |       |      |          |

| DMC Naise V/V Channels [3]          | N                         | BW select = 0                                         | _     | 0.1   | _    | G        |

| RMS Noise X/Y Channels [3]          | N <sub>RMS(XY)</sub>      | BW select = 6                                         | _     | 0.8   | _    | G        |

| DMO Nation 7 Observed [3]           |                           | BW select = 0                                         | _     | 0.052 | _    | G        |

| RMS Noise Z Channel [3]             | N <sub>RMS(Z)</sub>       | BW select = 6                                         | _     | 0.414 | _    | G        |

| RMS Angle Noise [3]                 | N <sub>RMS(θXY)</sub>     | BW select = 0, B <sub>IN</sub> = 300 G                | _     | 0.02  | _    | ۰        |

| ACCURACY PERFORMANCE                |                           |                                                       |       |       |      |          |

| Official Famous VIV Access          |                           | B <sub>IN</sub> = 0 G, T <sub>A</sub> = 25°C          | -6    | _     | 6    | G        |

| Offset Error X/Y Axes               | E <sub>OFF(XY)</sub>      | B <sub>IN</sub> = 0 G, -40°C < T <sub>A</sub> < 125°C | -6    | _     | 6    | G        |

| Official Famous 7 April             | _                         | B <sub>IN</sub> = 0 G, T <sub>A</sub> = 25°C          | -6    | _     | 6    | G        |

| Offset Error Z Axis                 | E <sub>OFF(Z)</sub>       | B <sub>IN</sub> = 0 G, -40°C < T <sub>A</sub> < 125°C | -6    | -     | 6    | G        |

|                                     |                           | T <sub>A</sub> = 25°C                                 | -2.5  | -     | 2.5  | %        |

| Sensitivity Error X/Y Axes          | E <sub>SENS(XY)</sub>     | 25°C < T <sub>A</sub> < 125°C                         | -4    | -     | 4    | %        |

|                                     |                           | -40°C < T <sub>A</sub> < 25°C                         | -5.2  | _     | 5.2  | %        |

|                                     |                           | T <sub>A</sub> = 25°C                                 | -3.5  | -     | 3.5  | %        |

| Sensitivity Error Z Axis            | E <sub>SENS(Z)</sub>      | 25°C < T <sub>A</sub> < 125°C                         | -4    | _     | 4    | %        |

|                                     |                           | -40°C < T <sub>A</sub> < 25°C                         | -5.2  | _     | 5.2  | %        |

| Sensitivity Mismatch Error          | _                         | T <sub>A</sub> = 25°C                                 | -1.1  | -     | 1.1  | %        |

| X Axis to Y Axis                    | E <sub>MATCH(XY)</sub>    | -40°C < T <sub>A</sub> < 125°C                        | -1.1  | -     | 1.1  | %        |

| Sensitivity Mismatch Error          | _                         | T <sub>A</sub> = 25°C                                 | -3    | -     | 3    | %        |

| X/Y Axes to Z Axis                  | E <sub>MATCH(XZ,YZ)</sub> | -40°C < T <sub>A</sub> < 125°C                        | -4    | -     | 4    | %        |

| 0.11                                |                           | T <sub>A</sub> = 25°C                                 | -1.75 | _     | 1.75 | ۰        |

| Orthogonality Error, X-Y Plane      | E <sub>ORTHO(XY)</sub>    | -40°C < T <sub>A</sub> < 125°C                        | -2    | -     | 2    | ۰        |

| Angle Frank V V Dlene               |                           | B <sub>IN</sub> ≥ 300 G, T <sub>A</sub> = 25°C        | -1.5  | _     | 1.5  | ۰        |

| Angle Error X-Y Plane               | E <sub>ANG(XY)</sub>      | B <sub>IN</sub> ≥ 300 G                               | -2    | _     | 2    | ۰        |

| An als Fare V 7 V 7 D 121           |                           | B <sub>IN</sub> ≥ 300 G, T <sub>A</sub> = 25°C        | -2    | _     | 2    | ۰        |

| Angle Error X-Z, Y-Z Plane [3]      | $E_{ANG(XZ,YZ)}$          | B <sub>IN</sub> ≥ 300 G                               | -2.5  | -     | 2.5  | ۰        |

<sup>[1] 1</sup> G (gauss) = 0.1 mT (millitesla)

<sup>[2]</sup> RMS noise equivalent to 1 standard deviation (sigma) distribution.

<sup>[3]</sup> Parameter not measured at final test. Determined by design and characterization.

## with SPI, I<sup>2</sup>C Interfaces, and Advanced Low-Power Management

# A31331KLEA-XYZ-06 PERFORMANCE CHARACTERISTICS (continued): Valid at $V_{CC}$ = 3 V, and $C_{BYPASS}$ = 0.1 $\mu$ F, unless otherwise specified

| Characteristics                                     | Symbol                         | Test Conditions                                                                                   | Min.  | Тур. | Max. | Unit [1] |

|-----------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------|-------|------|------|----------|

| DRIFT CHARACTERISTICS—TEMPERATURE                   |                                |                                                                                                   |       |      |      |          |

| Offset Drift X/Y Axes                               | D <sub>OFF,TEMP(XY)</sub>      | $-40$ °C < $T_A$ < 125°C, relative to $T_A$ = 25°C                                                | -4    | _    | 4    | G        |

| Offset Drift Z Axis                                 | D <sub>OFF,TEMP(Z)</sub>       | $-40$ °C < $T_A$ < 125°C, relative to $T_A$ = 25°C                                                | -4    | _    | 4    | G        |

| Consistivity Drift VIV Avec                         | Б                              | 25°C < T <sub>A</sub> < 125°C, relative to T <sub>A</sub> = 25°C                                  | 0.00  | _    | 0.08 | %/°C     |

| Sensitivity Drift X/Y Axes                          | $D_{SENS,TEMP(XY)}$            | -40°C < T <sub>A</sub> < 25°C, relative to T <sub>A</sub> = 25°C                                  | -0.04 | _    | 0.12 | %/°C     |

| Considiuita Duiti 7 Anio                            |                                | 25°C < T <sub>A</sub> < 125°C, relative to T <sub>A</sub> = 25°C                                  | 0.00  | _    | 0.08 | %/°C     |

| Sensitivity Drift Z Axis                            | $D_{SENS,TEMP(Z)}$             | -40°C < T <sub>A</sub> < 25°C, relative to T <sub>A</sub> = 25°C                                  | -0.04 | _    | 0.12 | %/°C     |

| Sensitivity Mismatch Error Drift X Axis to Y Axis   | D <sub>MATCH,TEMP(XY)</sub>    | -40°C < T <sub>A</sub> < 125°C, relative to T <sub>A</sub> = 25°C                                 | -1.5  | _    | 1.5  | %        |

| Sensitivity Mismatch Error Drift X/Y Axes to Z Axis | D <sub>MATCH,TEMP(XZ,YZ)</sub> | $-40$ °C < $T_A$ < 125°C, relative to $T_A$ = 25°C                                                | -3.5  | _    | 3.5  | %        |

| Orthogonality Error Drift, X-Y Plane                | D <sub>ORTHO,TEMP(XY)</sub>    | -40°C < T <sub>A</sub> < 125°C, relative to T <sub>A</sub> = 25°C                                 | -1.5  | _    | 1.5  | ۰        |

| Angle Error Drift, X-Y Plane                        | D <sub>ANG,TEMP(XY)</sub>      | $-40^{\circ}$ C < T <sub>A</sub> < 125°C, relative to T <sub>A</sub> = 25°C.                      | -1.1  | _    | 1.1  | o        |

| Angle Error Drift, X-Z, Y-Z Plane [3]               | D <sub>ANG,TEMP(XZ,YZ)</sub>   | $-40$ °C < T <sub>A</sub> < 125°C, relative to T <sub>A</sub> = 25°C, B <sub>IN</sub> $\ge$ 300 G | -1.5  | _    | 1.5  | 0        |

<sup>[1] 1</sup> G (gauss) = 0.1 mT (millitesla)

<sup>[2]</sup> Lifetime Drift Characteristics will be based on worst-case error or drift seen during device qualification.

<sup>[3]</sup> Parameter not measured at final test. Determined by design and characterization.

## with SPI, I<sup>2</sup>C Interfaces, and Advanced Low-Power Management

# A31331KLEA-XYZ-06 PERFORMANCE CHARACTERISTICS (continued): Valid at $V_{CC}$ = 3 V, and $C_{BYPASS}$ = 0.1 $\mu$ F, unless otherwise specified

| Characteristics                                     | Symbol                         | Test Conditions                                                                                | Min.  | Тур. | Max. | Unit [1] |

|-----------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------|-------|------|------|----------|

| DRIFT CHARACTERISTICS—TEMPI                         | RATURE AND I                   | LIFETIME [2]                                                                                   |       |      |      |          |

| Offset Drift X/Y Axes                               | D <sub>OFF,LIFE(XY)</sub>      | -40°C < T <sub>A</sub> < 125°C, Relative to T <sub>A</sub> = 25°C pre-stress conditions        | -3    | -    | 3    | G        |

| Offset Drift Z Axis                                 | D <sub>OFF,LIFE(Z)</sub>       | -40°C < T <sub>A</sub> < 125°C, Relative to T <sub>A</sub> = 25°C pre-stress conditions        | -2    | -    | 2    | G        |

| Considiuity Drift V/V Avec                          | 5                              | 25°C < T <sub>A</sub> < 125°C, Relative to T <sub>A</sub> = 25°C pre-stress conditions         | 0.00  | _    | 0.08 | %/°C     |

| Sensitivity Drift X/Y Axes                          | D <sub>SENS,LIFE(XY)</sub>     | $-40$ °C < $T_A$ < 25°C, Relative to $T_A$ = 25°C pre-stress conditions                        | -0.04 | _    | 0.12 | %/°C     |

|                                                     | D                              | 25°C < T <sub>A</sub> < 125°C, Relative to T <sub>A</sub> = 25°C pre-stress conditions         | 0.00  | -    | 0.11 | %/°C     |

| Sensitivity Drift Z Axis                            | D <sub>SENS,LIFE(Z)</sub>      | $-40$ °C < $T_A$ < 25°C, Relative to $T_A$ = 25°C pre-stress conditions                        | -0.07 | _    | 0.04 | %/°C     |

| Sensitivity Mismatch Error Drift X Axis to Y Axis   | D <sub>MATCH,LIFE(XY)</sub>    | -40°C < T <sub>A</sub> < 125°C, Relative to T <sub>A</sub> = 25°C pre-stress conditions        | -1.5  | _    | 1.5  | %        |

| Sensitivity Mismatch Error Drift X/Y Axes to Z Axis | D <sub>MATCH,LIFE(XZ,YZ)</sub> | $-40$ °C < $T_A$ < 125°C, Relative to $T_A$ = 25°C pre-stress conditions                       | -4.5  | _    | 4.5  | %        |

| Orthogonality Error Drift, X-Y Plane                | D <sub>ORTHO,LIFE(XY)</sub>    | $-40$ °C < $T_A$ < 125°C, Relative to $T_A$ = 25°C pre-stress conditions                       | -2.6  | ı    | 2.6  | ۰        |

| Angle Error Drift, X-Y Plane                        | D <sub>ANG,LIFE(XY)</sub>      | $-40$ °C < $T_A$ < 125 °C, Relative to $T_A$ = 25 °C pre-stress conditions, $B_{IN} \ge 300$ G | -1.6  | -    | 1.6  | ٥        |

| Angle Error Drift, X-Z, Y-Z Plane                   | D <sub>ANG,LIFE(XZ,YZ)</sub>   | $-40$ °C < $T_A$ < 125°C, Relative to $T_A$ = 25°C pre-stress conditions, $B_{IN} \ge 300$ G   | -2.25 | _    | 2.25 | ۰        |

<sup>[1] 1</sup> G (gauss) = 0.1 mT (millitesla)

<sup>[2]</sup> Lifetime drift characteristics are based on the worst-case error or drift observed during device AEC-Q100 Grade 1 quality stress testing.

#### APPLICATION INFORMATION

Figure 5: A31331 Signal Path

### Magnetic Sensor(s) Output

The A31331 provides 8-bit and 15-bit digital output value options that are proportional to the magnetic field that is typically applied to any of the Hall elements as the X-, Y-, and Z-channels. Each channel is factory-trimmed for sensitivity and offset accuracy at room temperature, as well as with a target temperature compensation. For additional adjustment in application, the room sensitivity and sensitivity parameter and the offset temperature compensation parameter are accessible by the customer. This allows the A31331 to be used in both rotary and linear position applications in any mounting orientation relative to the sensing magnet and to provide high accuracy and matching as the device and magnetic system changes over temperature. Starting with the raw filter output, which can be read in registers X/Y/Z\_RAW\_FILT\_OUT\_15B, the single-dimension magnetic data is corrected through the following steps:

$A = X/Y/Z_RAW_FILT_OUT_15B + Factory \ Offset \ Correction$   $B = A \times SENS_F_X/_Y/_Z \times -1^{(POL_F_X/Y/Z)}$

$C = B + (OFFSTC\_HOT/CLD\_F\_X/Y/Z \times Temperature)$

X/Y/Z\_CHANNEL\_15B =  $C \times (SENSTC\_HOT/CLD\_F\_X/Y/Z \times Temperature)$

The A31331 features an internal ATAN calculation on any two of the three user-selectable axes, X, Y, or Z. One of the channels is designated as the sine channel, and the other is designated as the cosine channel. This is performed with the indirect extended-space EEPROM parameter CORDIC\_SEL or the volatile direct primary-space parameter CORDIC SEL DIR.

Table 1: CORDIC\_SEL Decode

| CORDIC_SEL | COSINE Channel | SINE Channel |

|------------|----------------|--------------|

| 0          | X              | Y            |

| 1          | X              | Z            |

| 2          | Y              | Z            |

| 3          | Y              | X            |

| 4          | Z              | Х            |

| 5          | Z              | Y            |

| 6          | Х              | Y            |

| 7          | Х              | Y            |

The sine channel is stored in the direct primary-space registers SIN\_8B and SINE\_15B. The cosine channel is stored in the direct primary-space registers COS\_8B and COSINE\_15B.

The angle between the magnetic vectors selected by the sine and cosine channels is taken as the ATAN, following the equation:

$$\theta = \tan^{-1} \frac{\sin \theta}{\cos \theta}$$

This angle can have an inverted polarity, decreasing code output with increasing input angle using the CORDIC POL parameter.

$$Angle_{Out} = \begin{cases} Angle_{in} & for CORDIC\_POL = 0 \\ 360^{\circ} - Angle_{in} & for CORDIC\_POL = 1 \end{cases}$$

Polarity can also be adjusted after power-on in the volatile direct primary-space register CORDIC\_POL\_DIR. The angle output is stored in the direct-space registers ANGLE\_8B and ANGLE\_15B.

While calculating the angle, digital processing also tracks the magnitude of the angle vector from the sine and cosine channels as the radius squared, following the equation:

$$radius^2 = cosine^2 + sine^2$$

This radius-squared value is stored in the direct-space registers RADIUS SQ 8B and RADIUS 15B.

#### **Temperature Sensor Output**

The A31331 provides a 12-bit digital output that is proportional to the junction temperature of the IC. Temperature can be calculated by:

$$Temp [°C] = \frac{TEMPERATURE\_12B}{8.052} + 25$$

## Special Function Pin INT/SAMPLE

The A31331 has a special function pin, INT/SAMPLE, that can be set as either an output as an interrupt pin, or an input as a sample request pin, depending on the configured power mode.

#### **SAMPLE MODE**

While in sample mode, the special function pin acts as an input and can trigger a request to start a new conversation of the magnetic signal. This allows the host/user to synchronize the acquisition of the magnetic data. The device remains in a standby mode (no data acquisition) until either the INT/SAMPLE pin is brought high or the direct register START\_SAMPLE bit is set by the host. When this pin transitions to active (defined by SAMPLE\_INT\_POLARITY\_DIR) or when the START\_SAMPLE bit is set, a sample is triggered. The front end acquires data, the output registers are updated with the new data, the output registers are set, the STATUS\_READY flag asserts, and the device returns to standby. This mode is particularly useful for signal-processing applications that are sensitive to time/speed considerations (such as feedback and control applications) where deterministic sam-

## A31331

## 3D Linear Hall-Effect Sensor

## with SPI, I<sup>2</sup>C Interfaces, and Advanced Low-Power Management

pling is critical for loop stability.

If the device is in the process of acquiring new data from an initial sample request, subsequent sample signals are ignored. Data registers are updated only once per INT/SAMPLE pin or START\_SAMPLE write trigger. If DATA\_LATCH = 1, the STATUS\_READY bit must be cleared by the host writing a one to the bit once the reading of the stored data is complete, in order to allow a new acquisition to occur.

#### INTERRUPT MODE

When the pin is in interrupt mode, the special function pin is an output and is used to indicate when a certain internal threshold is surpassed. The threshold of interest is set by the direct-space INTERRUPT\_SEL\_DIR register or the indirect-space INT\_SEL

parameter and is compared to the programmed threshold in INTERRUPT\_THR\_MSB/LSB\_DIR in the direct space, loaded from INT\_THR in the indirect space. When the selected threshold condition is met, the interrupt flag becomes set in the direct-space register INTERRUPT\_FLAG and through the INT/SAMPLE pin. The INTERRUPT\_FLAG direct-space bit always remains asserted once it is set and, after the interrupt condition is removed, it must be cleared by writing it to a 1. If the parameter INTERRUPT\_FLAG\_LATCH\_DIR is set, the INT pin status also becomes latched until the INTERRUPT\_FLAG bit is written to a 1. In low-power mode, the flag requires 20 μs to clear after the write.

Table 2: Interrupt Selection Options, THR set by INTERRUPT\_THR\_MSB/LSB\_DIR in Direct Space

| INTERRUPT_SEL_<br>DIR/INT_SEL | Condition (INTERRUPT_SIGN_DIR = 0) | Threshold Register | Description                                                                  |

|-------------------------------|------------------------------------|--------------------|------------------------------------------------------------------------------|

| 0                             | THR > X                            | SIGNED             | Threshold register is compared to the trimmed X output                       |

| 1                             | THR > Y                            | SIGNED             | Threshold register is compared to the trimmed Y output                       |

| 2                             | THR > Z                            | SIGNED             | Threshold register is compared to the trimmed Z output                       |

| 3                             | THR > ABS(X)                       | UNSIGNED           | Threshold register is compared to the absolute value of the trimmed X output |

| 4                             | THR > ABS(Y)                       | UNSIGNED           | Threshold register is compared to the absolute value of the trimmed Y output |

| 5                             | THR > ABS(Z)                       | UNSIGNED           | Threshold register is compared to the absolute value of the trimmed Z output |

| 6                             | THR > TEMP                         | SIGNED             | Threshold register is compared to the temperature output                     |

| 7                             | THR > ANGLE                        | UNSIGNED           | Threshold register is compared to the angle output                           |

| 8                             | THR > RADIUS                       | UNSIGNED           | Threshold register is compared to the radius output                          |

| 9                             | THR = New Sample                   | _                  | No comparison; pin provides one 10 µs pulse that occurs when data is valid   |

#### **Operation Modes**

Power management on the A31331 is user-selectable and highly configurable, allowing for system-level optimization of current consumption and performance. The A31331 supports three different power modes: active mode, sleep mode, and low-power duty cycle mode (LPDCM), each with various subconfigurations using the special function pin INT/SAMPLE. The operating mode of the A31331 is determined by the value in the OP\_MODE field, in direct-space address [0x32:0x33], bits [3:1], described in Table 3.

#### **ACTIVE MODE**

In active mode, the A31331 continuously updates the channel and angle outputs at an interval defined by the bandwidth selection. This mode requires the most power but provides output register updates at the highest frequency. In addition to the standard output of active mode, the OP\_MODE register can be configured to set the device in active mode with the interrupt output enabled.

#### **SLEEP MODE**

In sleep mode, the A31331 enters a near powered-off state where it consumes the minimum amount of current. In this mode, the device continues to respond to  $I^2C$  or SPI commands, but it does not update magnetic or temperature data. In OP\_MODE = 4, sleep mode with sample wake, the device operates similarly to full-sleep mode, but it also monitors the INT/SAMPLE pin or START\_ SAMPLE bit for a trigger to start a conversion. This allows the host to set a conversion frequency to best balance power and response time in the system. Sleep mode is valuable in applications where the supply voltage cannot be disabled but minimal power consumption is required. The time it takes to exit sleep mode is equivalent to the power-on delay time ( $t_{POD}$ ).

#### LOW-POWER DUTY CYCLE MODE (LPDCM)

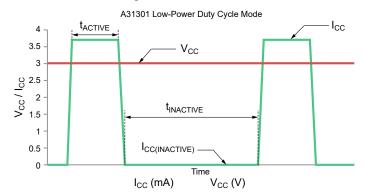

In low-power duty cycle mode (LPDCM), the A31331 toggles between the active and inactive states, reducing overall current consumption. During LPDCM, the average  $I_{\rm CC}$  for the A31331 varies based on the device configuration. The profile of  $I_{\rm CC}$  as the A31331 toggles between active and inactive states during LPDCM is shown in Figure 6.

Figure 6: I<sub>CC</sub> in Low-Power Duty Cycle Mode

The inactive time is determined by the value set in the SLEEP\_CNT field, address [0x32:0x33], bits [6:4]. The A31331 offers eight discrete time frames, explained in Table 4.

Table 3: OP\_MODE Control

| Address           | Bits | Value | Operating Mode                                   | INT/SAMPLE Pin Function |

|-------------------|------|-------|--------------------------------------------------|-------------------------|

|                   |      | 0     | Active Mode                                      | None                    |

|                   |      | 1     | Interrupt Output                                 |                         |

|                   |      | 2     | Active Mode—Sample                               | Sample Input            |

| Direct: 0x32:0x33 |      | 3     | Sleep Mode                                       | None                    |

| Direct. 0x32.0x33 | 3:1  | 4     | Sleep Mode with Sample Wake                      | Sample/Wake Input       |

|                   |      | 5     | Low-Power Duty Cycle Mode (LPDCM) with Interrupt | Interrupt Output        |

|                   |      | 6     | Low-Power Duty Cycle Mode (LPDCM)                | None                    |

|                   |      | 7     | Active Mode                                      | None                    |

Table 4: SLEEP\_CNT Decode; LPDCM Inactive Time (t<sub>INACTIVE</sub>)

|                   |      |       | CINACTIVE                        |

|-------------------|------|-------|----------------------------------|

| Address           | Bits | Value | t <sub>INACTIVE</sub> (typ) (ms) |

|                   |      | 0     | 0.68                             |

|                   |      | 1     | 1.36                             |

|                   |      | 2     | 6.82                             |

| Direct: 0x32:0x33 | 6:4  | 3     | 13.64                            |

| Direct. 0x32.0x33 | 0.4  | 4     | 68.18                            |

|                   |      | 5     | 136.36                           |

|                   |      | 6     | 681.82                           |

|                   |      | 7     | 1363.64                          |

The active time is determined by a combination of the value in the BW select field and the number of magnetic sensing channels enabled.

#### **Bandwidth Selection**

The A31331 has two parameters to control the device bandwidth and update rate in active mode and low-power mode: CIC\_BW\_SEL in indirect address 0x14, bits [2:0], controls filtering modes on the A31331 for the X, Y, and Z magnetic channels in active mode; and CIC\_BW\_SEL\_LPM in indrect address 0x14, bits [5:3] controls the filtering modes of the channels in low-power

duty cycle mode. This setting impacts the resolution of the sampled magnetic data, device update rate, and overall bandwidth.

A lower value for CIC\_BW\_SEL/LPM offers increased measurement resolution with a longer measurement duration. A higher value for CIC\_BW\_SEL/LPM offers faster measurement time at the expense of reduced resolution. This setting is valuable for controlling active time during low-power duty cycle mode or increasing response time. Typical noise versus CIC\_BW\_SEL/LPM is listed in Table 5.

Update rate (typical) versus CIC\_BW\_SEL/LPM and active channels is shown in Table 5. The A31331 updates internally at a high bandwidth. However, throughput may be limited by the communication protocol clocking frequency at the application level.

Magnetic sensing channels on the A31331 may be enabled independently with the AFE\_CHAN\_DIS\_X, AFE\_CHAN\_DIS\_Y, and AFE\_CHAN\_DIS\_Z bits in the indirect space, or the equivalent AFE\_CHAN\_DIS\_X\_DIR, AFE\_CHAN\_DIS\_Y\_DIR, and AFE\_CHAN\_DIS\_Z\_DIR in the direct space.

NOTE: When updating the CIC\_BW\_SEL or CIC\_BW\_SEL\_LPM, the device must be reset for the change to correctly take effect.

Table 5: Bandwidth Select, Filtering Modes, and Input Referred Noise (600 G Device Only)

| BW Select Value | Approximate<br>Bandwidth (Hz) | Approximate<br>Update Rate,<br>1 Channel (µs) | Approximate<br>Update Rate,<br>2 Channels (µs) | Approximate<br>Update Rate,<br>3 Channels (µs) | Z-Channel<br>Noise (G) | X-/Y-Channel<br>Noise (G) |

|-----------------|-------------------------------|-----------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------|---------------------------|

| 0               | 195.5                         | 1024                                          | 6156                                           | 9234                                           | 0.052                  | 0.100                     |

| 1               | 391                           | 512                                           | 3084                                           | 4626                                           | 0.073                  | 0.141                     |

| 2               | 782                           | 256                                           | 1548                                           | 2322                                           | 0.103                  | 0.200                     |

| 3               | 1564                          | 128                                           | 780                                            | 1170                                           | 0.146                  | 0.283                     |

| 4               | 3128                          | 64                                            | 396                                            | 594                                            | 0.207                  | 0.400                     |

| 5               | 6256                          | 32                                            | 204                                            | 306                                            | 0.293                  | 0.566                     |

| 6               | 12512                         | 16                                            | 108                                            | 162                                            | 0.414                  | 0.800                     |

| 7               |                               |                                               | Not Sup                                        | ported                                         |                        |                           |

#### INTERFACE INFORMATION

#### I<sup>2</sup>C Interface

I<sup>2</sup>C is a synchronous, two-wire serial communication protocol that provides a full-duplex interface between two or more devices. The bus specifies two logic signals:

- 1. Serial clock line (SCL) output by the controller.

- 2. Serial data line (SDA) output by either the controller or the peripheral.

The A31331 may only operate as a peripheral device. Therefore, it cannot initiate any transactions on the I<sup>2</sup>C bus.

#### **Data Transmission and Timing Considerations**

I<sup>2</sup>C communication comprises the following steps:

- 1. Start Condition: Defined by a negative edge of the SDA line, initiated by the controller, while SCL is high.

- 2. Address Cycle: 7-bit peripheral address, plus 1 bit to indicate write (0) or read (1), followed by an acknowledge bit.

- Data Cycles: Reading or writing 8 bits of data, followed by an acknowledge bit. This cycle can be repeated for multiple bytes of data transfer. The first data byte on a write could be the register address. For further information, see the sections that follow.

- 4. Stop Condition: Defined by a positive edge on the SDA line, while SCL is high.

Except to indicate the start or stop condition, SDA must remain stable while the clock signal is high. SDA may only change states while SCL is low. It is acceptable for a start or stop condition to occur at any time during the data transfer. The A31331 always responds to a read or write request by resetting the data transfer sequence.

The state of the Read/Write bit is set to 0 to indicate a write cycle and is set to 1 to indicate a read cycle.

The controller monitors for an acknowledge bit to confirm the peripheral device (A31331) is responding to the address byte. When the A31331 decodes the 7-bit peripheral address as valid, it responds by pulling SDA low during the ninth clock cycle.

When a data write is requested by the controller, the A31331 pulls SDA low during the clock cycle following the data byte to indicate that data receipt is successful.

After sending either an address byte or a data byte, the controller must release the SDA line before the ninth clock cycle, allowing the handshake process to occur.

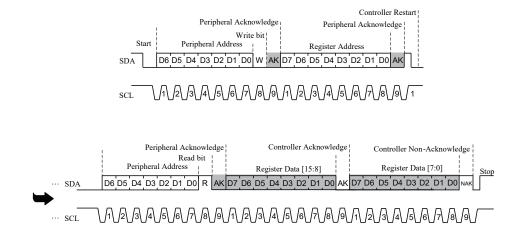

#### I<sup>2</sup>C Write Cycle Overview

The write cycle to access registers on the A31331 comprises the following steps:

- 1. Controller initiates the start condition.

- 2. Controller sends the 7-bit peripheral address and the write bit (0).

- 3. Controller waits for acknowledgement (ACK) from A31331.

- 4. Controller sends the 8-bit register address.

- 5. Controller waits for ACK from A31331.

- 6. Controller sends the data from bits [15:8].

- 7. Controller waits for ACK from A31331.

- 8. Controller sends the data from bits [7:0].

- 9. Controller waits for ACK from A31331.

- 10. Controller initiates the stop condition.

The I<sup>2</sup>C write sequence is further illustrated in the timing diagram in Figure 7.

Figure 7: I<sup>2</sup>C Write Timing Diagram

#### **Read Cycle Overview**

The read cycle to access registers on A31331 comprises the following steps:

- 1. Controller initiates the start condition.

- 2. Controller sends the 7-bit peripheral address and the write bit (0).

- 3. Controller waits for ACK from A31331.

- 4. Controller sends 8-bit register address.

- 5. Controller waits for ACK from A31331.

- 6. Initiate a start condition; this time it is referred to as a restart condition.

- 7. Controller sends the 7-bit peripheral address and the read bit (1).

- 8. Controller waits for ACK from A31331.

- 9. Controller receives the data of bits [15:8].

- 10. Controller sends ACK to A31331.

- 11. Controller receives the data of bits [7:0].

- Controller sends negative acknowledgement (NACK) to A31331.

- 13. Controller initiates the stop condition

The I<sup>2</sup>C read sequence is further illustrated in the timing diagrams in Figure 8.

The timing diagram in Figure 8 shows the entire contents (bits [15:0]) of a single register location being transmitted. Optionally, the I<sup>2</sup>C Controller may choose to replace the NACK with an ACK instead, which allows the read sequence to continue. This case will result in the transfer of contents (bits [15:8]) from the following register, address + 1. The controller can then continue acknowledging, issue the NACK, or stop after any byte to stop receiving data.

NOTE: Only the initial register address is required for reads, allowing for faster data retrieval. However, this restricts data retrieval to sequential registers when using a single read command. When the controller provides a NACK bit and a stop bit, the A31331 stops sending data. If nonsequential registers are to be read, separate read commands must be sent.

Figure 8: I<sup>2</sup>C Read Timing Diagram

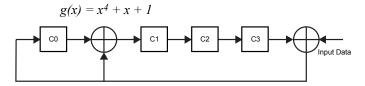

### I<sup>2</sup>C CRC Byte

To enable the A31331 cyclic redundancy check (CRC) feature, set the I2C\_CRC\_EN bit, indirect address 0x15, bit [18]. When enabled, the A31331 read transaction returns one extra byte, which corresponds to the CRC calculation of that read. The bytes of the I<sup>2</sup>C read sequence used for CRC calculation are:

- 1. 8-bit register address

- 2. 7-bit peripheral address + read bit (1'b1)

- 3. 2 data bytes (16 bits, MSB first)

The 8-bit-long code is generated using the CRC8-ATM (0x83) polynomial:

$$p(x) = x^8 + x^2 + x + 1$$

#### I<sup>2</sup>C Readback Modes

The A31331 supports three different readback modes over the I<sup>2</sup>C interface, including single, continuous, and loopback modes. These modes simplify the process of repeatedly polling the A31331 for magnetic X, Y, Z, and temperature data.

#### SINGLE MODE

In single mode, there is a single write or read command to any register. This is the default mode and is best suited for setting fields and reading static registers. If desired, this mode can be used to read data in a typical serial fashion, but fast or full-loop read modes are recommended for high-speed data retrieval. After each single read is complete, the controller must issue a NACK to complete the transaction.

#### **CONTINUOUS MODE**

Instead of issuing a NACK after a read request, the controller can continue to issue an ACK. When this occurs, the A31331 continues to transmit data from the next address, address + 2. This feature allows successive register reads without the need to send a read command for each register.

#### LOOPBACK MODE

Loopback mode on the A31331 is described in Table 6. The desired data to be returned serially in the loopback output register, I2C\_LOOP\_BACK\_16B, can be enabled by setting the appropriate bit(s) for I2C\_LOOPBACK\_CH\_SEL, direct address [0x34:0x35], bits [7:0]. In this mode, the desired data are loaded into the same read address sequentially. This allows continuous polling of a single register to obtain all of the necessary data. If a NACK is sent before the loopback sequence is complete, the loop restarts upon the next request.

Table 6: A31331 Looping Read Modes

| I2C_LOOPBACK_CH_SEL | Enabled Data in Loop |

|---------------------|----------------------|

| 0                   | X_CHANNEL_15B        |

| 1                   | Y_CHANNEL_15B        |

| 2                   | Z_CHANNEL_15B        |

| 3                   | TEMPERATURE_12B      |

| 4                   | SINE_15B             |

| 5                   | COSINE_15B           |

| 6                   | RADIUS_15B           |

| 7                   | ANGLE_15B            |

## I<sup>2</sup>C Addressing

The different addresses available to the A31331 are outlined in Table 7. In the special case where AD0 and AD1 are both tied to VCC, the device responds to the peripheral address stored in register I2C\_SLV\_ADDR in indirect-space address 0x15 (bits [16:10]). From the factory, this is set to 111, with the bit following the address indicating a read or write per the I<sup>2</sup>C specification.

NOTE: Different values for the three most significant bits (MSBs) of the address bits (A6, A5, and A4) are available for factory programming if a conflict with other units occurs in the application design.

4-Bit Code from ADR1 Voltage on AD1, Voltage on AD0, **Peripheral Address Bits** and ADR0 Voltages **Peripheral Address**  $V_{A1}$  (×  $V_{CC\_IO}$ )  $V_{A0}$  (×  $V_{CC\_IO}$ ) E2 **E**1 **E3** E0 A6 Α5 A0 Α4 А3 A2 Α1 0.33 0.67 O 0.33 0.33 0.67 O 0.33 0.67 0.67 0.33

Table 7: I<sup>2</sup>C Peripheral Address Decoding

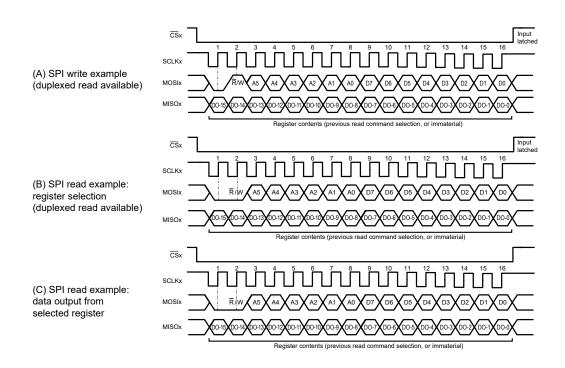

#### **SPI Protocol**

The A31331 provides a full-duplex 4-pin SPI interface for each die. The sensor responds to commands received on the corresponding controller-out peripheral-in (MOSI), serial clock (SCLK), and chip-select  $(\overline{CS})$  pins, and outputs data on the controller-in peripheral-out (MISO) pin. The A31331 supports SPI mode 3 (CPOL = 1, and CPHA = 1).

0.67

I2C\_SLV\_ADDR

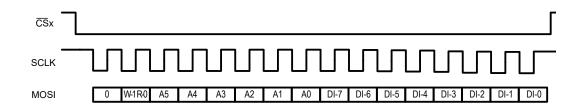

### **SPI Interface Timing**

The SPI interface operates in pure peripheral mode, with the controller governing the SCLK, MOSI, and  $\overline{\text{CS}}$  lines. Clock frequencies up to 10 MHz are supported. Timings of the write and read cycles are shown in Figure 4.

## **SPI Message Frame Size**

An SPI transaction is a minimum of 16 bits in length. An extended 20-bit SPI packet allows 4 bits of CRC to accompany every data packet. The 4-bit CRC is automatically generated and placed on the MISO line during clock pulses 17 through 20. The A31331 contains 16-bit primary-access registers that are byte-addressable to match the SPI frame size. To access the 32-bit EEPROM, an extended access scheme is implemented. This scheme consists of two 16-bit registers that contain the memory contents for a write,

two 16-bit registers that contain the memory contents for a read, and registers that contain the memory locations for the write, read, and execution control to begin and monitor the write/read.

Programmed to 111

at the factory

### **SPI Error Checking**

The SPI CRC algorithm is based on the following polynomial, initialized with 0xF:

Figure 9: SPI CRC

For the A31331 to accept the CRC on the MOSI line, the EEPROM parameter, SPI\_CRC\_EN, must be set to 1. If the incoming SPI message is greater than 16 bits and SPI\_CRC\_EN = 0, the message is ignored.

When enabled, the 4-bit CRC is expected. If the CRC is incorrect, the SPI packet is discarded. The MISO packet on the next message is the previous read data.

Figure 10: Sixteen-Bit SPI Message

Figure 11: Twenty-Bit SPI Message

## Write Cycle Overview

Write cycles consist of 1 synchronization (sync) bit (low), 1 read/write bit (R/W) asserted high, 6 address bits (corresponding to the primary serial register), 8 data bits, and 4 optional CRC bits. To write a full 16-bit serial register, two write commands are required (even and odd byte addresses). MOSI bits are clocked-in on the rising edge of the controller-generated SCLK signal. The complete SPI packet is latched on the rising edge of the controller-generated (CS) signal.

The simultaneous MISO signal output represents the contents of the corresponding die SPI read packet, including 16 data bits and 4 optional CRC bits. The data bits correspond to the register contents selected during the previous read command. If a previous read command was not issued (for instance, a write command), the MISO line transmits all zeroes as a return.

### **Read Cycle Overview**

Read cycles have two stages: a read command, selecting a serial register address, followed by another SPI command; it is during this second SPI command that data from the selected register is transmitted from the part to the host. Both commands consist of a 1-bit sync (low), a 1-bit R/W asserted low for a read, 6 address bits identifying the target register, and 8 data bits (these

are immaterial because data is not being written), followed by 4 optional CRC bits.

In the first stage, as with the write command, the read command MOSI bits are clocked-in on the rising edge of the controller-generated SCLK signal, and data are latched on the rising edge of the  $\overline{\text{CS}}$  signal. During the first read stage, the simultaneous MISO signal output is composed of either the contents of the SPI read data from a previous read command cycle, or the contents of the angle register if the previous command was a write.

In the second stage, the read command continues on the next falling edge of the controller-generated  $(\overline{CS})$  signal. The MISO bits are the contents of the register selected during the first stage, read 16 bits at a time. The MISO bits transmit on the falling edges of the SCLK signal, such that the controller can sample them on the SCLK rising edges.

Because an SPI read command can transmit 16 data bits at one time, and the primary serial registers are built from one even and one odd byte, the entire 16-bit contents of one serial register can be transmitted with one SPI frame.

Examples of both an SPI write and an SPI read request using a 16-bit SPI message frame are shown in Figure 12.

Figure 12: SPI Read and Write Pulse Sequences

## **EEPROM Margin Checking**

The A31331 contains a test mode, known as EEPROM margining, to check the logic levels of the EEPROM bit cells. Due to nonidealities in transistors, current slowly leaks into or out of EEPROM cells and can, over time, cause small changes in the stored voltage level. During programming, variances in voltage levels of the charge pump can result in a variety of stored EEPROM cell voltages. If this value is marginally close to the threshold, the small drift over lifetime can cause this value to surpass the threshold. This results in a corrupted EEPROM value. Because this drift occurs slowly over time, if an issue arises, it might not appear for years. For this reason, it is important to perform margin testing (margining) to verify the internal voltage levels of EEPROM cells after programming and to ensure that issues do not occur in the future.

This test should be run after writing to the EEPROM to ensure the bit cell thresholds are within the specification for reliable EEPROM operation. To perform the test, set the volatile MARGIN\_START bit. Once set, the device enters the test mode where all bit cells within the EEPROM array are checked. The EEPROM margining is selectable to check all logic 1 thresholds (can be disabled by MARGIN\_NO\_MAX), logic 0 thresholds (can be disabled by MARGIN\_NO\_MIN), or both thresholds.

**Table 8: Margin Status Return Decoding**

| MARGIN_STATUS | Meaning                                                    |

|---------------|------------------------------------------------------------|

| 0             | Reset condition (result from margin testing not available) |

| 1             | Pass: Failure not detected during margin testing           |

| 2             | Fail: Failure detected during margin testing               |

| 3             | Running: Margin test is still running                      |

The EEPROM margin test spans 1 ms (typical). After the EEPROM margin test completes, the status can be read out via the MARGIN\_STATUS bit in the volatile space. The best practice is to perform EEPROM margin checking after end-of-line programming.

#### **MEMORY ACCESS**

The A31331 uses a primary and extended memory structure. The device uses EEPROM to permanently store configuration parameters for operation. EEPROM is user-programmable and permanently stores operation parameter values or customer information. The operation parameters are downloaded to shadow (volatile) memory at power-up. Shadow fields are initially loaded from corresponding fields in EEPROM, but can be overwritten, either by performing an extended write to the shadow addresses, or by reprogramming the corresponding EEPROM fields and powercycling the IC. Use of shadow memory is substantially faster than accessing EEPROM. In situations where many parameters need to be tested quickly, shadow memory is recommended for trying parameter values before permanently programming them into EEPROM. The shadow memory registers have the same format as the EEPROM and are accessed at extended addresses 0x20 higher than the equivalent EEPROM address. Unused bits in the EEPROM do not exist in the related shadow register and return 0 when read. Shadow registers do not contain the ECC bits. The serial interface primary access registers can be read or written to without the customer access code. The mapping of bits from register addresses in EEPROM to their corresponding register addresses in shadow is shown in the EEPROM tables in the Indirect Extended Space section. The access register is used to unlock the device. The access code must be written to ACCESS KEY [15:0] one byte at a time. Once unlocked, EEPROM and shadow registers can be written.

Extended access is provided to additional memory space via the primary registers. This access includes the EEPROM, shadow registers, and registers for additional status and diagnostics. All extended registers are 32 bits wide.

#### **Customer Access Modes**

The device memory contains nonvolatile EEPROM and volatile registers that are accessible via the serial interface through SPI or I<sup>2</sup>C communication mode. The memory address space is divided into three areas: factory, customer, and general access.

Customer access is controlled by an access code shown in Table 9. The access codes contain 32 bits.

To send the access codes shown in Table 9, the user writes to the access register with four consecutive 8-bit writes.

When the customer access code is received, factory registers are addressable but are read-only.

**Table 9: 32-bit Customer Access Code**

|                                | Byte 1 | Byte 2 | Byte 3 | Byte 4 |

|--------------------------------|--------|--------|--------|--------|

| Customer (Read access to fact) | 43     | 55     | 53     | 54     |

# Read Transaction from EEPROM (or Shadow Memory)

To invoke an extended read access:

- Load the INDIRECT\_RD\_ADDR parameter with the target extended address. INDIRECT\_RD\_ADDR is the 8-bit extended address that determines which extended memory address is to be accessed.

- Invoke the extended access by writing the primary INDI-RECT\_RD\_STATUS register EXR bit with 1. The INDI-RECT\_RD\_ADDR address is then read, and the data is loaded into the INDIRECT\_RD\_DATA\_MSB and INDI-RECT\_RD\_DATA\_LSB registers.

- 3. Read the INDIRECT\_RD\_DATA\_MSB and INDIRECT\_ RD\_DATA\_LSB registers to obtain the extended data. Multiple packets are required to obtain all 32 bits.

The RDN bit in the INDIRECT\_RD\_STATUS register can be polled to determine if the read access is complete before reading the data. Shadow register reads complete in one system clock cycle after synchronization. Do not attempt to read the INDIRECT\_RD\_DATA\_MSB or INDIRECT\_RD\_DATA\_LSB register when read access is in progress. If the read access is potentially in progress, the data might change during serial access. Therefore, an attempt to read these registers when read access is in progress can result in inconsistent data. A data change during a serial read via the SPI interface can also produce an SPI CRC error.

For example, to read location 0x15 in the EEPROM:

- Write 0x15 to the lower 8 bits of INDIRECT\_RD\_ADDR (0x15 to address 0x0B).

- Write 0x80 to the upper 8 bits of INDIRECT\_RD\_STATUS to set the EXR bit (0x80 to address 0x0C).

- Read INDIRECT\_RD\_STATUS until bit 0 (RDN) is set (or until sufficient time elapses).

- Read INDIRECT\_RD\_DATA\_MSB (upper 16 bits of read data).

- Read INDIRECT\_RD\_DATA\_LSB (lower 16 bits of read data).

## A31331

## 3D Linear Hall-Effect Sensor

## with SPI, I<sup>2</sup>C Interfaces, and Advanced Low-Power Management

# Write Transaction to EEPROM (or Shadow Memory)

An extended write access can be invoked as follows:

- Load the INDIRECT\_WR\_ADDR parameter with the target extended address.

- 2. Load the INDIRECT\_WR\_DATA\_MSB and INDIRECT\_WR\_DATA\_LSB registers with the data to be written to the target. Multiple writes are required to load all 32 bits of data.

- 3. Invoke the extended access by writing the primary INDI-RECT WR STATUS register EXW bit with 1.

The INDIRECT\_WR\_ADDR address is then written with the 32-bit INDIRECT\_WR\_DATA\_MSB and INDIRECT\_WR\_DATA\_LSB data. The WDN bit in the INDIRECT\_WR\_STATUS register can be polled to determine when the write completes.

#### **Shadow Memory Read and Write Transactions**

Read and write transactions for shadow memory are nearly identical to those for EEPROM: Instead of addressing to the EEPROM addresses, the shadow extended addresses must be addressed; these are located at an offset of 0x20 higher than the EEPROM.

### **Shared Factory and Customer Trim Registers**

Register addresses [0x07:0x12] contain memory used to factory-trim the device for the highest sensing accuracy in any application where the input vectors match in amplitude. If the application requires additional end-of-line adjustments to the device trim, these registers can be adjusted by the customer.

NOTE: The customer must ensure the accuracy of the device after end-of-line programming.

### **Memory Access in Low-Power Modes**

When in sleep mode or low-power duty cycle mode, OP\_MODE = 3 through 6, read/write access is limited to critical registers. This helps conserve power. Only the subset of direct-space registers needed to use the part in typical operation is available. Writes are only possible to direct-space addresses [0x32:0x33] that contain device configuration parameters. For reads, direct-space addresses [0x12:0x2B] and [0x32:0x33] are available in the I<sup>2</sup>C interface, and [0x1C:0x2A] and [0x32:0x33] are available in the SPI interface. For more information about the contents of these registers, see the Memory Map section.

## with SPI, I<sup>2</sup>C Interfaces, and Advanced Low-Power Management

#### **MEMORY MAP**

The A31331 uses a primary and extended memory structure designated as direct (primary) and indirect (extended) space.

### **Direct Primary Space**

**Table 10: Direct Memory Map**

| MSByte       | LSByte       | Register                     |                     |                    |    | MSI | Byte |    |     |            |            |      |   | LSI | Byte |   |   |   |

|--------------|--------------|------------------------------|---------------------|--------------------|----|-----|------|----|-----|------------|------------|------|---|-----|------|---|---|---|

| Address      | Address      | Name                         | 15                  | 14                 | 13 | 12  | 11   | 10 | 9   | 8          | 7          | 6    | 5 | 4   | 3    | 2 | 1 | 0 |

| 0x0          | 0x1          | NOP_REGISTER                 | 0                   | 0                  | 0  | 0   | 0    | 0  | 0   | 0          | 0          | 0    | 0 | 0   | 0    | 0 | 0 | 0 |

| 0x2 to 0x8   | 0x3 to 0x9   | INDIRECT_WRITE_<br>REGISTERS |                     |                    |    |     |      |    | Ind | lirect Wri | te Regist  | ters |   |     |      |   |   |   |