## **Discontinued Product**

These parts are no longer in production The device should not be purchased for new design applications. Samples are no longer available.

Date of status change: September 30, 2024

### **Recommended Substitutions:**

For existing customer transition, and for new customers or new applications, refer to the AMT49413GEVATR.

NOTE: For detailed information on purchasing options, contact your local Allegro field applications engineer or sales representative.

Allegro MicroSystems reserves the right to make, from time to time, revisions to the anticipated product life cycle plan for a product to accommodate changes in production capabilities, alternative product availabilities, or market demand. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

#### **FEATURES AND BENEFITS**

- Drives 6 N-channel MOSFETs

- Synchronous rectification for low power dissipation

- Internal UVLO and thermal shutdown circuitry

- Hall element inputs

- PWM current limiting

- Dead time protection

- FG outputs

- Standby mode

- Lock detect protection

- Overvoltage protection

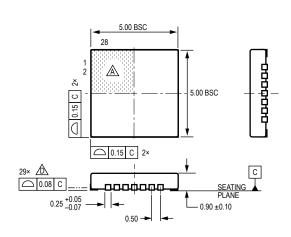

### PACKAGE: 28-contact QFN (ET package)

#### **DESCRIPTION**

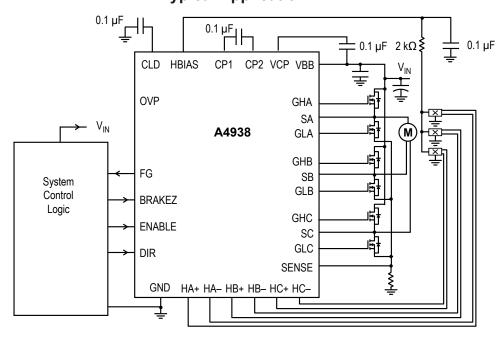

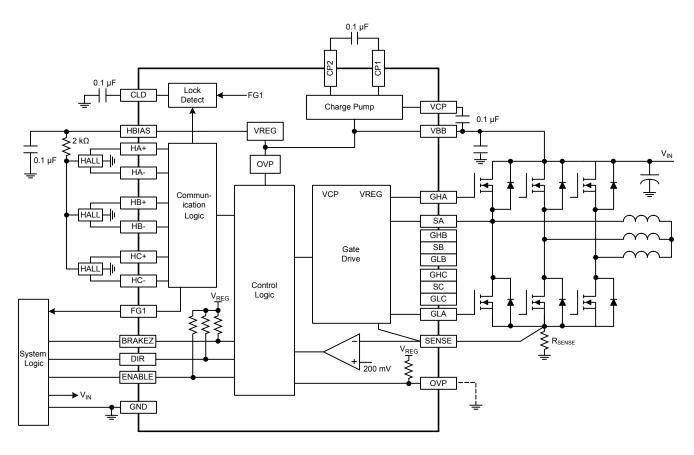

The A4938 is a complete 3-phase brushless DC (BLDC) motor pre-driver, supplying direct, high-current gate drive of an all N-channel power MOSFET 3-phase bridge. The device has three Hall-element inputs, a sequencer for commutation control, fixed off-time pulse width modulation (PWM) current control, and locked-rotor detection.

Output current is scaled by the capability of the external MOSFETs. Locked rotor detection delay is set by an external capacitor on the CLD terminal. The ENABLE, DIR, and BRAKEZ inputs can be used to control motor speed, position, and torque. Motor speed can be determined using the FG1 output.

The external MOSFETS can be PWMed using an external signal on the PWM input or using the internal PWM current regulator. In either case, the A4938 synchronous rectification feature reduces power dissipation by turning on the appropriate MOSFETs during current decay.

The Hall elements can be inexpensive types, when used with noise filtering to prevent false commutation signals. The A4938 provides a regulated 5.0 V supply to power the three Hall elements. Internal circuit protection includes thermal shutdown with hysteresis, undervoltage lockout, and dead time

Continued on the next page...

### **Typical Application**

## 3-Phase Brushless DC Motor Pre-Driver

### **DESCRIPTION** (continued)

protection. Special power-up sequencing is not required. Operating temperature range is -40°C to 85°C.

The A4938 is supplied in a 5 mm  $\times$  5 mm, 28-terminal QFN package with exposed thermal pad. This small footprint package is lead (Pb) free with 100% matte tin leadframe plating.

### **SELECTION GUIDE**

| Part Number  | Packing              | Package                                 |

|--------------|----------------------|-----------------------------------------|

| A4938EETTR-T | 1500 pieces per reel | 5 mm x 5 mm, 0.90 mm nominal height QFN |

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristics               | Symbol                            | Notes   | Rating     | Unit |

|-------------------------------|-----------------------------------|---------|------------|------|

| Load Supply Voltage           | V <sub>BB</sub>                   |         | 38         | V    |

| Motor Phase Output            | Motor Phase Output S <sub>X</sub> |         | -3         | V    |

| Hall Input                    | V <sub>Hx</sub>                   | DC      | -0.3 to 7  | V    |

| Logic Input Voltage Range     | V <sub>IN</sub>                   |         | -0.3 to 7  | V    |

| Operating Ambient Temperature | T <sub>A</sub>                    | Range E | -40 to 85  | °C   |

| Maximum Junction Temperature  | T <sub>J</sub> (max)              |         | 150        | °C   |

| Storage Temperature           | T <sub>stg</sub>                  |         | -40 to 150 | °C   |

#### THERMAL CHARACTERISTICS

| Characteristics Symbol                                                |                | Test Conditions*                    | Rating | Unit |

|-----------------------------------------------------------------------|----------------|-------------------------------------|--------|------|

| Package Thermal Resistance, Junction to Ambient                       | $R_{	heta JA}$ | 4-layer PCB based on JEDEC standard | 32     | °C/W |

| Package Thermal Resistance, Junction to Exposed Pad $$R_{\theta JP}$$ |                |                                     | 2      | °C/W |

<sup>\*</sup>For additional information, refer to the Allegro website.

### **FUNCTIONAL BLOCK DIAGRAM**

### **Terminal List**

| Number | Name  | Description                    |

|--------|-------|--------------------------------|

| 1      | HA+   | Hall input A                   |

| 2      | HA -  | Hall input A                   |

| 3      | HB+   | Hall input B                   |

| 4      | HB -  | Hall input B                   |

| 5      | HC+   | Hall input C                   |

| 6      | HC-   | Hall input C                   |

| 7      | GND   | Ground                         |

| 8      | HBIAS | Hall bias power supply output  |

| 9      | CP1   | Charge pump capacitor terminal |

| 10     | CP2   | Charge pump capacitor terminal |

| 11     | VBB   | Supply voltage                 |

| 12     | VCP   | Reservoir capacitor terminal   |

| 13     | SENSE | Sense resistor connection      |

| 14     | GLC   | Low side gate drive C          |

| Number | Name   | Description                            |

|--------|--------|----------------------------------------|

| 15     | GLB    | Low side gate drive B                  |

| 16     | GLA    | Low side gate drive A                  |

| 17     | GHC    | High side gate drive C                 |

| 18     | SC     | High side source connection C          |

| 19     | GHB    | High side gate drive B                 |

| 20     | SB     | High side source connection B          |

| 21     | GHA    | High side gate drive A                 |

| 22     | SA     | High side source connection A          |

| 23     | FG1    | FG 1 output                            |

| 24     | OVP    | Logic input – OVP selection            |

| 25     | CLD    | Locked rotor detect timing capacitor   |

| 26     | DIR    | Logic input – motor direction          |

| 27     | ENABLE | Logic input – external PWM control     |

| 28     | BRAKEZ | Logic input – motor brake (active low) |

## 3-Phase Brushless DC Motor Pre-Driver

### **ELECTRICAL CHARACTERISTICS**\*: Valid at $T_A$ = 25°C, $V_{BB}$ = 24 V, unless noted otherwise

| Characteristics                        | Symbol                | Test Conditions                                        | Min. | Тур. | Max. | Unit |

|----------------------------------------|-----------------------|--------------------------------------------------------|------|------|------|------|

| Supply Voltage Range                   | V <sub>BB</sub>       | Operating                                              | 8.5  | _    | 30   | V    |

| Matan Cumulu Cumant                    |                       | f <sub>PWM</sub> < 30 kHz, C <sub>LOAD</sub> = 1000 pF | _    | 5    | 6    | mA   |

| Motor Supply Current                   | I <sub>BB</sub>       | Charge pump on, outputs disabled, Standby mode         | _    | 2.4  | 3.2  | mA   |

| HBIAS                                  | V <sub>HBIAS</sub>    | 0 mA ≤ I <sub>HBIAS</sub> ≤ 24 mA                      | 4.7  | 5.0  | 5.3  | V    |

| HBIAS Current Limit                    | I <sub>HBIASlim</sub> |                                                        | 35   | -    | _    | mA   |

| CONTROL LOGIC                          |                       |                                                        | ·    |      |      |      |

| Logio Input Voltago                    | V <sub>IN(1)</sub>    |                                                        | 2    | _    | _    | V    |

| Logic Input Voltage                    | V <sub>IN(0)</sub>    |                                                        | _    | _    | 0.8  | V    |

| Lasia Inguit Dull Ha                   |                       | OVP pin pull-up to HBIAS                               | _    | 100  | _    | kΩ   |

| Logic Input Pull-Up                    | R <sub>IN(PU)</sub>   | ENABLE, BRAKEZ, DIR pins pull-up to HBIAS              | _    | 50   | _    | kΩ   |

| Innuit Din Clitale Dais at             |                       | ENABLE pin                                             | 350  | 500  | 650  | ns   |

| Input Pin Glitch Reject                | t <sub>GLITCH</sub>   | DIR, BRAKEZ pins                                       | 700  | 1000 | 1300 | ns   |

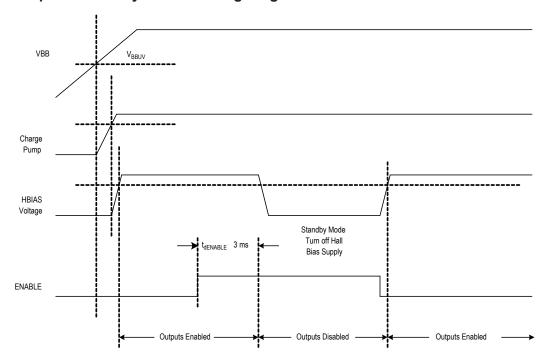

| ENABLE Standby Pulse Propagation Delay | t <sub>dENABLE</sub>  | t <sub>dENABLE</sub> To outputs off                    |      | 3    | 3.9  | ms   |

| HBIAS Wake-up Delay, Standby Mode      | t <sub>dHBIAS</sub>   | C <sub>HBIAS</sub> = 0.1 µF                            | _    | 15   | 25   | μs   |

| GATE DRIVE                             | `                     |                                                        |      |      |      |      |

| High-Side Gate Drive Output            | V <sub>GS(H)</sub>    | Relative to V <sub>BB</sub> , I <sub>GATE</sub> = 2 mA | 7    | _    | _    | V    |

| Low-Side Gate Drive Output             | V <sub>GS(L)</sub>    | I <sub>GATE</sub> = 2 mA                               | 4.5  | -    | _    | V    |

| Gate Drive Current (Sourcing)          | I <sub>Gate</sub>     | GH = GL = 4 V                                          | 20   | 30   | _    | mA   |

| Gate Drive Pull Down Resistance        | R <sub>Gate</sub>     |                                                        | 10   | 28   | 40   | Ω    |

| Dead Time                              | t <sub>dead</sub>     |                                                        | 700  | 1000 | 1300 | ns   |

| Current Limit Input Threshold          | V <sub>REF</sub>      |                                                        | 180  | 200  | 220  | mV   |

| Fixed Off-Time                         | t <sub>OFF</sub>      |                                                        | 18   | 25   | 37   | μs   |

| PROTECTION                             |                       |                                                        |      |      |      |      |

| Thermal Shutdown Temperature           | T <sub>JTSD</sub>     |                                                        | 155  | 170  | 185  | °C   |

| Thermal Shutdown Hysteresis            | T <sub>JTSDhys</sub>  |                                                        | _    | 20   | _    | °C   |

| VBB UVLO Enable Threshold              | V <sub>BBUV</sub>     | Rising V <sub>BB</sub>                                 | 6.20 | 7    | 7.85 | V    |

| VBB UVLO Hysteresis                    | V <sub>BBUVhys</sub>  |                                                        | 0.4  | 0.75 | 1    | V    |

| VCP UVLO                               | V <sub>CPUV</sub>     | Relative to V <sub>BB</sub>                            | 4.6  | _    | 6    | V    |

| Lock Detect Duration                   | t <sub>lock</sub>     | C = 0.1 µF                                             | 1.5  | 2    | 2.5  | s    |

| VPP Overvoltage Throubald              | \/                    | OVP = GND, V <sub>BB</sub> rising                      | 15.5 | 16   | 16.5 | V    |

| VBB Overvoltage Threshold              | V <sub>BBOV</sub>     | OVP = open, V <sub>BB</sub> rising                     | 28.5 | 29   | 29.5 | V    |

| VBB Overvoltage Hysteresis             | V <sub>OVOhys</sub>   |                                                        | _    | 2    | _    | V    |

Continued on the next page...

## 3-Phase Brushless DC Motor Pre-Driver

### **ELECTRICAL CHARACTERISTICS**\* (continued): Valid at T<sub>A</sub>= 25°C, V<sub>BB</sub> = 24 V, unless noted otherwise

| Characteristics              | Symbol                                | Test Conditions                                     | Min. | Тур. | Max. | Unit              |

|------------------------------|---------------------------------------|-----------------------------------------------------|------|------|------|-------------------|

| HALL LOGIC                   |                                       |                                                     |      |      |      |                   |

| Hall Input Current           | I <sub>HALL</sub>                     | V <sub>IN</sub> = 0.2 to 3.5 V                      | -1   | 0    | 1    | μA                |

| Common Mode Input Range      | V <sub>CMR</sub>                      |                                                     | 0.2  | _    | 2.0  | V                 |

| AC Input Voltage Range       | V <sub>HALL</sub>                     |                                                     | 60   | -    | -    | mV <sub>p-p</sub> |

| Hall Thresholds              | $V_{th}$                              | Difference between Hall inputs at transitions       | -    | ±10  | _    | mV                |

| Hall Three hald Hustanasia   | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | T <sub>J</sub> = 25°C                               | 10   | 20   | 30   | mV                |

| Hall Threshold Hysteresis    | V <sub>HYS</sub>                      | $T_J = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ | 5    | 20   | 40   | mV                |

| Pulse Reject Filter          | t <sub>pulse</sub>                    |                                                     | _    | 2    | _    | μs                |

| FG                           | '                                     |                                                     |      |      |      |                   |

| FG Output Saturation Voltage | V <sub>FG(sat)</sub>                  | I <sub>FG</sub> = 2 mA                              | _    | _    | 0.5  | V                 |

| FG Leakage Current           | I <sub>FGlkg</sub>                    | V <sub>FG</sub> = 5 V                               | _    | _    | 1    | μA                |

<sup>\*</sup>Typical data are for initial design estimations only and assume optimum manufacturing and application conditions. Performance may vary for individual units, within the specified maximum and minimum limits.

For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device pin.

Specifications throughout the allowed operating temperature range are guaranteed by design and characterization.

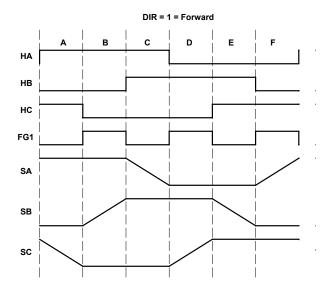

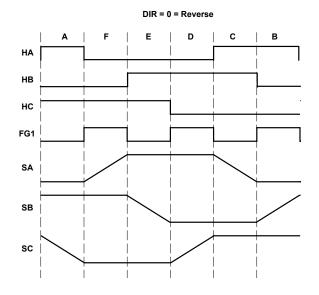

**Logic States Table** (See timing charts, below) X = Don't Care (can be 1 or 0), Z = high impedance

| Condition |   |    |    |    | In  | puts   |                          |     | Resulti | ng Pre- | Driver C | Outputs |     | Motor Output |    |    |

|-----------|---|----|----|----|-----|--------|--------------------------|-----|---------|---------|----------|---------|-----|--------------|----|----|

| Conditio  | n | НА | НВ | нс | DIR | BRAKEZ | ENABLE                   | GHA | GLA     | GHB     | GLB      | GHC     | GLC | Α            | В  | С  |

|           | Α | +  | -  | +  | 1   | 1      | 0                        | HI  | LO      | LO      | HI       | LO      | LO  | HI           | LO | Z  |

|           | В | +  | -  | -  | 1   | 1      | 0                        | HI  | LO      | LO      | LO       | LO      | HI  | HI           | Z  | LO |

| Forward   | С | +  | +  | -  | 1   | 1      | 0                        | LO  | LO      | HI      | LO       | LO      | HI  | Z            | HI | LO |

| Forward   | D | _  | +  | -  | 1   | 1      | 0                        | LO  | HI      | HI      | LO       | LO      | LO  | LO           | HI | Z  |

|           | Е | _  | +  | +  | 1   | 1      | 0                        | LO  | HI      | LO      | LO       | HI      | LO  | LO           | Z  | HI |

|           | F | _  | -  | +  | 1   | 1      | 0                        | LO  | LO      | LO      | HI       | НІ      | LO  | Z            | LO | HI |

|           | Α | +  | -  | +  | 0   | 1      | 0                        | LO  | HI      | HI      | LO       | LO      | LO  | LO           | HI | Z  |

|           | F | +  | -  | -  | 0   | 1      | 0                        | LO  | HI      | LO      | LO       | HI      | LO  | LO           | Z  | HI |

| Reverse   | Е | +  | +  | -  | 0   | 1      | 0                        | LO  | LO      | LO      | HI       | HI      | LO  | Z            | LO | HI |

| Reveise   | D | _  | +  | -  | 0   | 1      | 0                        | HI  | LO      | LO      | HI       | LO      | LO  | HI           | LO | Z  |

|           | С | _  | +  | +  | 0   | 1      | 0                        | HI  | LO      | LO      | LO       | LO      | HI  | HI           | Z  | LO |

|           | В | _  | _  | +  | 0   | 1      | 0                        | LO  | LO      | HI      | LO       | LO      | HI  | Z            | HI | LO |

|           | Α | +  | -  | +  | Χ   | 1      | If 1 for <3 ms           | LO  | HI      | LO      | HI       | LO      | LO  | LO           | LO | Z  |

|           | F | +  | -  | -  | Χ   | 1      | If 1 for <3 ms           | LO  | HI      | LO      | LO       | LO      | HI  | LO           | Z  | LO |

| Chop      | E | +  | +  | -  | Χ   | 1      | If 1 for <3 ms           | LO  | LO      | LO      | HI       | LO      | HI  | Z            | LO | LO |

| Спор      | D | _  | +  | -  | Χ   | 1      | If 1 for <3 ms           | LO  | HI      | LO      | HI       | LO      | LO  | LO           | LO | Z  |

|           | С | _  | +  | +  | Χ   | 1      | If 1 for <3 ms           | LO  | HI      | LO      | LO       | LO      | HI  | LO           | Z  | LO |

|           | В | _  | _  | +  | Χ   | 1      | If 1 for <3 ms           | LO  | LO      | LO      | HI       | LO      | HI  | Z            | LO | LO |

| Fault     |   | _  | -  | -  | Χ   | Χ      | X                        | LO  | LO      | LO      | LO       | LO      | LO  | Z            | Z  | Z  |

| ı ault    |   | +  | +  | +  | X   | Χ      | X                        | LO  | LO      | LO      | LO       | LO      | LO  | Z            | Z  | Z  |

| Brake     |   | Х  | Χ  | Х  | Х   | 0      | If 0, or if 1 for < 3 ms | LO  | НІ      | LO      | HI       | LO      | НІ  | LO           | LO | LO |

| Standby   | / | Х  | Х  | Χ  | Х   | Χ      | If 1 for >3 ms           | LO  | LO      | LO      | LO       | LO      | LO  | Z            | Z  | Z  |

### Power-Up and Standby Modes Timing Diagram

### **Power-Up and Standby Modes Timing Diagram**

#### **FUNCTIONAL DESCRIPTION**

**Current Regulation.** Load current is regulated by an internal fixed off-time PWM control circuit. When the outputs of the full bridge are turned on, current increases in the motor winding until it reaches a value, I<sub>TRIP</sub>, given by:

$$I_{\text{TRIP}} = 200 \text{ mV} / R_{\text{SENSE}}$$

.

When  $I_{TRIP}$  is reached, the sense comparator resets the source enable latch, turning off the source driver. At this point, load inductance causes the current to recirculate for the fixed off-time period.

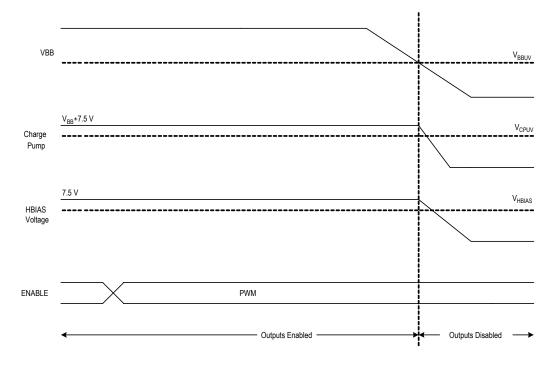

**Enable Logic.** The ENABLE pin allows external PWM. ENABLE low turns on the selected sink-source pair. ENABLE high switches off the appropriate drivers and the load current decays. If ENABLE is held low, the current will rise until it reaches the level set by the internal current control circuit. Typically, PWM frequency is in the 20 to 30 kHz range. If the ENABLE high pulse width exceeds 3 ms, the gate outputs are disabled. The Enable logic is summarized in the following table:

| ENABLE P        | in Outputs     | Outputs State                                   |

|-----------------|----------------|-------------------------------------------------|

| 0               | On             | Drive                                           |

| 1               | Source chopped | Slow decay with<br>synchronous<br>rectification |

| 1 for > 3 ms ty | pical Off      | Disable                                         |

**Fixed Off-Time.** The A4938 fixed off-time is set to 25  $\mu$ s nominal.

**PWM Blank Timer.** When a source driver turns on, a current spike occurs due to the reverse recovery currents of the clamp diodes and/or switching transients related to distributed capacitance in the load. To prevent this current spike from erroneously resetting the source Enable latch, the sense comparator is blanked. The blanking timer runs after the off-time counter, to

provide the blanking function. The blanking timer is reset when ENABLE is chopped or DIR is changed. For external PWM control, a DIR change or an ENABLE on triggers the blanking function. The duration is fixed at 1.5 µs.

**Synchronous Rectification.** When a PWM-off cycle is triggered, either by an ENABLE chop command or by an internal fixed off-time cycle, load current recirculates. The A4938 synchronous rectification feature turns on the appropriate MOSFETs during the current decay, and effectively shorts out the body diodes with the low  $R_{\rm DS(on)}$  driver. This lowers power dissipation significantly and can eliminate the need for external Schottky diodes.

**Brake Mode.** A logic low on the BRAKEZ pin activates Brake mode. A logic high allows normal operation. Braking turns on all three sink drivers, effectively shorting out the motor-generated BEMF. The BRAKEZ input overrides the ENABLE input and the Lock Detect function.

It is important to note that the internal PWM current control circuit does not limit the current when braking, because the current does not flow through the sense resistor. The maximum current can be approximated by  $V_{BEMF}/\,R_{LOAD}.$  Care should be taken to ensure that the maximum ratings of the A4938 are not exceeded in the worse case braking situation: high speed and high inertial load.

**HBIAS Function.** This function provides a power supply of 5.0 V, current-limited to 35 mA. This reference voltage is used to power the logic sections of the A4938 and also to power the external Hall elements.

**Standby Mode.** To prevent excessive power dissipation due to the current draw of the external Hall elements, Standby mode turns off the HBIAS output voltage. Standby mode is triggered by

## 3-Phase Brushless DC Motor Pre-Driver

holding ENABLE high for longer than 3 ms. Note that the state of BRAKEZ does not affect Standby mode.

**Charge Pump.** The internal charge pump is used to generate a supply above  $V_{BB}$  to drive the high-side MOSFETs. The voltage on the VCP pin is internally monitored, and in the case of a fault condition, the outputs of the device are disabled.

**Fault Shutdown.** In the event of a fault due to excessive junction temperature, or due to low voltage on VCP or VBB, the outputs of the device are disabled until the fault condition is removed. At power-up the UVLO circuit disables the drivers.

**Overvoltage Protection.** VBB is monitored to determine if a hazardous voltage is present due to the motor generator pumping-up the supply bus. When the voltage exceeds  $V_{BBOV}$ , the synchronous rectification feature is disabled. Connecting OVP to GND sets  $V_{BBOV}$  to 16 V typically and leaving OVP open sets  $V_{BBOV}$  to 29 V typically.

**Overtemperature Protection.** If die temperature exceeds approximately 170°C, the Thermal Shutdown function will disable the outputs until the internal temperature falls below the threshold hysteresis.

**Hall State Reporting.** The FG1 pin is an open drain output that changes state at each transition of an external Hall element.

**Lock Detect Function.** The IC will evaluate a locked rotor condition under either of these two different conditions:

- The FG1 signal is not consistently changing.

- The proper commutation sequence is not being followed. The motor can be locked in a condition in which it toggles between two specific Hall device states.

Both of these fault conditions are allowed to persist for a period of time,  $t_{lock}$ . The value of  $t_{lock}$  is set by capacitor connected to the CLD pin.  $C_{LD}$  produces a triangle waveform (1.67 V peak-topeak) with a frequency linearly related to the capacitor value.  $t_{lock}$  is defined as 127 cycles of this triangle waveform, or:

$$t_{\text{lock}} = C_{\text{LD}} \times 20 \text{ s/}\mu\text{F}$$

After the wait time,  $t_{lock}$ , has expired, the outputs are disabled, and the fault is latched.

These fault conditions are latched and can only be cleared by any one of the following actions:

- Rising or falling edge on the DIR pin

- VBB UVLO threshold exceeded (during power-up cycle)

- ENABLE pin held high for  $> t_{lock} / 2$

The Lock Detect function can be disabled by connecting CLD to GND.

When the A4938 is in Brake mode, the Lock Detect counter is disabled.

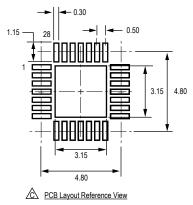

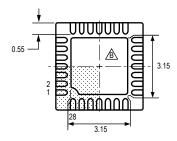

### ET Package, 28-Contact QFN

XXXX  ${\mathcal A}$  Date Code Lot Number

Line 3: Characters 5, 6, 7, 8 of Assembly Lot Number

For Reference Only; not for tooling use (reference DWG-0000378, Rev. 3) Dimensions in millimeters Exact case and lead configuration at supplier discretion within limits shown

Exposed thermal pad (reference only, terminal #1 identifier appearance at supplier discretion)

Reference land pattern layout (reference IPC7351 QFN50P500X500X100-29V1M);

All pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to meet application process requirements and PCB layout tolerances; when mounting on a multilayer PCB, thermal vias at the exposed thermal pad land can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

Coplanarity includes exposed thermal pad and terminals

A Branding scale and appearance at supplier discretion

## 3-Phase Brushless DC Motor Pre-Driver

#### **Revision History**

| Number | Date               | Description                             |

|--------|--------------------|-----------------------------------------|

| 1      | February 13, 2020  | Minor editorial updates                 |

| 2      | February 10, 2022  | Updated package drawing (page 10)       |

| 3      | March 18, 2024     | Updated product status to Last-Time Buy |

| 4      | September 13, 2024 | Updated product status to Discontinued  |

Copyright 2024, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com