## **Three-Phase Fan Driver**

#### **FEATURES AND BENEFITS**

- 180° sinusoidal drive

- · PWM speed input

- · Analog speed input

- FG speed output

- Lock detection

- Overcurrent protection

- Short circuit protection

- Wide power supply range

- · Soft start

#### **PACKAGE**

16-pin TSSOP with exposed thermal pad (LP package)

Not to scale

#### **DESCRIPTION**

The A4944 three-phase motor driver incorporates sinusoidal control to minimize audible noise and vibration as well as to provide highly efficient operation of appliance or personal computer (PC) fans.

Pulse-width modulation (PWM) or analog voltage input can be used to control motor speed. This allows system cost savings by eliminating external variable power supply. Alternatively, the speed can be controlled by varying power supply amplitude over a wide range (4 to 17 V).

A soft-start circuit reduces the demand on the power supply at startup. When the motor is forced to a stop by a rotor lock condition, a lock-detection circuit, which does not require external components, disables the output driver.

The A4944 is supplied in a low-profile 16-pin thin-shrink small-outline package (TSSOP) with exposed thermal pad (suffix LP). The package is lead (Pb) free with 100% matte tin leadframe plating.

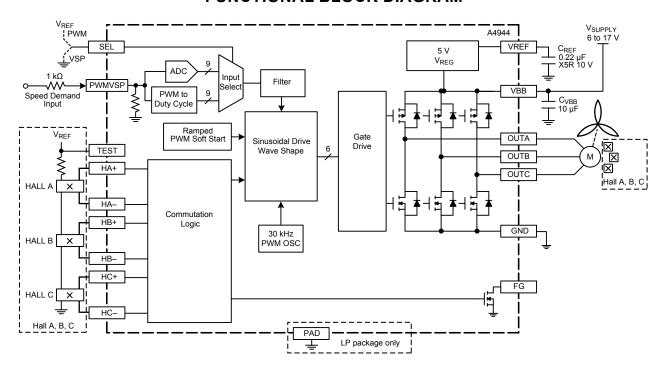

#### **FUNCTIONAL BLOCK DIAGRAM**

## **SELECTION GUIDE**

| Part Number  | Packing                      | Package                               |

|--------------|------------------------------|---------------------------------------|

| A4944GLPTR-T | 4000 pieces per 13-inch reel | 16-pin TSSOP with exposed thermal pad |

## **ABSOLUTE MAXIMUM RATINGS**

| Characteristic                | Symbol               | Notes               | Rating             | Unit |

|-------------------------------|----------------------|---------------------|--------------------|------|

| Supply Voltage                | V <sub>BB</sub>      |                     | 18                 | V    |

| Logic Input Voltage Range     | V <sub>IN</sub>      | PWMVSP and SEL pins | -0.3 to 6          | V    |

| Logic Output                  | Vo                   | FG pin              | V <sub>BB</sub>    | V    |

| Output Current                | I <sub>OUT</sub>     |                     | 1.2                | Α    |

| Hall Inputs                   | V <sub>Hx</sub>      |                     | 6                  | V    |

| Output Voltage                | V <sub>OUT</sub>     |                     | V <sub>BB</sub> +1 | V    |

| Reference Voltage             | V <sub>REF</sub>     |                     | 5.5                | V    |

| Operating Ambient Temperature | T <sub>A</sub>       | G temperature range | -40 to 105         | °C   |

| Maximum Junction Temperature  | T <sub>J</sub> (max) |                     | 150                | °C   |

| Storage Temperature           | T <sub>stg</sub>     |                     | -55 to 150         | °C   |

## THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Characteristic Symbol Test Conditions |                                                                    | Value | Unit |

|----------------------------|---------------------------------------|--------------------------------------------------------------------|-------|------|

| Package Thermal Resistance | Ь                                     | LP package, 2-sided PCB with 3.8 in. <sup>2</sup> copper each side | 43    | °C/W |

| rackage mermar Resistance  | $R_{\theta JA}$                       | LP package, 4-layer PCB based on JEDEC standard                    | 34    | °C/W |

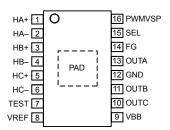

### PINOUT DIAGRAM AND TERMINAL LIST TABLE

**LP Package Pinout**

#### **Terminal List Table**

| Number | Name   | Function               |

|--------|--------|------------------------|

| 1      | HA+    | Input Hall element A   |

| 2      | HA-    | Input Hall element A   |

| 3      | HB+    | Input Hall element B   |

| 4      | HB-    | Input Hall element B   |

| 5      | HC+    | Input Hall element C   |

| 6      | HA-    | Input Hall element C   |

| 7      | TEST   | Connect to VREF        |

| 8      | VREF   | Analog output          |

| 9      | VBB    | Input supply           |

| 10     | OUTC   | Motor terminal phase C |

| 11     | OUTB   | Motor terminal phase B |

| 12     | GND    | Ground                 |

| 13     | OUTA   | Motor terminal phase A |

| 14     | FG     | Speed output           |

| 15     | SEL    | Analog input           |

| 16     | PWMVSP | Logic Input            |

| _      | PAD    | Exposed thermal pad    |

## **RECOMMENDED OPERATING CONDITIONS**

| Characteristic       | Symbol            | Conditions   | Min. | Тур. | Max. | Unit |

|----------------------|-------------------|--------------|------|------|------|------|

| Supply Voltage       | V <sub>BB</sub>   |              | 6    | -    | 17   | V    |

| Output Current       | I <sub>OUT</sub>  |              | _    | _    | 600  | mA   |

| Hall Input Amplitude | V <sub>HALL</sub> | Peak to peak | 50   | _    | _    | mV   |

| PWM Input Frequency  | f <sub>PWM</sub>  |              | 2.5  | _    | 35   | kHz  |

| Hall Bias Current    | I <sub>HALL</sub> |              | _    | _    | 10   | mA   |

## **ELECTRICAL CHARACTERISTICS:** Valid at T<sub>A</sub> = 25°C, V<sub>BB</sub> = 4 to 17 V, unless otherwise specified

| Characteristic              | Symbol              | Test Conditions                                                   | Min.  | Тур. | Max.  | Unit |

|-----------------------------|---------------------|-------------------------------------------------------------------|-------|------|-------|------|

| VBB Supply Current          | I <sub>BB</sub>     | PWMVSP = 50%, I <sub>HALL</sub> = 0 mA                            | _     | 9    | 15    | mA   |

| Output Driver Leakage       | I <sub>LK</sub>     | PWMVSP = 0                                                        | -10   | -    | 10    | μA   |

|                             |                     | Sink + Source; $I_{OUTx}$ = 500 mA, $T_J$ = 25°C, $V_{BB}$ = 12 V | 1     | 1.3  | 1.6   | Ω    |

| Driver On Besistance        |                     | Sink + Source; $I_{OUTx}$ = 500 mA, $T_J$ = 25°C, $V_{BB}$ = 4 V  | _     | 1.6  | _     | Ω    |

| Driver On-Resistance        | R <sub>DS(on)</sub> | Source only; $I_{OUTx}$ = 500 mA, $T_J$ = 25°C, $V_{BB}$ = 12 V   | _     | 0.85 | _     | Ω    |

|                             |                     | Sink only; $I_{OUTx}$ = 500 mA, $T_J$ = 25°C, $V_{BB}$ = 12 V     | -     | 0.45 | _     | Ω    |

| VREF Pin Voltage            | V <sub>REF</sub>    | I <sub>REF</sub> = 0 to 10 mA, V <sub>BB</sub> = 6 V              | 4.75  | 5    | 5.25  | V    |

| VREF Dropout                | V <sub>REFDO</sub>  | I <sub>REF</sub> = 10 mA, V <sub>BB</sub> = 4 V                   | 100   | 400  | 600   | mV   |

| Logic Input Low Level       | V <sub>IL</sub>     | PWMVSP and SEL pins                                               | _     | _    | 0.8   | V    |

| Logic Input High Level      | V <sub>IH</sub>     |                                                                   | 2     | _    | _     | V    |

| Logic Input Hysteresis      | V <sub>HYS</sub>    |                                                                   | 200   | 300  | 600   | mV   |

| Input Current (SEL pin)     | I <sub>SELIN</sub>  | V <sub>SELIN</sub> = 5 V, (50 kΩ pull-down)                       | 50    | 100  | 150   | uA   |

| Input Current (PWMVSP pin)* | I <sub>PWPIN</sub>  | V <sub>PWPIN</sub> = 5V (100 kΩ pull-down)                        | 25    | 50   | 75    | uA   |

| Output Saturation Voltage   | V <sub>SAT</sub>    | I <sub>FG</sub> = 5 mA                                            | _     | _    | 0.3   | V    |

| FG Output Leakage Current   | I <sub>FG</sub>     | V <sub>FG</sub> =18 V                                             | _     | _    | 1     | uA   |

| VSP ADC Input Range         | V <sub>ADC</sub>    | PWMVSP pin, monotonic, V <sub>BB</sub> = 6 V                      | 0     | _    | 4.35  | V    |

| PWM Signal Input Resolution | RES <sub>PWM</sub>  | PWMVSP pin                                                        | _     | _    | 9     | bit  |

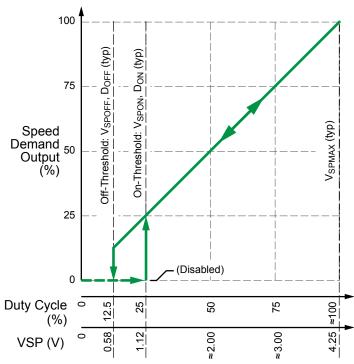

| VSP On-Threshold            | V <sub>SPON</sub>   |                                                                   | 1.02  | 1.12 | 1.22  | V    |

| VSP Off-Threshold           | V <sub>SPOFF</sub>  |                                                                   | 0.48  | 0.58 | 0.68  | V    |

| VSP Maximum Demand          | V <sub>SPMAX</sub>  | V <sub>BB</sub> = 6 V                                             | 4.15  | 4.25 | 4.35  | V    |

| Duty Cycle On-Threshold     | D <sub>ON</sub>     |                                                                   | 23.75 | 25   | 26.25 | %    |

| Duty Cycle Off-Threshold    | D <sub>OFF</sub>    |                                                                   | 11.88 | 12.5 | 13.12 | %    |

Continued on the next page...

# **ELECTRICAL CHARACTERISTICS (continued):** Valid at $T_A = 25$ °C, $V_{BB} = 4$ to 17 V, unless otherwise specified

| Characteristic                  | Symbol              | Test Conditions                                  | Min. [1] | Тур.  | Max. [1]            | Unit |

|---------------------------------|---------------------|--------------------------------------------------|----------|-------|---------------------|------|

| Lock Protection                 | t <sub>OFF</sub>    |                                                  | 7        | 8     | 9                   | S    |

| LOCK Protection                 | t <sub>ON</sub>     |                                                  | 0.9      | 1     | 1.1                 | S    |

| VBB Undervoltage Lockout (UVLO) | V <sub>BBUVLO</sub> | V <sub>BB</sub> rising                           | 3.5      | 3.8   | 3.98                | V    |

| VBB UVLO Hysteresis             | V <sub>BBHYS</sub>  |                                                  | 160      | 300   | 480                 | mV   |

| Dead Time                       | t <sub>DT</sub>     |                                                  | 325      | 400   | 475                 | ns   |

| Motor PWM Frequency             | f <sub>PWM</sub>    |                                                  | 28       | 30    | 32                  | kHz  |

| Pulse Reject Filter             | Tw                  |                                                  | 430      | 600   | 840                 | ns   |

| Overcurrent Threshold           | I <sub>CL</sub>     |                                                  | 0.8      | 1     | 1.2                 | Α    |

| Soft-Start Time                 | t <sub>SS</sub>     | PWM duty ramp 25% to 100% duty cycle             | 0.95     | 1.152 | 1.45                | S    |

| Hall Element Input Range        | V <sub>H</sub>      |                                                  | 0.5      | _     | V <sub>REF</sub> -1 | V    |

| Hall Element Offset             | V <sub>OFF</sub>    |                                                  | -5       | 0     | +5                  | mV   |

| Hysteresis                      | V <sub>HYS</sub>    | Relative to V <sub>OFF</sub>                     | 5        | 13    | 21                  | mV   |

| Hall Element Minimum Amplitude  | V <sub>H</sub>      |                                                  | 50       | _     | -                   | mV   |

| Thermal Shutdown Temperature    | T <sub>JTSD</sub>   | Temperature increasing                           | 150      | 165   | 180                 | °C   |

| Thermal Shutdown Hysteresis     | T <sub>JHYS</sub>   | Recovery = T <sub>JTSD</sub> - T <sub>JHYS</sub> | -        | 20    | _                   | °C   |

<sup>[1]</sup> Specified limits are tested at a single temperature and determined across the operating temperature range by design and characterization.

#### **FUNCTIONAL DESCRIPTION**

**Lock Detect.** A logic circuit monitors the inputs from the Hall position sensors in order to determine if the motor is running as expected. If a fault is detected, the motor drive is disabled for a period of 8 seconds before an auto-restart is attempted. The retry duration is 1 second. Because the on:off ratio is 8:1, neither the IC nor the motor overheat. This cycle continues until the fault condition is removed.

The lock-detect circuit is triggered by any of the following:

- Time between Hall sensor input transitions is less than 52 ms: That value is less than the expected running speed for fan motors (96 rpm for a 4-pole motor, 48 rpm for an 8-pole motor, etc.).

- Invalid Hall conditions: The three inputs from the Hall sensors (HA, HB, and HC) are either all low (000) or all high (111).

- Direction error: The motor is rotating in the wrong direction, which can occur if the Hall sensors are not wired correctly.

**FG.** This open-drain output provides speed data to the system. The system controller can use this data to make adjustments in relation to the speed-demand input, in order to achieve the required speed.

FG changes state in synchronization with the HC+ Hall sensor input, at a rate of one period per electrical rotation of the motor. This open-drain output is rated to 18 V. This allows the pull-up resistor to be connected to VBB.

**Current Limit.** During a locked rotor condition, the current ramps up to the internal current limit. Load current is monitored on the high-side MOSFETs. If the current reaches  $I_{CL}$ , the source driver is turned off for 24  $\mu$ s, to allow the current to decay.

**VREF.** This 5 V reference powers internal logic and analog circuitry. VREF can be used to power the Hall sensor elements with a bias current of up to 10 mA, if required. Stabilize this circuit with a  $0.22~\mu F$  or greater ceramic capacitor.

**TEST.** For factory test use only. Connect this pin to VREF.

**PWMVSP.** This is the speed-demand input pin. To select analog voltage control or PWM duty control, configure the logic state of SEL as follows:

- For PWM mode, tie SEL to VREF.

- For VSP (analog voltage) mode, connect SEL to GND.

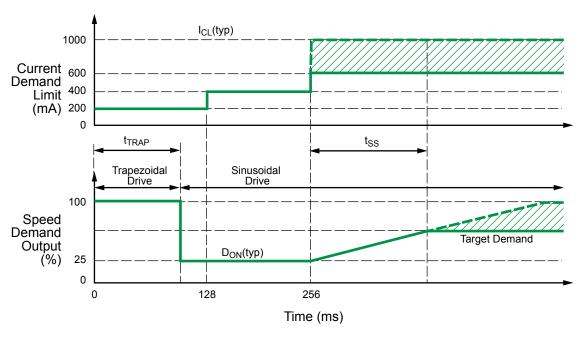

**Speed Demand Control.** The speed-demand transfer function translates the analog or PWM signal on the PWMVSP pin into a percentage of the motor driver output range. The relationship is diagrammed in Figure 1.

When the device is configured for analog control (VSP), an increase in the voltage applied to the PWMVSP pin increases speed demand. This is performed by an internal 9-bit analog-to-digital (A-to-D) converter that translates the input into a speed demand. The resolution of the ADC is 8.4 mV.

The analog configuration also can be used where the system cannot provide a PWM frequency in an appropriate range. An external circuit can be used to translate a PWM-signal duty cycle to an appropriate analog signal. (For more information, see the Application Information section.)

When the device is configured for PWM duty-cycle control, an external PWM signal with a frequency in the range 2.5 to 35 kHz can be used. In this configuration, if the PWMVSP pin becomes open circuit, the motor coasts to a stop.

Figure 1: Duty and Voltage Input versus Speed-Demand Output

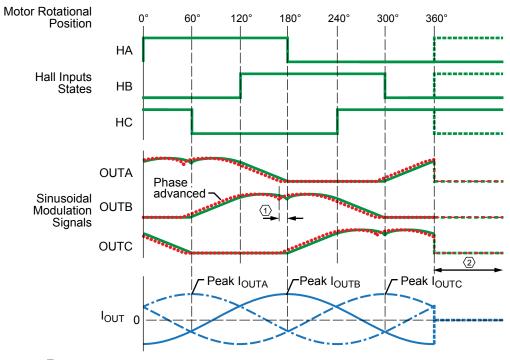

#### **Commutation State Table**

| H  | all Input Sta | te | Mo             | otor Driver Phase State |                |                        |

|----|---------------|----|----------------|-------------------------|----------------|------------------------|

| HA | НВ            | НС | OUTA           | OUTB                    | OUTC           | Operation Mode         |

| Н  | L             | Н  | Sinusoidal PWM | Low                     | Sinusoidal PWM | Typical                |

| Н  | L             | L  | Sinusoidal PWM | Sinusoidal PWM          | Low            | Typical                |

| Н  | Н             | L  | Sinusoidal PWM | Sinusoidal PWM          | Low            | Typical                |

| L  | Н             | L  | Low            | Sinusoidal PWM          | Sinusoidal PWM | Typical                |

| L  | Н             | Н  | Low            | Sinusoidal PWM          | Sinusoidal PWM | Typical                |

| L  | L             | Н  | Sinusoidal PWM | Low                     | Sinusoidal PWM | Typical                |

| Н  | Н             | Н  | Z              | Z                       | Z              | Fault, all MOSFETS off |

| L  | L             | L  | Z              | Z                       | Z              | Fault, all MOSFETS off |

Note: Z indicates high impedance.

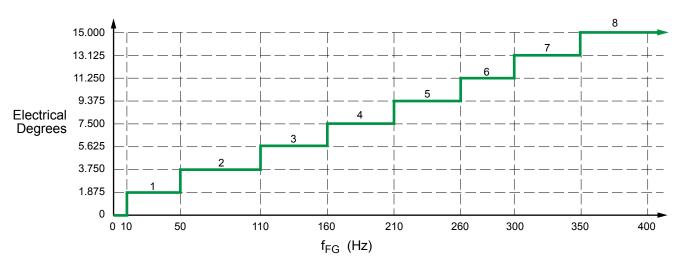

- 1 Amount of phase advance depends on speed, see figure 3

- ② Output State: All gate drivers low

Fault Mode: Hall Inputs = 000 or 111

(Fault mode can also result from TSD or V<sub>BBUVLO</sub>)

## **Three-Phase Fan Driver**

**Soft Start.** The soft-start function is integrated into the IC. Soft start ramps both the speed-demand function (output duty cycle) and the current limit to reduce the load on the power supply and smoothly ramp the motor up to speed, as shown in Figure 2. During this ramping, the current takes several steps, at 200, 400, and 600 mA.

The A4944 starts up in trapezoidal-drive mode and switches to sine-drive mode as soon as the motor moves sufficiently fast

$(t_{TRAP})$ . This typically occurs in less than 128 ms. The actual time depends on the motor, the load, and the supply voltage.

After sinusoidal-drive mode begins, the PWM duty cycle is held at  $D_{ON}$  until approximately 256 ms after startup, then ramps up to the final value, according to:

$t_{SS}$  (ms) = 512 × (Speed Demand (%) – 25%) × 3 (ms)

Figure 2: Effect of Soft-Start Operation on Output Current Limit and Speed-Demand Output

Figure 3: Dynamic Phase Advance

#### **APPLICATION INFORMATION**

#### **Layout Notes**

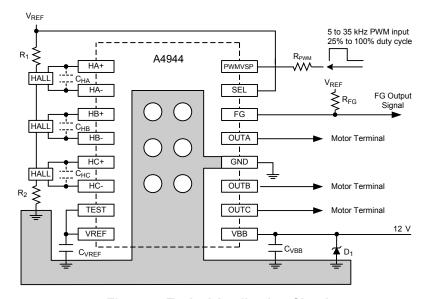

A typical layout is illustrated in Figure 4. The recommended component values for this layout are provided in Table 1.

The following guidelines for printed circuit board (PCB) layout should be observed:

- Add thermal vias to exposed pad area under the LP package.

- Connect ground planes on the top and bottom surfaces of the PCB.

- Place  $C_{VREF}$  and  $C_{VBB}$  as close as practical to the A4944.

- Route the Hall input traces (to HA, HB, and HC) away from the motor output traces (OUTA, OUTB, and OUTC). If possible, use the opposite sides of the PCB. For example, route the Hall input traces on the top layer, and route the output traces on the bottom layer.

- Place  $R_1$  and  $R_2$  near the Hall sensor devices.

**Table 1: Recommended External Components**

| Symbol            | Value                            | Note                                                                                                                                                                                                                                                             |

|-------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $R_1$ and $R_2$   | 330 Ω                            | Hall bias resistors selected to allow input voltages to be in common-mode range of Hall input pins (500 mV to $V_{REF} - 1 \text{ V}$ ). Maximum $V_{REF}$ current = 10 mA. Hall bias must result in the $V_{p-p}$ of the Hall signals being greater than 50 mV. |

| C <sub>VREF</sub> | 0.22 μF/<br>X5R/10 V             | Ceramic capacitor required.                                                                                                                                                                                                                                      |

| C <sub>VBB</sub>  | 10 to<br>47 μF                   | For power-supply stabilization; electrolytic or ceramic capacitor can be used.                                                                                                                                                                                   |

| R <sub>FG</sub>   | 20 kΩ                            | Optional pull-up resistor for speed feedback.                                                                                                                                                                                                                    |

| Сн                | Not<br>Installed                 | Not required for typical applications because the IC has an internal noise filter.                                                                                                                                                                               |

| D <sub>1</sub>    | Not<br>Installed<br>TVS<br>Zener | Optional, to limit maximum V <sub>BB</sub> if the power supply line is subject to transients. It is recommended to clamp below 18 V (for example: Fairchild SMBJ14A).                                                                                            |

| R <sub>PWM</sub>  | 1 kΩ                             | Optional. If PWMVSP is wired to a connector, R <sub>PWM</sub> isolates PWMVSP from noise and from overvoltage transients.                                                                                                                                        |

**Figure 4: Typical Application Circuit**

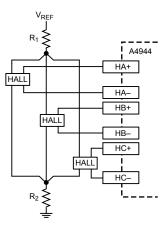

## Hall Biasing

The suggested Hall element bias is a series connection, as shown in Figure 4. It is allowable to connect the bias supply in parallel, as shown in Figure 5. When connecting in parallel, it might be necessary to change the bias resistors (R1 and R2) from the recommended values shown in Table 1, in order to limit the maximum Hall element bias current to less than 10 mA.

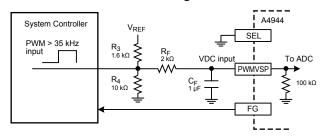

### **Analog Input from System PWM**

For proper operation with an external PWM speed-demand signal, the PWMVSP pin requires a frequency in the range of 5 to 35 kHz. If the system frequency is beyond this range, an external circuit can be used to translate the system PWM signal into an analog voltage that is appropriate for input to the PWMVSP pin. Use of an analog voltage input is selected by connecting the SEL pin to GND.

An example circuit is shown in Figure 6. Note:

- A filter composed of resistor  $R_F$  (2 k $\Omega$ ) and capacitor  $C_F$  (1  $\mu F$ ) smooths the input PWM to the analog voltage used by the ADC

- For low input PWM frequencies, it might be necessary to increase C<sub>F</sub>.

- The resistor divider composed by  $R_3$  (1.6 k $\Omega$ ) and  $R_4$  (10 k $\Omega$ ) scales the input to 100% demand when a 100% PWM duty cycle is applied.

Figure 5: Alternative Parallel Circuit for Hall-Element Biasing

Figure 6: Alternative Circuit for Providing Analog Speed-Demand Input from a High System PWM Signal

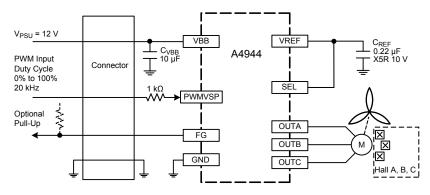

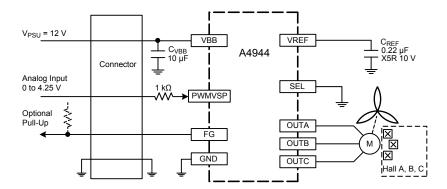

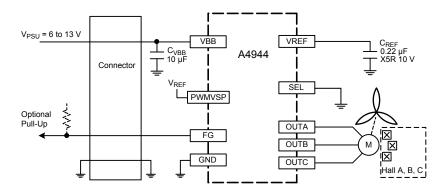

## **Fan System Integration**

Alternative circuits for three methods of integration of the device into typical fan system applications—PWM control input, analog voltage control input, and supply voltage control—are provided in Figure 7.

System PWM Speed Control

System Analog Voltage Speed Control

VBB Voltage Mode Speed Control

Figure 7: Typical Fan System Configuration Using PWM Speed Control

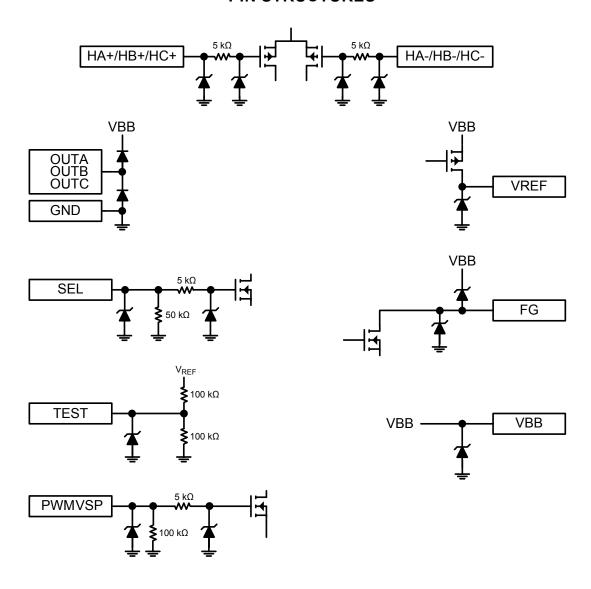

### **PIN STRUCTURES**

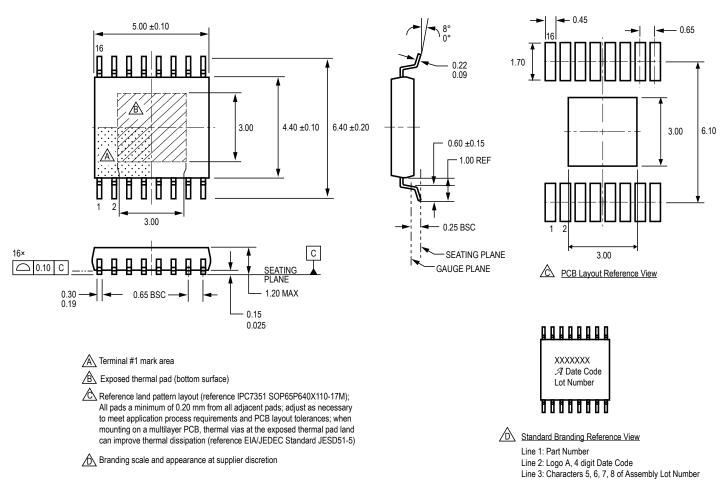

## **PACKAGE OUTLINE DRAWING**

## For Reference Only – Not for Tooling Use

(Reference JEDEC MO-153 ABT; Allegro DWG-0000379, Rev. 3)

Dimensions in millimeters – NOT TO SCALE

Dimensions exclusive of mold flash, gate burrs, and dambar protrusions

Exact case and lead configuration at supplier discretion within limits shown

Figure 8: Package LP, 16-Pin TSSOP with Exposed Thermal Pad

A4944

# **Three-Phase Fan Driver**

#### **Revision History**

| Number | Date           | Description                                                                                                     |

|--------|----------------|-----------------------------------------------------------------------------------------------------------------|

| 2      | April 23, 2018 | Minor editorial updates                                                                                         |

| 3      | July 2, 2019   | Minor editorial updates                                                                                         |

| 4      | July 14, 2022  | Updated LP package drawing (page 13); removed A4944LWTR-T package variant (page 1-3, page 14)                   |

| 5      | March 21, 2025 | Removed limited distribution markings, made minor editorial changes, and updated source file format (all pages) |

Copyright 2025, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website: www.allegromicro.com