## Multi-Topology Synchronous LED Controller with PWM Dimming and High/Low Intensity Modes

### FEATURES AND BENEFITS

- Wide 5 to 37 V input voltage range

□ 40 V absolute maximum for load dump

□ 4.5 V UVLO falling for idle stop

- Wide output voltage, up to 70 V OVP rating

- Single-ended topology controller with internal gate drivers for low-side and high-side external MOSFETs

Topology options including boost and buck-boost

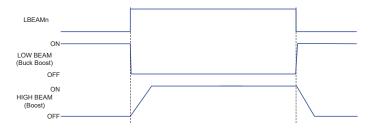

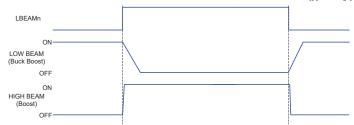

- □ Unique topology changeover option for high/low beam

- Unique slew rate control to minimize current overshoot/undershoot during high/low transition

- Complementary gate drivers for high/low beam applications

- Options for SPI control or programmable EEPROM for design parameters, eliminates need for local microcontroller

- Internal PWM generator and driver to control external dimming MOSFET

- Fixed frequency operation with programmable dithering for EMC mitigation

- Constant current regulation

- Extensive fault detection and reporting through SPI or hardwired fault signals

- Analog dimming options for LED binning, input voltage foldback, and temperature foldback via NTC

- 5 V / 50 mA linear regulator to power external circuitry

- Four programmable current settings to adapt to LED binning

### DESCRIPTION

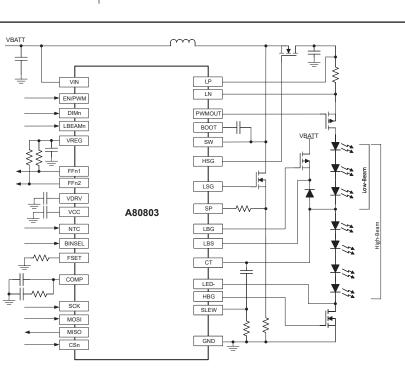

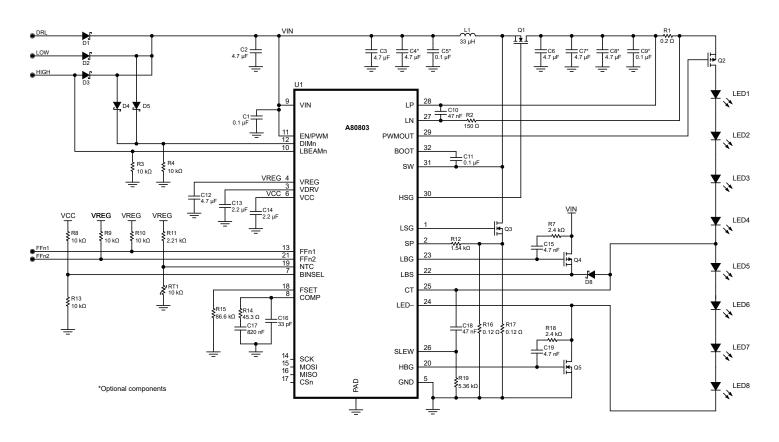

The A80803 is a switch-mode, constant-current DC/DC controller for high-power LED automotive lighting applications. The controller is based on a programmable fixed frequency, peak current mode control architecture and can be configured in multiple different switching topologies to suit different application requirements.

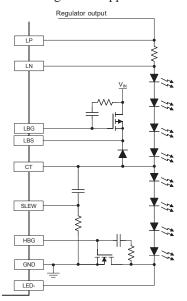

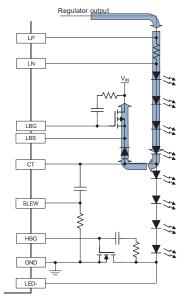

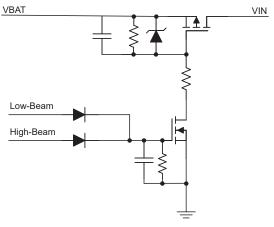

Both a low-side and high-side gate driver are included to control the external power MOSFETs. Two additional gate drivers are integrated to enable/disable part of the LED string to simplify high/low beam applications.

Diagnostics can be reported through SPI or via the two fault pins. The SPI interface can also be used to control many configuration options of the A80803. Alternatively, these options can be factory-programmed and stored in EEPROM to remove the need for a local microcontroller.

LED brightness can be controlled by a PWM signal on the EN/ PWM pin or by an internal PWM signal configured via SPI. An internal driver controls a MOSFET in series with the LED string to optimize dimming. The PWMOUT driver strength is programmable via SPI to optimize LED current during PWM transitions. LED current foldback is provided for low input voltage and thermal events.

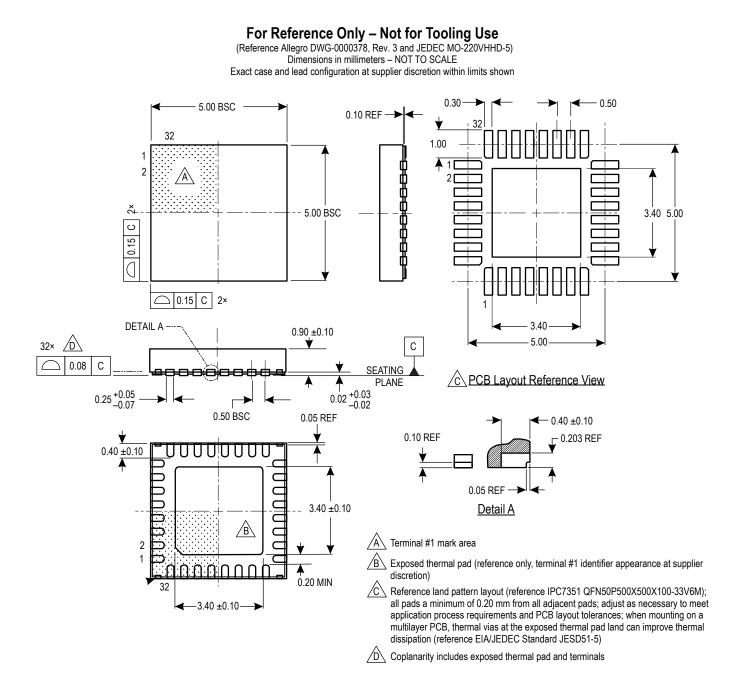

The A80803 is available in a thermally enhanced 32-pin 5 mm  $\times$  5 mm QFN package with wettable flank.

### APPLICATIONS

• Automotive lighting applications

### PACKAGE

32-pin 5 mm × 5 mm QFN with exposed thermal pad and wettable flank (suffix ET)

Not to scale

Figure 1: Simplified Block Diagram

#### **SELECTION GUIDE**

| Part Number  | Package                                                            | Packing <sup>[1]</sup>       |

|--------------|--------------------------------------------------------------------|------------------------------|

| A80803KETASR | 32-pin 5 mm × 5 mm QFN with exposed thermal pad and wettable flank | 6000 pieces per 13-inch reel |

<sup>[1]</sup> Contact Allegro for additional packing options.

#### **ABSOLUTE MAXIMUM RATINGS**<sup>[2]</sup>

| Characteristic                                  | Symbol                 | Notes      | Rating      | Unit |

|-------------------------------------------------|------------------------|------------|-------------|------|

| VIN, EN/PWM, DIMn, LBEAMn                       |                        |            | -0.3 to 40  | V    |

| BOOT, HSG                                       |                        |            | -0.3 to 90  | V    |

|                                                 |                        | t < 250 ns | -2 to 90    | V    |

|                                                 |                        | t < 50 ns  | –6 to 90    | V    |

| Boot with respect to SW                         | V <sub>BOOT-SW</sub>   |            | 6.6         | V    |

| LP, LN, PWMOUT, LED–, SW, LBS,<br>LBG, CT, SLEW |                        |            | -0.3 to 80  | V    |

| LP with respect to LN                           | V <sub>LP-LN</sub>     |            | -0.5 to 0.5 | V    |

| PWMOUT with respect to LP                       | V <sub>PWMOUT-LP</sub> |            | -6.6        | V    |

| LBG with respect to LBS                         | V <sub>LBG-LBS</sub>   |            | -6.6        | V    |

| HSG with respect to SW                          | V <sub>HSG-SW</sub>    |            | -6.6        | V    |

| VCC, BINSEL, COMP, SP                           |                        |            | -0.3 to 3.8 | V    |

| All other pins                                  |                        |            | -0.3 to 6.6 | V    |

| Junction Temperature                            | TJ                     |            | -40 to 150  | °C   |

| Storage Temperature Range                       | T <sub>stg</sub>       |            | -55 to 150  | °C   |

[2] Stresses beyond those listed in this table may cause permanent damage to the device. The absolute maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **THERMAL CHARACTERISTICS**

| Characteristic                         | Symbol                | Test Conditions <sup>[3]</sup>         | Value | Unit |

|----------------------------------------|-----------------------|----------------------------------------|-------|------|

| Junction to Ambient Thermal Resistance | $R_{	extsf{	heta}JA}$ | On 4-layer PCB based on JEDEC standard | 28    | °C/W |

<sup>[3]</sup> Additional thermal information available on the Allegro website.

# Multi-Topology Synchronous LED Controller with PWM Dimming and High/Low Intensity Modes

### **Table of Contents**

| Features and Benefits              | 1  |

|------------------------------------|----|

| Description                        | 1  |

| Applications                       | 1  |

| Package                            | 1  |

| Simplified Block Diagram           | 1  |

| Selection Guide                    | 2  |

| Absolute Maximum Ratings           | 2  |

| Thermal Characteristics            | 2  |

| Terminal Diagram and Terminal List | 4  |

| Functional Block Diagram           | 5  |

| Electrical Characteristics         | 6  |

| Typical Operating Characteristics  | 10 |

| Functional Description             | 12 |

| Power Converter Operation          | 12 |

| Current Sensing                    | 13 |

| LED PWM Dimming                    | 14 |

| LED Analog Dimming                 | 15 |

| Low and High Beam Control          |    |

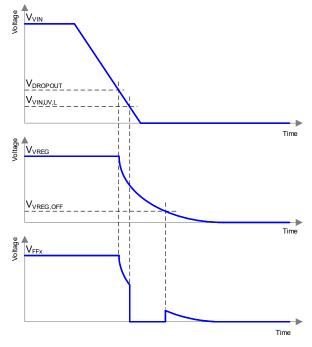

| Input UVLO                                      | 25 |

|-------------------------------------------------|----|

| Linear Regulator                                |    |

| Standby Power                                   |    |

| Fault Handling and Reporting                    |    |

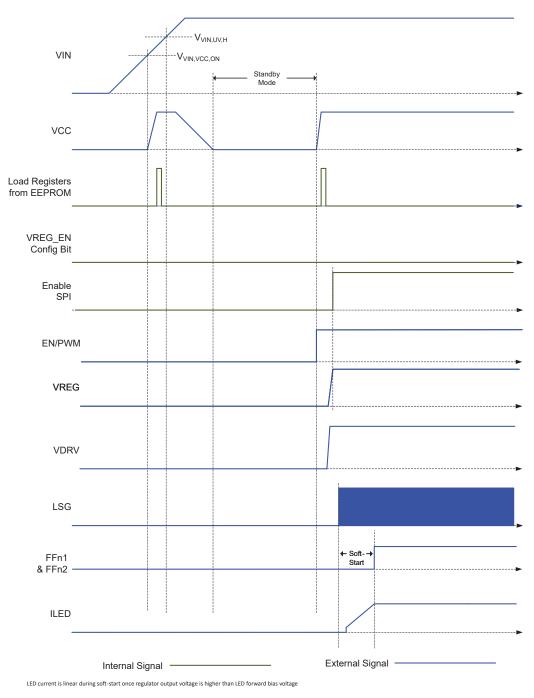

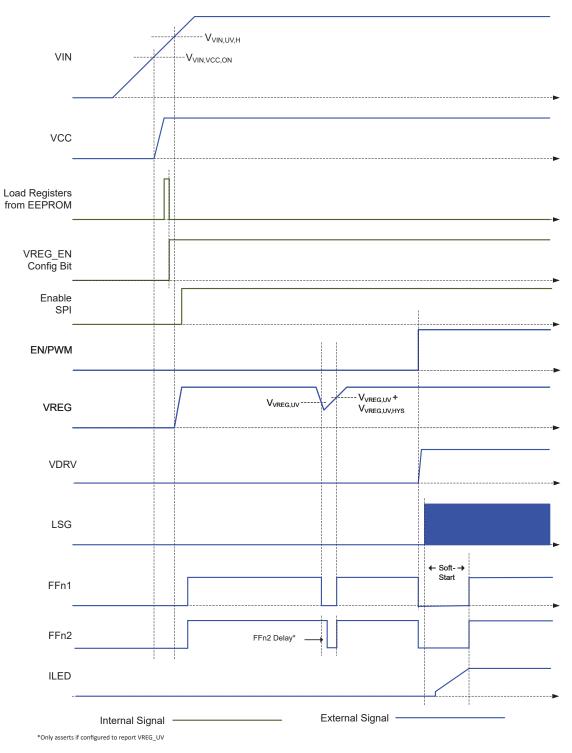

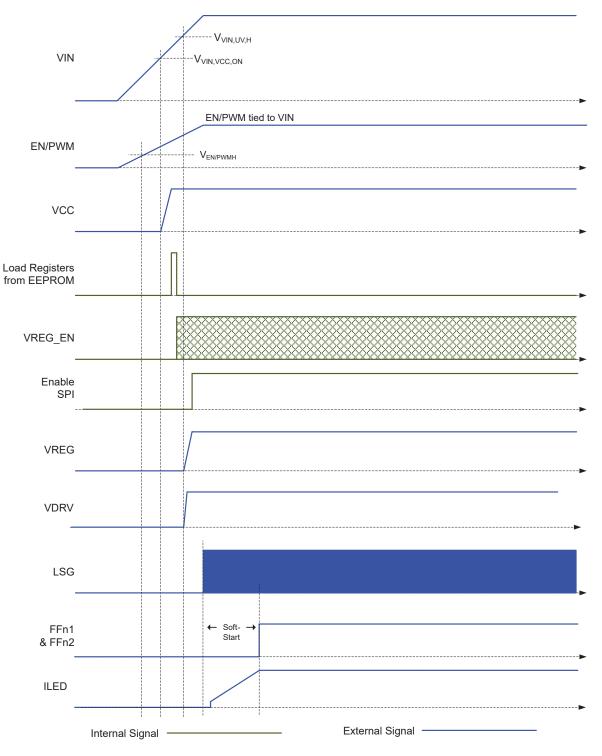

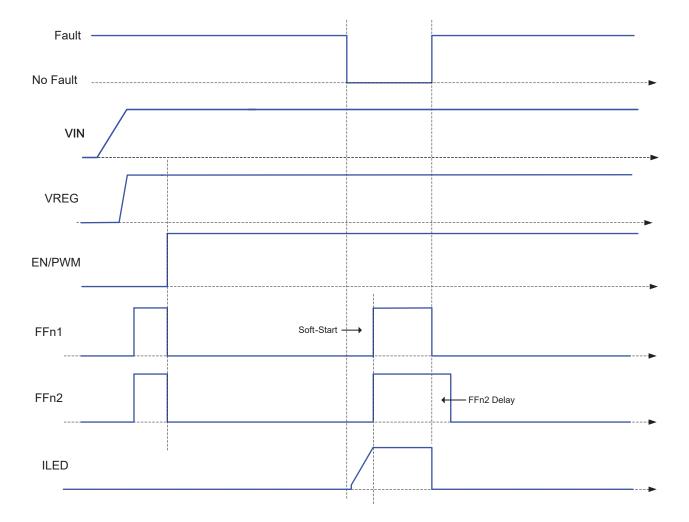

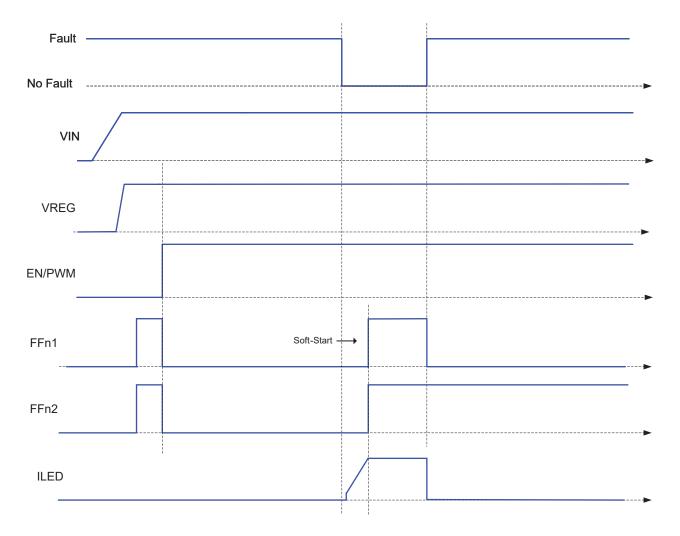

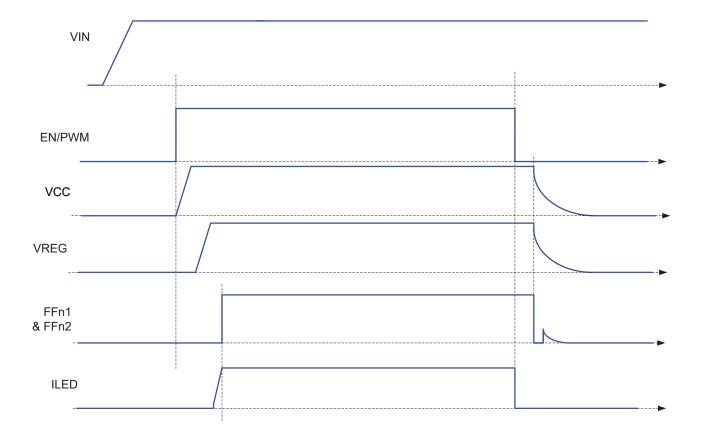

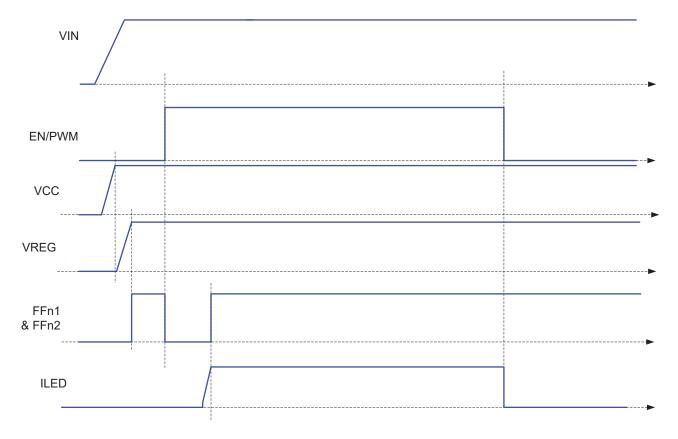

| Startup Timing Diagrams                         |    |

| Serial Communication                            |    |

| Register Map                                    | 40 |

| Applications Information                        | 49 |

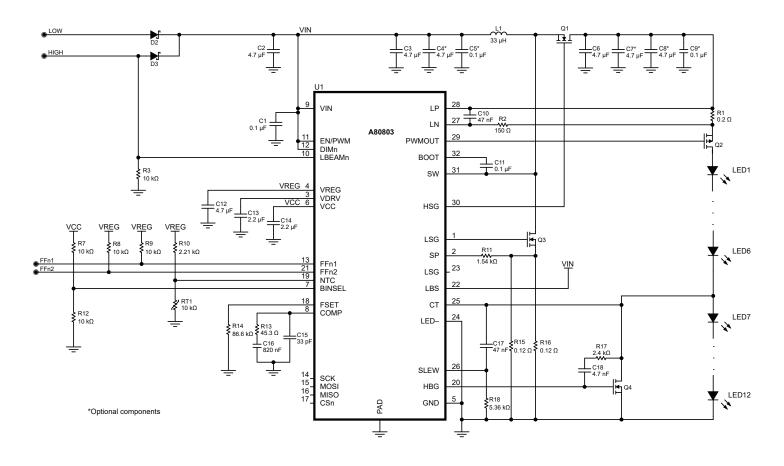

| Three Brightness Level DRL Headlamp Application | 49 |

| Two Brightness Level Lighting Application       |    |

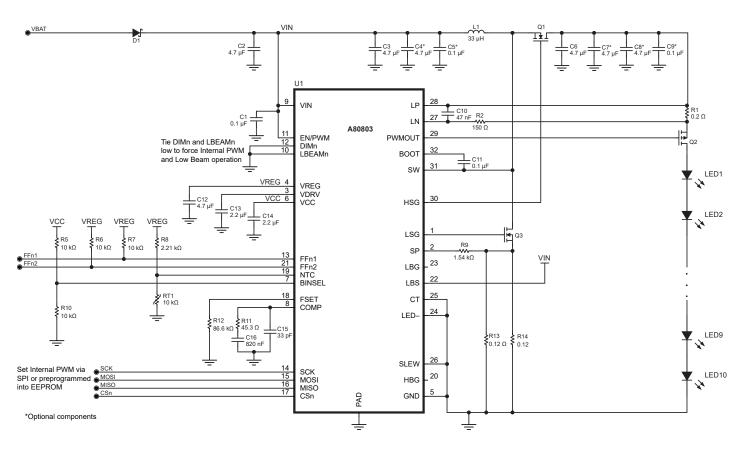

| with Single Low/High-Beam MOSFET                | 51 |

| Single LED String Boost Controller              |    |

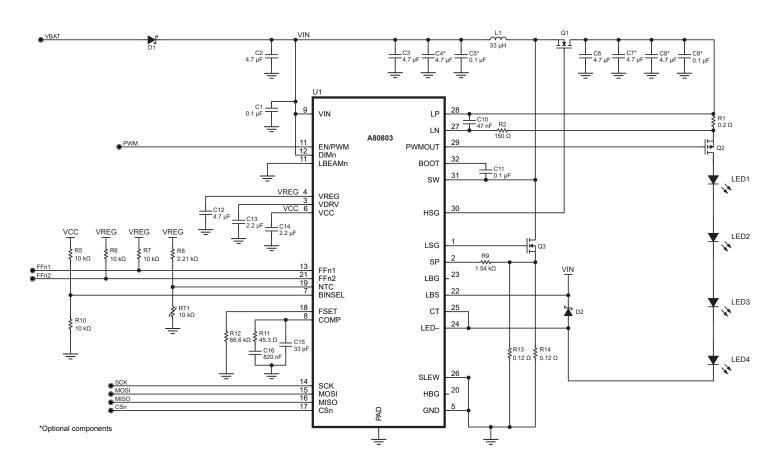

| with Configurable Internal PWM Dimming          | 53 |

| Single LED String Buck-Boost LED Controller     |    |

| with External PWM                               | 55 |

| Package Outline Drawing                         |    |

| Revision History                                | 58 |

# Multi-Topology Synchronous LED Controller with PWM Dimming and High/Low Intensity Modes

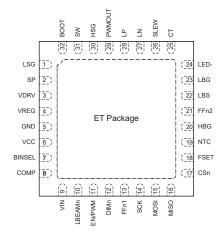

### **TERMINAL DIAGRAM AND TERMINAL LIST**

### **ET-32 Package Terminals**

| Number | Name   | Function                                                                                                                                                                                                               |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | LSG    | Low side gate driver to drive main switching MOSFET in all topologies.                                                                                                                                                 |

| 2      | SP     | Current sense input and slope comp for current mode control of regulator.                                                                                                                                              |

| 3      | VDRV   | Output of internal LDO used as power supply for internal gate drivers. Use a 2.2 $\mu$ F ceramic capacitor from V <sub>DRV</sub> to ground. This pin should not be used to power external circuitry.                   |

| 4      | VREG   | Output of 5 V / 50 mA LDO. Place a 2.2 $\mu F$ capacitor on this pin for stability.                                                                                                                                    |

| 5      | GND    | Ground pin                                                                                                                                                                                                             |

| 6      | VCC    | Voltage rail for internal circuits. Place a 1 µF capacitor here. This pin should only be used for a voltage divider to BINSEL pin and should not drive external circuitry.                                             |

| 7      | BINSEL | Binning pin with four binning levels. Selects reference value for current regulation                                                                                                                                   |

| 8      | COMP   | Compensation pin to stabilize the regulation loop.                                                                                                                                                                     |

| 9      | VIN    | Input voltage pin                                                                                                                                                                                                      |

| 10     | LBEAMn | Low/High beam control.<br>LBEAMn = 0 sets low-beam operation,<br>LBEAMn = 1 sets high-beam operation.                                                                                                                  |

| 11     | EN/PWM | Input for external PWM pulses. PWMOUT can be controlled by this pin in external PWM mode. Pin<br>can also be used as chip enable. A80803 is disabled if this pin is held low for longer than t <sub>DIS,EN/PWM</sub> . |

| 12     | DIMn   | Selects internal or external PWM dimming. External PWM is used when DIMn is high.                                                                                                                                      |

| 13     | FFn1   | Open drain active low signal. Pulls low when any fault is detected.                                                                                                                                                    |

| 14     | SCK    | Serial interface clock signal.                                                                                                                                                                                         |

| 15     | MOSI   | Serial interface input.                                                                                                                                                                                                |

| 16     | MISO   | Serial interface output.                                                                                                                                                                                               |

| 17     | CSn    | Chip Select, active low.                                                                                                                                                                                               |

| 18     | FSET   | Switching frequency programming pin. Connect a resistor form this pin to GND to set the converter switching frequency.                                                                                                 |

| 19     | NTC    | Temperature-controlled analog dimming pin. A voltage on this pin controls the regulated output current.                                                                                                                |

| 20     | HBG    | Gate driver output for high-beam boost topology NFET. Driver is with respect to GND pin.                                                                                                                               |

| 21     | FFn2   | Open drain active low signal. Pulls low when selected faults are detected.                                                                                                                                             |

| 22     | LBS    | Source connection of low-beam buck-boost topology PFET. Tie to VIN if not used.                                                                                                                                        |

| 23     | LBG    | Gate driver output for low-beam buck-boost topology PFET. Driver is with respect to LBS pin.                                                                                                                           |

| 24     | LED-   | Negative end of high-beam LED string (total string).                                                                                                                                                                   |

| 25     | СТ     | Negative end of low-beam LED string, center tap (partial string).                                                                                                                                                      |

| 26     | SLEW   | Filter connection for control of slew rate on topology switch over MOSFETs, LBG, and HBG.                                                                                                                              |

| 27     | LN     | LED current negative sense voltage. A resistor placed between LP and LN sets the current in the LED string.                                                                                                            |

| 28     | LP     | LED current positive sense voltage. A resistor placed between LP and LN sets the current in the LE string.                                                                                                             |

| 29     | PWMOUT | PWM output to drive high side PFET for PWM dimming of LED string.                                                                                                                                                      |

| 30     | HSG    | High side gate driver to drive synchronous MOSFET.                                                                                                                                                                     |

| 31     | SW     | Regulator switch node connect to node.                                                                                                                                                                                 |

| 32     | BOOT   | BOOT voltage for high side gate driver. Place a 0.1 $\mu\text{F}$ capacitor between BOOT and SW for gate drive current.                                                                                                |

| _      | PAD    | Tie to GND plane for optimal thermal performance.                                                                                                                                                                      |

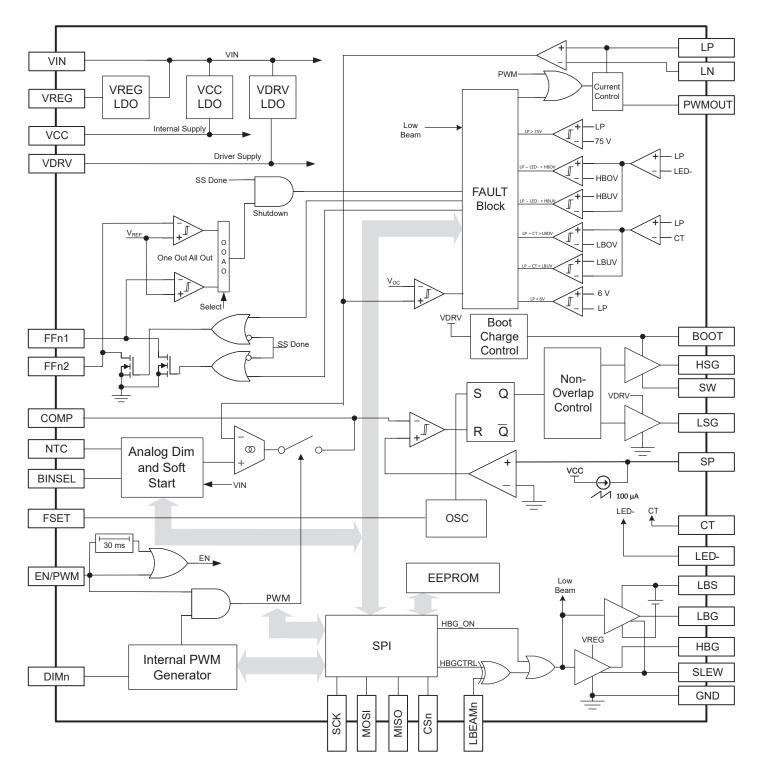

FUNCTIONAL BLOCK DIAGRAM

Allegro MicroSystems 955 Perimeter Road Manchester, NH 03103-3353 U.S.A. www.allegromicro.com

### **ELECTRICAL CHARACTERISTICS** <sup>[1]</sup>: Valid at 5 V ≤ V<sub>IN</sub> ≤ 37 V, $-40^{\circ}C \le T_J \le 150^{\circ}C$ , unless otherwise specified.

| Characteristics                           | Symbol                   | Test Conditions                                             | 6                     | Min.  | Тур. | Max.  | Unit |

|-------------------------------------------|--------------------------|-------------------------------------------------------------|-----------------------|-------|------|-------|------|

| GENERAL INPUTS                            |                          |                                                             |                       |       |      | ,     |      |

| Operating Input Voltage Range             | V <sub>VIN</sub>         |                                                             |                       | 5     | _    | 37    | V    |

|                                           | V <sub>VIN,UV,H</sub>    | V <sub>VIN</sub> rising, V <sub>INUV</sub> = Code 0         |                       | 5.40  | 5.65 | 5.90  | V    |

| Programmable Input Switching<br>Threshold | V <sub>VIN,UV,TOL</sub>  | V <sub>INUV</sub> = Code 0                                  |                       | -0.25 | _    | +0.25 | V    |

| meshol                                    | V <sub>VIN,UV,L</sub>    | V <sub>VIN</sub> falling, V <sub>INUV</sub> = Code 0        |                       | 4.50  | 4.75 | 5.00  | V    |

|                                           | V <sub>VIN,VCC,ON</sub>  | V <sub>VIN</sub> rising, VCC and VREG start                 | up                    | 4.2   | 4.5  | 4.8   | V    |

| Input VCC and VREG Undervoltage           | V <sub>VIN,VCC,OFF</sub> | V <sub>VIN</sub> falling, VCC and VREG start                | up                    | 3.9   | 4.2  | 4.5   | V    |

|                                           | V <sub>VIN,VCC,HYS</sub> | V <sub>VIN</sub> hysteresis when VCC and VI                 | REG shutdown          | -     | 0.3  | _     | V    |

| Input Overvoltage                         | V <sub>VIN,OV,H</sub>    | V <sub>INOV</sub> = Code 7 (35 V is selected)               |                       | -     | 35   | _     | V    |

| Input Overvoltage Tolerance               | V <sub>VIN,OV,TOL</sub>  | V <sub>INOV</sub> = x (all possible voltages)               |                       | -1.3  | _    | +1.3  | V    |

| Input Overvoltage Hysteresis              | V <sub>VIN,OV,HYS</sub>  | V <sub>INOV</sub> = x (all possible voltages)               |                       | -     | 1    | _     | V    |

| Operating Input Current                   | I <sub>VIN,OP</sub>      | Operating, no switching, EN/PWM                             | 1 = 1                 | -     | 8    | _     | mA   |

| Oten albus langust Course at [3]          |                          | Standby mode, EN/PWM = 0,                                   |                       | -     | _    | 160   | μA   |

| Standby Input Current <sup>[3]</sup>      | I <sub>VIN,STANDBY</sub> | VREG_EN = 0, V <sub>VIN</sub> = 14 V                        | T <sub>J</sub> = 25°C | -     | 90   | 120   | μA   |

| Input Switching UV Deglitch Timer         | t <sub>UV,FLT</sub>      |                                                             |                       | 9     | 10   | 11    | ms   |

| Startup Fault Blank Time                  | t <sub>FB</sub>          | SFST = Code 3                                               |                       | -     | 21.5 | _     | ms   |

| LINEAR REGULATOR (VREG)                   |                          |                                                             |                       |       |      |       |      |

| VREG Output Voltage                       | V <sub>VREG</sub>        | $I_{VREG}$ = 0 to 50 mA, 6 V ≤ $V_{VIN}$ ≤ $T_{VREG}$       | 18 V                  | 4.9   | _    | 5.1   | V    |

| VREG Dropout                              | V <sub>VREG,DROP</sub>   | I <sub>VREG</sub> = 50 mA, V <sub>VIN</sub> = 5 V           |                       | -     | _    | 0.3   | V    |

| VREG Overcurrent Limit                    | I <sub>VREG,OC</sub>     | $V_{VREG}$ = 4.85 V, 7 V ≤ $V_{VIN}$ ≤ 18 V                 | ,                     | 55    | -    | 80    | mA   |

| VREG Foldback Current                     | I <sub>VREG,FB</sub>     | $V_{VREG}$ = 0 V, 5 V ≤ $V_{VIN}$ ≤ 18 V                    |                       | -     | 16   | -     | mA   |

| VREG Undervoltage                         | V <sub>VREG,UV</sub>     |                                                             |                       | -     | 4.5  | _     | V    |

| VREG Undervoltage Hysteresis              | V <sub>VREG,UV,HYS</sub> |                                                             |                       | -     | 240  | _     | mV   |

| DRIVER POWER SUPPLY (VDRV)                |                          |                                                             |                       |       |      |       |      |

| VDRV Output Voltage                       | V <sub>VDRV</sub>        | $I_{VDRV}$ = 20 mA, 6.5 V $\leq$ V <sub>VIN</sub> $\leq$ 18 | V                     | 5.8   | _    | 6.2   | V    |

| VDRV Dropout                              | V <sub>VDRV,DROP</sub>   | I <sub>VDRV</sub> = 20 mA, V <sub>VIN</sub> = 6 V           |                       | -     | -    | 0.6   | V    |

| INTERNAL REGULATOR (VCC)                  |                          |                                                             |                       |       |      |       |      |

| VCC Output Voltage                        | V <sub>VCC</sub>         | $I_{VCC}$ = 0 to 5 mA, 6 V ≤ V <sub>VIN</sub> ≤ 18          | V                     | 3.2   | _    | 3.4   | V    |

| OSCILLATOR                                |                          |                                                             |                       |       |      |       |      |

| Oscillator Frequency                      | f <sub>OSC</sub>         | R <sub>FSET</sub> = 100 kΩ                                  |                       | 315   | 350  | 385   | kHz  |

| MAIN REGULATOR (LSG, HSG, BO              | DOT, SW)                 |                                                             |                       |       |      |       |      |

| Gate Driver Turn On Time [3]              | t <sub>r</sub>           | C <sub>LOAD</sub> = 1 nF, 20% to 80%                        |                       | -     | 7.5  | _     | ns   |

| Gate Driver Turn Off Time [3]             | t <sub>f</sub>           | C <sub>LOAD</sub> = 1 nF, 80% to 20%                        |                       | -     | 5    | _     | ns   |

| LSG Minimum Off Time                      | t <sub>off,MIN</sub>     |                                                             |                       | _     | _    | 135   | ns   |

| LSG Minimum On Time                       | t <sub>on,MIN</sub>      |                                                             |                       | -     | _    | 135   | ns   |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Thermally limited depending on input voltage, output voltage, duty cycle, regulator load currents, PCB layout, and airflow.

<sup>[3]</sup> Ensured by design and characterization, not production tested.

# Multi-Topology Synchronous LED Controller with PWM Dimming and High/Low Intensity Modes

### **ELECTRICAL CHARACTERISTICS** <sup>[1]</sup> (continued): Valid at $5 V \le V_{IN} \le 37 V$ , $-40^{\circ}C \le T_{J} \le 150^{\circ}C$ , unless otherwise specified.

| Characteristics                                         | Symbol                   | Test Conditions                                                                                                                                                            | Min. | Тур. | Max. | Unit            |

|---------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-----------------|

| MAIN REGULATOR (LSG, HSG, BC                            | OT, SW) (cont            | tinued)                                                                                                                                                                    |      | •    |      |                 |

| LSG to GND High Voltage                                 | V <sub>LSG</sub>         | $6 \text{ V} \le \text{V}_{\text{VIN}} \le 18 \text{ V}$                                                                                                                   | 5.7  | _    | 6.2  | V               |

| Low Side Gate Driver Source Current                     | I <sub>LSG,H</sub>       | V <sub>VDRV</sub> = 6 V, V <sub>LSG</sub> = 1.5 V                                                                                                                          | _    | 1.4  | _    | A               |

| Low Side Gate Driver Sink Current                       | I <sub>LSG,L</sub>       | V <sub>VDRV</sub> = 6 V, V <sub>LSG</sub> = 2.0 V                                                                                                                          | _    | 1.6  | _    | A               |

| HSG to SW High Voltage                                  | V <sub>HSG,SW</sub>      | $V_{BOOT} - V_{SW} = 5.3 V$                                                                                                                                                | _    | 5.3  | _    | V               |

| High-Side Gate Driver Source Current                    | I <sub>HSG,H</sub>       | V <sub>VDRV</sub> = 6 V, V <sub>BOOT</sub> – V <sub>SW</sub> = 5.3 V, V <sub>HSG,SW</sub> = 1.5 V                                                                          | _    | 1.3  | _    | A               |

| High Side Gate Driver Sink Current                      | I <sub>HSG,L</sub>       | V <sub>VDRV</sub> = 6 V, V <sub>BOOT</sub> – V <sub>SW</sub> = 5.3 V, V <sub>HSG</sub> = 2.0 V                                                                             | _    | 1.5  | _    | A               |

| INNER CURRENT LOOP CONTROI                              |                          |                                                                                                                                                                            |      |      |      |                 |

| Current Sense Input (SP) Bias Current                   | I <sub>BIAS</sub>        | V <sub>SP</sub> = 300 mV                                                                                                                                                   | _    | -20  | _    | μA              |

| Current Sense (SP) Overload Switch<br>Threshold Voltage | V <sub>SP,OL</sub>       |                                                                                                                                                                            | 370  | 400  | 440  | mV              |

| Switch Current Overload Filter Time                     | t <sub>SC,OL</sub>       |                                                                                                                                                                            | _    | 64   | _    | Clock<br>cycles |

| Switch Current Sense Amplifier<br>Voltage Gain          | A <sub>CS</sub>          |                                                                                                                                                                            | _    | 2.25 | _    | V/V             |

| Slope Compensation Peak Current                         | I <sub>SLOPE</sub>       |                                                                                                                                                                            | -116 | -    | -93  | μA              |

| OUTER CURRENT LOOP CONTRO                               | L (LP, LN)               |                                                                                                                                                                            |      |      |      |                 |

| Input Bias Current LN                                   | I <sub>LN</sub>          | $V_{LP} = V_{LN} = 14 V$                                                                                                                                                   | _    | 500  | -    | nA              |

| Input Bias Current LP                                   | I <sub>LP</sub>          | $V_{LP} = V_{LN} = 14 V$                                                                                                                                                   | _    | 1    | _    | mA              |

|                                                         |                          | $EN/PWM = 1, V_{IDL} = V_{LP} - V_{LN}, k_{BINx} = k_{VIN} = k_{NTC} = 1$                                                                                                  | 196  | 200  | 204  | mV              |

| Differential Sense Voltage                              | $K_{BIN}V_{IDL}$         | $ \begin{array}{l} EN/PWM = 1,  V_{\mathsf{IDL}} = V_{\mathsf{LP}} - V_{\mathsf{LN}},  k_{\mathsf{BINx}} = 0.625, \\ k_{\mathsf{VIN}} = k_{\mathsf{NTC}} = 1 \end{array} $ | 119  | 125  | 131  | mV              |

|                                                         |                          | $k_{BINx} = k_{NTC} = 1, k_{VIN} = 0.2$                                                                                                                                    | _    | 40   | _    | mV              |

| Input Common Mode Range                                 | V <sub>LP,CM</sub>       |                                                                                                                                                                            | 6    | -    | 70   | V               |

| Error Amplifier Open Loop DC Gain <sup>[3]</sup>        | A <sub>VEA</sub>         |                                                                                                                                                                            | _    | 62   | _    | dB              |

| Transconductance                                        | g <sub>mCOMP</sub>       |                                                                                                                                                                            | 1100 | 1500 | 1900 | μA/V            |

| COMP Sink Current                                       | I <sub>COMP,sink</sub>   | $V_{COMP}$ = 0.8 V, $V_{LP} - V_{LN}$ = 250 mV                                                                                                                             | _    | 1    | -    | mA              |

| COMP Source Current                                     | I <sub>COMP,source</sub> | $V_{COMP}$ = 0.8 V, $V_{LP} - V_{LN}$ = 150 mV                                                                                                                             | _    | -105 | -    | μA              |

| COMP Leakage Current                                    | I <sub>LCOMP,LKG</sub>   | V <sub>COMP</sub> = 1 V, No switching                                                                                                                                      | _    | ±200 | -    | nA              |

| Overcurrent Threshold                                   | V <sub>IDL,OC</sub>      | LP wrt LN                                                                                                                                                                  | 260  | 320  | 380  | mV              |

| Overcurrent Hysteresis                                  | V <sub>IDL,OC,HYS</sub>  |                                                                                                                                                                            | _    | 30   | _    | mV              |

| LED Output Overcurrent Filter Time                      | t <sub>OPI</sub>         | OCFILT = Code 0                                                                                                                                                            | _    | 2    | -    | clock<br>cycles |

| LED Output Undervoltage Filter Time                     | t <sub>OPV</sub>         |                                                                                                                                                                            | _    | 30   | -    | clock<br>cycles |

| Hiccup Shutdown Period                                  | t <sub>HIC</sub>         | LED overcurrent or output undervoltage or<br>overvoltage or switch overload                                                                                                | 9    | 10   | 11   | ms              |

| THERMAL PROTECTION                                      |                          |                                                                                                                                                                            |      |      |      |                 |

| Overtemperature Shutdown Threshold                      | T <sub>JF</sub>          | Temperature increasing                                                                                                                                                     | 155  | 170  | _    | °C              |

| Overtemperature Hysteresis                              | ΔTJ                      | Recovery = $T_{JF} - \Delta T_J$                                                                                                                                           | _    | 20   | _    | °C              |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Thermally limited depending on input voltage, output voltage, duty cycle, regulator load currents, PCB layout, and airflow.

<sup>[3]</sup> Ensured by design and characterization, not production tested.

### Multi-Topology Synchronous LED Controller with PWM Dimming and High/Low Intensity Modes

### **ELECTRICAL CHARACTERISTICS** <sup>[1]</sup> (continued): Valid at $5 \vee \leq V_{IN} \leq 37 \vee, -40^{\circ}C \leq T_{J} \leq 150^{\circ}C$ , unless otherwise specified.

| Characteristics                           | Symbol                       | Test Conditions                                          | Min.                    | Тур.  | Max.              | Unit |

|-------------------------------------------|------------------------------|----------------------------------------------------------|-------------------------|-------|-------------------|------|

| PWM DIMMING AND ENABLE (EN                | PWM, PWMOL                   | JT, DIMN)                                                |                         |       |                   |      |

| Disable Time                              | t <sub>DISEPWM</sub>         | EN/PWM = 0                                               | 24.8                    | 30    | 35                | ms   |

| EN/PWM Low Voltage                        | V <sub>EN/PWML</sub>         |                                                          | -                       | _     | 0.3               | V    |

| EN/PWM High Voltage                       | V <sub>EN/PWMH</sub>         |                                                          | 2                       | _     | _                 | V    |

| EN/PWM to PWMOUT Propagation<br>Delay     | t <sub>prop,DLY</sub>        | V <sub>LP</sub> = 10 V                                   | -                       | 2.6   | -                 | μs   |

| PWMOUT Low Voltage                        | V <sub>PWMLO</sub>           | PFET on, PWMOUT wrt LP, VLP = 10V                        | -6.6                    | -5.5  | -4.5              | V    |

| Peak Pull-Up Current                      | I <sub>PULLUP</sub>          | EN/PWM = 0, PWMOUT wrt LP = 0 V, PWM_DRV = Code 0        | -                       | -25   | -                 | mA   |

| Peak Pull-Down Current                    | I <sub>PULLDOWN</sub>        | EN/PWM = 1, PWMOUT wrt LP = -5.5 V, PWM_<br>DRV = Code 0 | _                       | 25    | -                 | mA   |

| Internal PWM Clock Frequency<br>Tolerance | f <sub>PWM,int</sub>         |                                                          | -10                     | _     | +10               | %    |

| External PWM Frequency                    | f <sub>PWM,ext</sub>         |                                                          | 100                     | _     | 1000              | Hz   |

| External PWM Duty Cycle                   | D <sub>PWM,ext</sub>         | f <sub>PWM,ext</sub> = 500 Hz                            | 5                       | _     | 95                | %    |

| LP Undervoltage PWMOUT Turn-On            | V <sub>PWMUVON</sub>         | Measured at LP wrt GND                                   | _                       | _     | 6.3               | V    |

| LP Undervoltage PWMOUT Turn-Off           | V <sub>PWMUVOFF</sub>        | Measured at LP wrt GND                                   | 5.5                     | _     | _                 | V    |

| DIMn Low Voltage                          | V <sub>DIMnL</sub>           |                                                          | -                       | _     | 0.3               | V    |

| DIMn High Voltage                         | V <sub>DIMnH</sub>           |                                                          | 2                       | _     | _                 | V    |

| DIMn Deglitch Time                        | t <sub>deglitch,DIMn</sub>   |                                                          | 90                      | 100   | 110               | μs   |

| LOW/HIGH BEAM (LBEAMN, LBG,               |                              |                                                          |                         |       |                   |      |

| LBEAMn Low Voltage                        | V <sub>LBEAMnLO</sub>        |                                                          | _                       | _     | 0.3               | V    |

| LBEAMn High Voltage                       | V <sub>LBEAMnHi</sub>        |                                                          | 2                       | _     | _                 | V    |

| LBEAMn Deglitch Time                      | t <sub>deglitch,LBEAMn</sub> |                                                          | 90                      | 100   | 110               | μs   |

| LBG to LBS Low Voltage                    | V <sub>LBG,LO</sub>          | LBEAMn = 0, LBG wrt LBS, V <sub>LBS</sub> = 10 V         | -6.5                    | -5.5  | -4.5              | V    |

| LBG Peak Pull-Up Current                  | I <sub>LBG,PULLUP</sub>      | LBEAMn = 1, LBG wrt LBS = 0 V, V <sub>LBS</sub> = 10 V   | -                       | -0.24 | _                 | mA   |

| LBG Peak Pull-Down Current                | I <sub>LBG,PULLDOWN</sub>    | LBEAMn = 0, LBG wrt LBS = –5 V, V <sub>LBS</sub> = 10 V  | _                       | 0.24  | _                 | mA   |

| HBG to GND High Voltage                   | V <sub>HBG,LO</sub>          | LBEAMn = 1, HBG wrt GND, V <sub>VIN</sub> = 10 V         | V <sub>VREG</sub> - 0.1 | _     | V <sub>VREG</sub> | V    |

| HBG Peak Pull-Up Current                  | I <sub>HBG,PULLUP</sub>      | LBEAMn = 1, HBG wrt GND = 0 V                            | -                       | -0.24 | _                 | mA   |

| HBG Peak Pull-Down Current                | I <sub>HBG,PULLDOWN</sub>    | LBEAMn = 0, HBG wrt GND = V <sub>VREG</sub>              | _                       | 0.24  | _                 | mA   |

| PROTECTION FEATURES                       |                              |                                                          |                         |       |                   |      |

| Output Over/Undervoltage Tolerance        | V <sub>OV/UVTOL</sub>        |                                                          | -1 V - 1%<br>OV/UV      | _     | 1 V + 1%<br>OV/UV | V    |

| Output Overvoltage Hysteresis             | V <sub>OVHYS</sub>           |                                                          | _                       | 0.5   | _                 | V    |

| Fixed Overvoltage Protection              | V <sub>OV,FIXED</sub>        | Measured between LP and GND when rising                  | 72                      | 75    | 78                | V    |

| Fixed Overvoltage Hysteresis              | V <sub>OV,HYS</sub>          | Measured between LP and GND when falling                 | -                       | 1     | _                 | V    |

| Strong Short Protection                   | V <sub>STG,SHT</sub>         | Measure between LP and GND                               | _                       | 1     | _                 | V    |

| CT Undervoltage Protection                | V <sub>CT,UV</sub>           | Measured between CT and GND when falling                 | _                       | 2     | _                 | V    |

| CT Undervoltage Hysteresis                | V <sub>CT,UV,HYS</sub>       | Measured between CT and GND when rising                  | _                       | 0.4   | _                 | V    |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking). <sup>[2]</sup> Thermally limited depending on input voltage, output voltage, duty cycle, regulator load currents, PCB layout, and airflow.

<sup>[3]</sup> Ensured by design and characterization, not production tested.

### Multi-Topology Synchronous LED Controller with PWM Dimming and High/Low Intensity Modes

### **ELECTRICAL CHARACTERISTICS** <sup>[1]</sup> (continued): Valid at $5 \vee \leq V_{IN} \leq 37 \vee$ , $-40^{\circ}C \leq T_{J} \leq 150^{\circ}C$ , unless otherwise specified.

| Characteristics                                          | Symbol              | Test Conditions                                   | Min. | Тур.                                  | Max. | Unit |  |

|----------------------------------------------------------|---------------------|---------------------------------------------------|------|---------------------------------------|------|------|--|

| FAULT REPORTING (FFN1, FFN2)                             |                     |                                                   |      |                                       |      |      |  |

| FFnx Output (Open Drain)                                 | V <sub>FFn,OL</sub> | I <sub>OL</sub> = 1 mA, Fault asserted            | _    | -                                     | 0.4  | V    |  |

| FFnx Output Leakage Current                              | I <sub>FFn,OH</sub> | V <sub>FFnx</sub> = 5.5 V, fault not asserted     | -1   | -                                     | 1    | μA   |  |

| SERIAL COMMUNICATION (MOSI,                              | MISO, SCK, C        | S)                                                | ~    | · · · · · · · · · · · · · · · · · · · |      |      |  |

| Input Low Voltage                                        | V <sub>IL</sub>     |                                                   | _    | -                                     | 0.8  | V    |  |

| Input Low Voltage                                        | V <sub>IH</sub>     | All logic inputs                                  | 2.0  | -                                     | -    | V    |  |

| Input Hysteresis                                         | V <sub>lhys</sub>   | All logic inputs                                  | 250  | 550                                   | _    | mV   |  |

| Input Pull-Down MOSI, SCK                                | R <sub>PDS</sub>    | 0 < V <sub>IN</sub> < 5 V                         | _    | 50                                    | _    | kΩ   |  |

| Input Pull-Up Current to VCC                             | I <sub>PU</sub>     | SS                                                | _    | 100                                   | _    | μA   |  |

| Output Low Voltage                                       | V <sub>OL</sub>     | I <sub>OL</sub> = 1 mA <sup>[1]</sup>             | _    | 0.2                                   | 0.4  | V    |  |

| Output Low Voltage                                       | V <sub>OH</sub>     | $I_{OL} = -1 \text{ mA}^{[1]}$                    | 2.4  | V <sub>VCC</sub> - 0.2                | -    | V    |  |

| Output Leakage <sup>[1]</sup>                            | I <sub>OH</sub>     | 0 V < V <sub>SDO</sub> < 5.5 V, <del>SS</del> = 1 | -1   | -                                     | 1    | μA   |  |

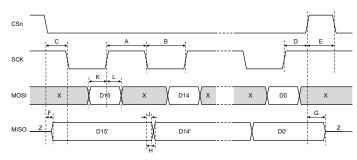

| Clock High Time [3]                                      | t <sub>scкн</sub>   | A in Figure 2                                     | 50   | -                                     | -    | ns   |  |

| Clock Low Time <sup>[3]</sup>                            | t <sub>SCKL</sub>   | B in Figure 2                                     | 50   | -                                     | -    | ns   |  |

| Strobe Lead Time [3]                                     | t <sub>STLD</sub>   | C in Figure 2                                     | 30   | -                                     | -    | ns   |  |

| Strobe Lag Time <sup>[3]</sup>                           | t <sub>STLG</sub>   | D in Figure 2                                     | 30   | -                                     | -    | ns   |  |

| Strobe High Time [3]                                     | t <sub>STRH</sub>   | E in Figure 2                                     | 300  | -                                     | _    | ns   |  |

| Data Out Enable Time <sup>[3]</sup>                      | t <sub>SDOE</sub>   | F in Figure 2                                     | _    | -                                     | 40   | ns   |  |

| Data Out Disable Time [3]                                | t <sub>SDOD</sub>   | G in Figure 2                                     | -    | -                                     | 30   | ns   |  |

| Data Out Valid Time From Clock<br>Falling <sup>[3]</sup> | t <sub>SDOV</sub>   | H in Figure 2                                     | _    | -                                     | 40   | ns   |  |

| Data Out Hold Time From Clock<br>Falling <sup>[3]</sup>  | t <sub>SDOH</sub>   | J in Figure 2                                     | 5    | -                                     | _    | ns   |  |

| Data In Set-Up Time To Clock Rising [3]                  | t <sub>SDIS</sub>   | K in Figure 2                                     | 15   | -                                     | _    | ns   |  |

| Data In Hold Time From Clock Rising [3]                  | t <sub>SDIH</sub>   | L in Figure 2                                     | 10   | _                                     | _    | ns   |  |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

[3] Thermally limited depending on input voltage, output voltage, duty cycle, regulator load currents, PCB layout, and airflow.

[3] Ensured by design and characterization, not production tested.

Figure 2: Serial Interface Timing Diagram

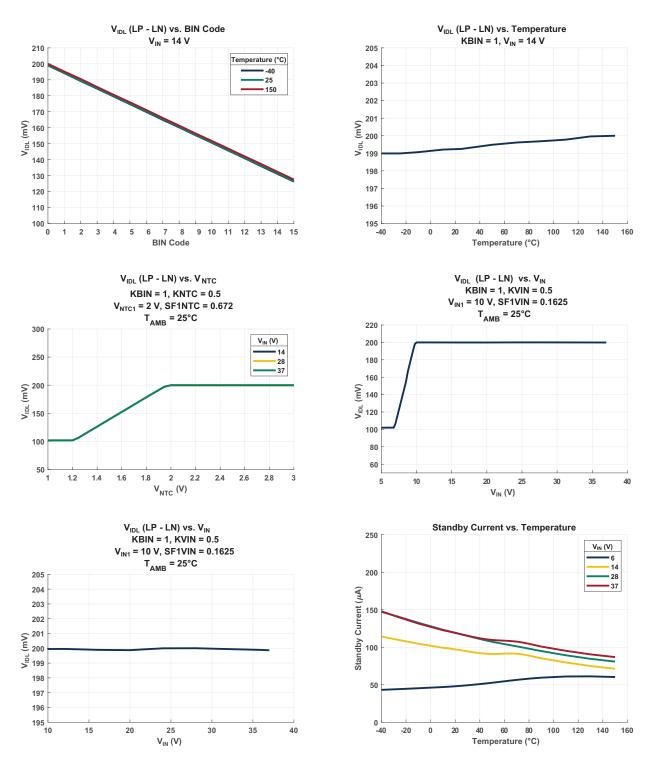

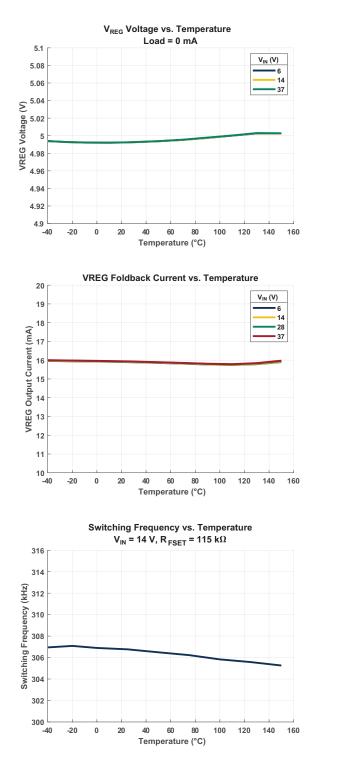

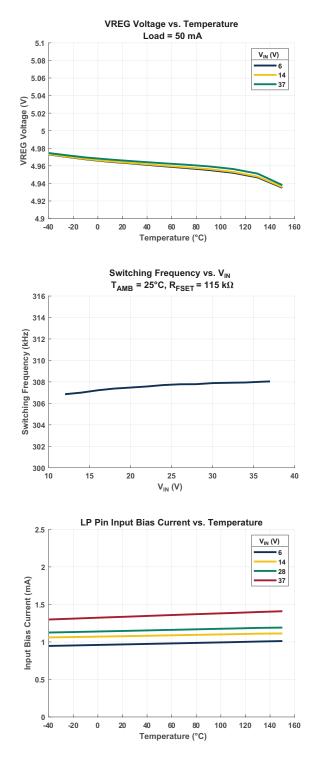

### **TYPICAL OPERATING CHARACTERISTICS**

Allegro MicroSystems 955 Perimeter Road Manchester, NH 03103-3353 U.S.A. www.allegromicro.com

# Multi-Topology Synchronous LED Controller with PWM Dimming and High/Low Intensity Modes

### TYPICAL OPERATING CHARACTERISTICS (continued)

Allegro MicroSystems 955 Perimeter Road Manchester, NH 03103-3353 U.S.A. www.allegromicro.com

# Multi-Topology Synchronous LED Controller with PWM Dimming and High/Low Intensity Modes

### FUNCTIONAL DESCRIPTION

The A80803 is a switch-mode, constant-current controller for high-power LED automotive lighting applications. The controller is based on a programmable fixed-frequency, peak current mode control architecture. The switching power supply can be configured in multiple different switching topologies to suit different application requirements. For each configuration, the appropriate loop compensation and slope compensation passive components must be selected for optimal performance.

The A80803 integrates all necessary control elements to provide a cost-effective solution for a DC-DC controller using external MOSFETs. The maximum LED current is programmable by external sense resistor selection. The LED current can be modulated by an internal PWM signal or can sync to an external PWM signal for direct PWM control on the EN/PWM pin.

The maximum LED current can be adjusted based on one of four binning levels on the BINSEL pin and further derated at low input voltage, high temperature, or both.

The A80803 handles several hardware fault conditions and reports fault status on the active low FFn1 and FFn2 pins. FFn2 can be configured to report or ignore fault conditions and has a programmable assertion delay.

### **Power Converter Operation**

The A80803 provides the necessary blocks to create a switch mode power supply with a single low-side control MOSFET and optionally a high-side synchronous MOSFET, including output current sense, error amplifier with external compensation, resistor programmable switching frequency, and two gate drivers. The EN/PWM pin is a dual function pin, acting as enable if held high, and acting as the PWM input for LED dimming if pulsed with an off-time less than t<sub>DIS.EN/PWM</sub>.

### **Switching Frequency**

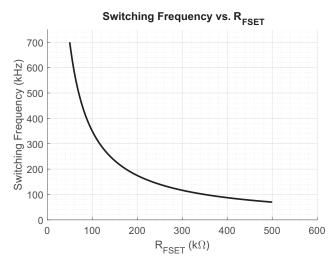

The oscillator for the main power converter is programmable using a resistor to ground and is programmable from 70 to 700 kHz. The relationship between the switching frequency and the programming resistor is shown in Figure 3 and Equation 1 below. Keep  $R_{FSET}$  within the range of 50 to 500 k $\Omega$  as beyond this range the A80803 detects  $R_{FSET}$  open and short faults.

Equation 1:

$R_{FSET} = 35000 \ / \ f_{SW}$  where  $R_{FSET}$  is in k\Omega and  $f_{SW}$  is in kHz

### **Frequency Dithering**

The oscillator also includes dithering which reduces EMI of the power converter. By default, dithering is set to a 10% frequency sweep with 10 kHz modulation. Additional frequency dithering values are available through the SPI interface by accessing the DITH\_FRNG and DITH\_MOD fields in CONFIG0.

#### **Table 1: Dithering Frequency**

| Dithering Frequency | DITH_FRNG[1:0] |

|---------------------|----------------|

| Off                 | 00             |

| ±5%                 | 01             |

| ±10%                | 10             |

| ±15%                | 11             |

#### **Table 2: Dithering Modulation**

| _                    |               |

|----------------------|---------------|

| Dithering Modulation | DITH_MOD[1:0] |

| 10 kHz               | 00            |

| 5 kHz                | 01            |

| 15 kHz               | 10            |

| 22 kHz               | 11            |

### **Power Stage Gate Drivers**

The two main power converter gate drivers provide drive signals to external NMOS devices. The low-side gate driver controls the power flow in the converter. The high-side gate driver allows for efficient delivery of inductor current to the load.

The A80803 includes a boot circuit that allows the use of an NMOS device for the high-side switch. The boot circuit operates at the main converter switching frequency.

#### Soft Start

Soft start can be programmed from 5 to 20 ms in 5 ms steps using the SFST field in the CONFIG1 register.

#### Table 3: Soft Start Time

| Soft Start Time | SFST[1:0] |

|-----------------|-----------|

| 5 ms            | 00        |

| 10 ms           | 01        |

| 15 ms           | 10        |

| 20 ms           | 11        |

During the soft soft time, the A80803 operates asynchronously. This prevents reverse conduction through the high-side power switch in the event of starting into a pre-biased output. Upon the completion of soft start, the A80803 automatically switches to synchronous operation to improve efficiency.

### **Current Sensing**

The control loop depends on two current sense circuits. The inner current-sense loop provides the inductor current information for peak current mode control. A series resistor in this circuit allows the user to program the slope compensation to ensure a stable loop under all operating conditions. The outer loop uses an external current sense resistor to control the DC current in the load.

### **Switch Current Sensing**

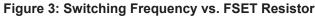

The current through the inner loop is measured by the external sense resistor,  $R_{SP}$ , and the amplifier at the SP pin. The SP pin provides peak-current information to determine duty cycle for the switching converter and a cycle-by-cycle current limit for the switching MOSFET. A resistor at the input of the SP pin,  $R_{SLOPE}$ , sets the slope compensation to prevent subharmonic oscillations at duty cycles greater than 50%.

Figure 4

The current limit of the inner loop is set by the input limit of the sense amplifier,  $V_{IDS}$ , the maximum switch current that has been determined, and the effects of the slope compensation must be taken into account. The operating duty cycle must be calculated at maximum load and minimum operating input voltage. The amount of slope compensation can be calculated for this operating point and can then be added to the actual current-sense signal to determine the maximum signal amplitude before cycle-by-cycle current limiting takes effect. The term di<sub>SLOPE</sub>/dt is the required slope compensation as selected during the design process and programmed with R<sub>SLOPE</sub> as described in section Slope Compensation.

Equation 2:

$$R_{SP} = \frac{V_{IDS,MIN}}{1.2 \left[ I_{LP} + \left( \frac{di_{SLOPE}}{dt} \times \frac{D_{MAX}}{f_{SW}} \right) \right]}$$

Note that the minimum value of  $V_{IDS}$  is used with an additional 20% on the peak current to allow for margin.  $I_{LP}$  is the peak current in the inductor.

### **Slope Compensation**

Slope compensation can be added to the MOSFET current-sense signal on pin SP to prevent subharmonic oscillations where the peak-to-average control error becomes increasingly larger at duty cycles in excess of 50%. A current source is provided at the SP pin as a sawtooth from 0 to 100  $\mu$ A. An external resistor, R<sub>SLOPE</sub>, connected between the SP pin and the source connection of the MOSFET, is used to program the appropriate voltage level to scale the slope compensation for correct use with the appropriate topology and set up conditions that have been adopted.

Equation 3:

$$R_{SLOPE} = \frac{\frac{di_{SLOPE}}{dt} \times R_{SP}}{I_{SLOPE} \times f_{SW}}$$

$di_{\text{SLOPE}}/dt$ , is the required slope compensation based on design parameters.

### Low-Side Switch Current Limit (inner loop)

Cycle-by-cycle current protection is provided through the lowside MOSFET. If an overcurrent occurs for longer than 64 switching clock cycles, the high-side MOSFET drive (PWMOUT) and the low-side MOSFET drive (HSG) are disabled, FFn1 and FFn2 are set low, and the hiccup timer,  $t_{\rm HIC}$ , is initiated for a period of 10 ms. After the hiccup period, an auto-restart is performed under control of the soft-start timer.

### LED Current Sense Resistor

The main outer loop uses an external current sense resistor to control the DC current in the load.

The initial LED current,  $I_{LED,SET}$ , is programmed by the LED sense resistor,  $R_{SL}$ , according to:

Equation 4:

$$R_{SL} = \frac{V_{IDL}}{I_{LED,SET}}$$

$V_{IDL}$  is the differential LED current sense voltage ( $V_{LP} - V_{LN}$ ). See Outer Current Loop Control (LP, LN) section in Electrical Characteristics table. Typical  $V_{IDL} = 200$  mV.

### **LED PWM Dimming**

The LED current can be pulse-width modulated to control the LED brightness while maintaining the same current level through the LEDs during the on-time.

When the EN/PWM pin is driven low for less than  $t_{DIS,EN/PWM}$ , the PWMOUT signal disables the PWM PMOS to open the LED string and the LSG and HSG signals are set to their off-state to stop switching. If the EN/PWM pin is driven low for more than  $t_{DIS,EN/PWM}$  the A80803 enters standby.

### **PWM Dimming Source**

Two options are available for PWM dimming: apply an external PWM signal to the EN/PWM pin or use internal PWM dimming. Select internal or external PWM dimming by controlling the state of the DIMn pin or toggling the PWM\_EN bit in the CONFIG14 register. Note that if the PWM\_EN bit is set it will override the DIMn pin to select internal dimming. Tie the DIMn pin high to control the dimming mode through SPI. The PWM\_EN bit defaults to 0, so if SPI is not used the DIMn pin controls dimming selection; see Table 4 for all combinations of DIMn and PWM\_EN. For the best performance, the minimum recommended PWM dimming duty cycle is 5%.

### Table 4: PWM Dimming Source Selection

| DIMn Pin | PWM_EN Bit | Dimming Source |

|----------|------------|----------------|

| 0        | 0          | Internal       |

| 0        | 1          | Internal       |

| 1        | 0          | External       |

| 1        | 1          | Internal       |

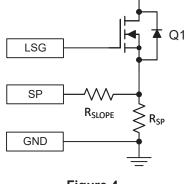

### PWMOUT

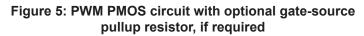

PWMOUT is used to drive a PMOS in series with the LEDs to turn the current through the LEDs on or off. When the PWM signal is high, the PWMOUT pin will drive 5.5 V below the regulator output voltage. When the PWM signal is low, the PWMOUT signal will drive to the regulator output voltage. Connect PWMOUT to the gate of the PWM PMOS to turn the LEDs on when PWM is high and off when PWM is low. There is an undervoltage detect circuit to ensure sufficient regulator output voltage is available to switch the PMOS on. The current drive to the PWM PMOS is configurable through SPI by setting the PWM DRV field in CON-FIG14. Allegro recommends configuring the PWM DRV field to control the PMOS gate drive instead of using a series resistor. This feature provides programmable control of the LED current edge rate while PWM dimming. The PWMOUT current drive setting applies for both external and internal PWM dimming. The PWMOUT pin can drive the gate of the PWM PMOS on and off without a gate-source pullup resistor. If a pullup resistor is required to support system safety requirements, use at least 100 k $\Omega$  for the pullup resistance.

| Table ! | 5: PWMOUT | Pull-Up/Down | Current (   | Configuration |

|---------|-----------|--------------|-------------|---------------|

| 10010 0 |           |              | - ourront v | Johngaradon   |

| Gate Drive Current | PWM_DRV [1:0] | Code |

|--------------------|---------------|------|

| 25 mA              | 00            | 0    |

| 2 mA               | 01            | 1    |

| 0.5 mA             | 10            | 2    |

| 1 mA               | 11            | 3    |

### **External PWM Dimming**

Drive the DIMn pin high to enable external PWM dimming. If SPI is used in the application, the PWM\_EN bit must be set to 0.

Apply a PWM signal to EN/PWM within the specifications in the PWM Dimming and Enable section of the Electrical Characteristics table.

### Internal PWM Dimming

To enable internal PWM dimming drive EN/PWM high to keep the A80803 out of standby, and drive DIMn low or set PWM\_EN bit to 1. If PWM\_EN is set to 1 the state of the DIMn pin is ignored. EN/PWM should be treated as an enable pin when using internal PWM dimming, do not apply a PWM signal.

Four internal PWM frequency options are available and the internal PWM duty cycle is configurable from 0% to 100% in 0.5% steps. See Table 6 for the internal PWM frequency options and CONFIG14-CONFIG15 in Table 41: Register Map for all internal PWM options.

| Internal PWM<br>Frequency | PWM_FREQ [1:0] | Code |

|---------------------------|----------------|------|

| 200 Hz                    | 00             | 0    |

| 250 Hz                    | 01             | 1    |

| 300 Hz                    | 10             | 2    |

| 350 Hz                    | 11             | 3    |

#### Table 6: Internal PWM Frequency Configuration

### **LED Analog Dimming**

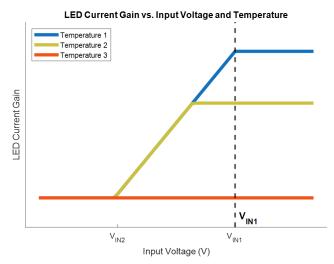

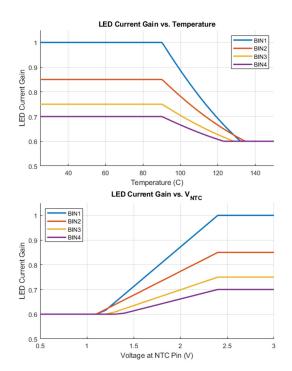

Three analog dimming methods to adjust the maximum LED current are provided within the A80803: LED binning, input voltage derating, and thermal derating. The threshold levels and behavior of these pins are programmed through SPI.

The maximum LED current,  $I_{LED}$ , is set using the external current sense resistor,  $R_{CS}$ , and scaled by adjusting the reference voltage to maintain across  $R_{CS}$ .

When LED binning is used,  $I_{LED}$  is derated by the programmed gain for the selected bin. When input voltage derating is used,  $I_{LED}$  will be scaled by the programmed input voltage foldback gain. When thermal derating is used,  $I_{LED}$  will be scaled by the programmed NTC foldback gain. The three current derating factors are  $k_{BINx}$ ,  $k_{VIN}$  and  $k_{NTC}$ . The maximum LED current is the minimum of  $k_{BIN}$ ,  $k_{VIN}$ , and  $k_{NTC}$  at the system operating voltage and temperature for the active bin.

### **LED Binning**

LED binning applies one of four scaling factors to  $I_{LED}$  and allows for better matching. Drive the BINSEL pin to one of four voltage regions relative to  $V_{CC}$  to select a bin. See Table 7 for the voltage ranges on the BINSEL pin that correspond to each bin. The A80803 will regulate the LED current to  $I_{LED(BINx)}$ , where:

Equation 5:

$I_{\text{LED(BINx)}} = k_{\text{BINx}} \times I_{\text{LED}}$

#### Table 7: BINSEL Voltage Ranges (V<sub>CC</sub>)

| BINx | V <sub>BINSEL(MIN)</sub> | V <sub>BINSEL(MAX)</sub> |

|------|--------------------------|--------------------------|

| 1    | 0.62 × V <sub>CC</sub>   | V <sub>CC</sub>          |

| 2    | 0.45 × V <sub>CC</sub>   | 0.6 × V <sub>CC</sub>    |

| 3    | 0.25 × V <sub>CC</sub>   | $0.4 \times V_{CC}$      |

| 4    | GND                      | 0.2 × V <sub>CC</sub>    |

The resistor divider from VCC should draw less than 1 mA. If resistor values that would draw more than 1 mA are required, the voltage divider can be tied to VREG using the following table to account for the difference between  $V_{REG}$  and  $V_{CC}$ .

Table 8: BINSEL Voltage Ranges (V<sub>REG</sub>)

| BINx | V <sub>BINSEL(MIN)</sub> | V <sub>BINSEL(MAX)</sub> |

|------|--------------------------|--------------------------|

| 1    | 0.41 × V <sub>REG</sub>  | 0.66 × V <sub>REG</sub>  |

| 2    | 0.30 × V <sub>REG</sub>  | 0.40 × V <sub>REG</sub>  |

| 3    | 0.17 × V <sub>REG</sub>  | 0.27 × V <sub>REG</sub>  |

| 4    | GND                      | 0.13 × V <sub>REG</sub>  |

Each bin has its own 4-bit register field to store its scaling factor,  $k_{BINx}$ , in the CONFIG2 and CONFIG3 registers. The scale factors are programmable through SPI from 100% to 62.5% of  $I_{LED}$  in 2.5% steps. See Table 9 for examples of BINx codes to achieve a  $k_{BINx}$  scale factor. Calculate the bin gain,  $k_{BINx}$ , with the following equation:

Equation 6:

$k_{\text{BINx}} = 1 - 0.025 \times \text{code}$

for  $0 \le \text{code} \le 15$

Or, to find the code for a specific gain:

Equation 7:

$code = (1 - k_{BINx}) / 0.025$

### for $0.625 \le k_{BINx} \le 1$

#### Table 9: BINx Scale Factor

| k <sub>BINx</sub> | BINx [3:0] | Code |

|-------------------|------------|------|

| 1                 | 0000       | 0    |

| 0.975             | 0001       | 1    |

| 0.950             | 0010       | 2    |

|                   |            |      |

| 0.650             | 1110       | 14   |

| 0.625             | 1111       | 15   |

# Multi-Topology Synchronous LED Controller with PWM Dimming and High/Low Intensity Modes

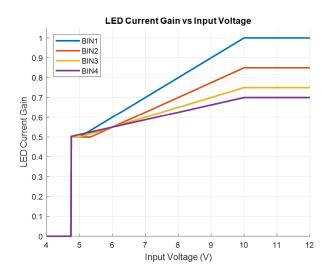

### Input Voltage Derating

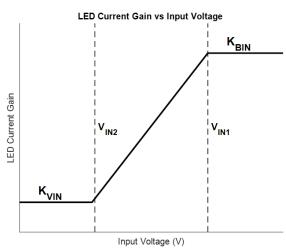

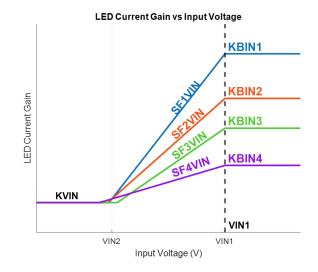

The LED current,  $I_{LED}$ , can be scaled down linearly as input voltage decreases up to a maximum derating set by  $k_{VIN}$ , programmable from a gain of 1 to a gain of 0.2 in CONFIG13. The shape of the input voltage derating is defined by the bin gain,  $k_{BIN}$ , a voltage level to start derating,  $V_{IN1}$ , a voltage level to stop derating,  $V_{IN2}$ , and the derating gain at  $V_{IN2}$ ,  $k_{VIN}$ . The derating term definitions are shown in Figure 6.  $V_{IN2}$  should be 2 to 5 V lower than  $V_{IN1}$ . See Table 11 for available values of  $k_{VIN}$  and Table 12 for available values for  $V_{IN1}$ , or CONFIG13 in the register map.

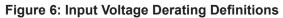

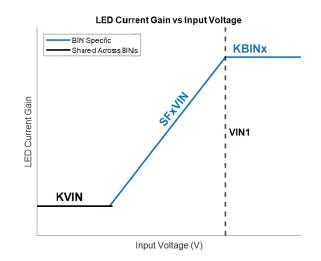

The A80803 stores the value for V<sub>IN1</sub> as register field VIN1 in CONFIG13. Instead of storing V<sub>IN2</sub> directly it stores the slope-factor to achieve the desired V<sub>IN2</sub>, SFxVIN in CONFIG9 - CONFIG12. See Figure 7 for the voltage derating definition terms used in the A80803 registers, where "x" represents the bin number.

### Figure 7: Input Voltage Derating Programming Definitions

All bins share a common  $V_{IN1}$  and  $k_{VIN}$ , while each bin has a separate slope-factor field, allowing different bins to have different derating slopes, as shown in Figure 8.

### Figure 8: Input Voltage Derating Programming For Multiple Bins

Calculate the slope-factor from the following equation:

Equation 8:

$$slope = \frac{k_{BIN} - k_{VIN}}{V_{IN1} - V_{IN2}}$$

Calculate register field SFxVIN from Equation 9 or find the closest available value in Table 16 to the calculated slope-factor.

Equation 9:

$$SFxVIN = round\left(\frac{slope}{0.0125} - 1\right)$$

Using the selected slope-factor, SFxVIN, the actual  $\rm V_{\rm IN2}$  voltage can be found with the following equation:

Equation 10:

$$V_{IN2(Actual)} = V_{IN1} - \frac{k_{BIN} - k_{VIN}}{SF}$$

When input voltage,  $V_{IN}$ , is greater than  $V_{IN1}$ ,  $I_{LED}$  is only scaled by the selected bin. When  $V_{IN}$  is less than  $V_{IN2}$ ,  $I_{LED}$  is scaled by  $k_{VIN}$ . When  $V_{IN2} < V_{IN} < V_{IN1}$ , the LED current is scaled by the slope-factor and  $V_{IN}$ . Table 10 shows the LED current scaling factor based on input voltage.

Table 10: Input Voltage Derating LED Current Scale Factor

| Input Voltage (V <sub>IN</sub> )   | I <sub>LED</sub> Scale Factor                  |

|------------------------------------|------------------------------------------------|

| V <sub>IN</sub> > V <sub>IN1</sub> | k <sub>BIN</sub>                               |

| $V_{IN2} < V_{IN} < V_{IN1}$       | $k_{VIN} + [SFxVIN \times (V_{IN} - V_{IN2})]$ |

| V <sub>IN</sub> < V <sub>IN2</sub> | k <sub>VIN</sub>                               |

#### Table 11: Values for k<sub>VIN</sub>

| k <sub>vin</sub> | KVIN[2:0] | Code |

|------------------|-----------|------|

| 1                | 000       | 0    |

| 0.8              | 001       | 1    |

| 0.7              | 010       | 2    |

| 0.6              | 011       | 3    |

| 0.5              | 100       | 4    |

| 0.4              | 101       | 5    |

| 0.3              | 110       | 6    |

| 0.2              | 111       | 7    |

#### Table 12: Values for V<sub>IN1</sub>

| V <sub>IN1</sub> | VIN1[2:0] | Code |

|------------------|-----------|------|

| 7.5 V            | 000       | 0    |

| 8.0 V            | 001       | 1    |

| 8.5 V            | 010       | 2    |

| 9.0 V            | 011       | 3    |

| 9.5 V            | 100       | 4    |

| 10.0 V           | 101       | 5    |

| 10.5 V           | 110       | 6    |

| 11.0 V           | 111       | 7    |

#### **Thermal Derating**

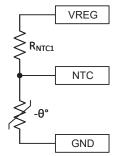

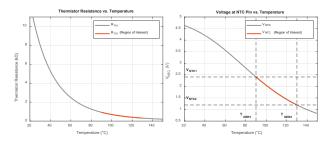

The LED current,  $I_{LED}$ , can be scaled down linearly as the voltage at the NTC pin decreases, up to a maximum derating set by  $k_{NTC}$ . This feature is intended to be used with a voltage divider at the NTC pin between a resistor and a negative temperature coefficient thermistor as shown in Figure 9. Applications that do not require thermal derating should tie the NTC pin to a voltage higher than the programmed VNTC1, such as tying to VREG.

Figure 9: NTC Derating Application Circuit

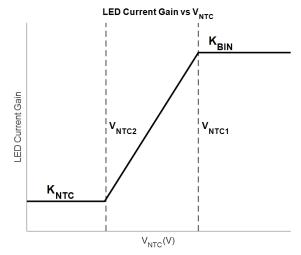

The shape of the derating is defined by the bin gain,  $k_{BIN}$ , a voltage level to start derating,  $V_{NTC1}$ , a voltage level to stop derating,  $V_{NTC2}$ , and the derating gain at  $V_{NTC2}$ ,  $k_{NTC}$ . The derating term definitions are shown in Figure 10.

**Figure 10: NTC Derating Definitions**

The voltage levels  $V_{NTC1}$  and  $V_{NTC2}$  represent the temperature to start derating and the temperature to stop derating respectively, based on the voltage at the NTC pin when used with a thermistor in the circuit shown in Figure 9. The exact values of  $V_{NTC1}$  and  $V_{NTC2}$  depend on the properties of the selected thermistor. See the Thermal Derating Example section for more details on calculating  $V_{NTC1}$  and  $V_{NTC2}$  for a given thermistor.

The A80803 stores the value for  $V_{NTC1}$  as register field  $V_{NTC1}$  in CONFIG4, and instead of storing  $V_{NTC2}$  directly, it stores the slope factor to achieve the desired  $V_{NTC2}$ , SFxNTC in CONFIG5 – CONFIG8. The gain term  $k_{NTC}$  is stored as KNTC in CONFIG4. See Figure 7 for the voltage derating definition terms used in the A80803 registers.

Figure 11: NTC Derating Programming Definitions

For proper operation,  $k_{\rm NTC}$  should be less than  $k_{\rm BINx}$  and  $V_{\rm NTC2}$  should be at least 0.5 V lower than  $V_{\rm NTC1}$ . See Table 14 for available values for  $k_{\rm NTC}$ , and Table 15 and Equation 14 for available values of  $V_{\rm NTC1}$ .

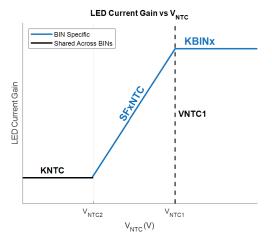

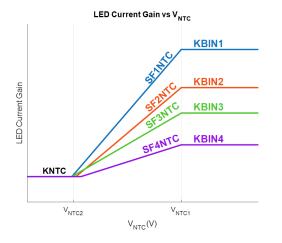

All bins share a common  $V_{NTC1}$  and  $k_{NTC}$ , while each bin has a separate slope factor field, SFxNTC, allowing different bins to have different derating slopes to reach the same final derated value, as shown in Figure 4.

Calculate the slope factor for NTC derating of a specific bin from the following equation:

Equation 11:

$$slope = \frac{k_{BIN} - k_{NTC}}{V_{NTC1} - V_{NTC2}}$$

Calculate the register field SFxNTC from Equation 12 or the closest available value in Table 17 to the calculated slope-factor.

Equation 12:

$$SFxNTC = round\left(\frac{slope}{0.032} - 1\right)$$

Using the selected slope-factor, SFxNTC, the actual  $V_{\rm NTC2}$  voltage can be found with the following equation:

Equation 13:

$$V_{NTC2(Actual)} = V_{NTC1} - \frac{k_{BIN} - k_{NTC}}{SF}$$

where SF is the selected slope-factor.

When the voltage at the NTC pin,  $V_{NTC}$ , is greater than  $V_{NTC1}$ ,  $I_{LED}$  is only scaled by the selected bin. When  $V_{NTC}$  is less than  $V_{NTC2}$ ,  $I_{LED}$  is scaled by  $k_{NTC}$ . When  $V_{NTC2} < V_{NTC} < V_{NTC1}$ , the LED current is scaled by the slope-factor and  $V_{NTC}$ . Table 13 shows the LED current scaling factor based on NTC pin voltage.

#### Table 13: NTC Derating LED Current Scale Factor

| NTC Pin Voltage (V <sub>NTC</sub> )                      | I <sub>LED</sub> Scale Factor                   |

|----------------------------------------------------------|-------------------------------------------------|

| V <sub>NTC &gt;</sub> V <sub>NTC1</sub>                  | k <sub>BIN</sub>                                |

| V <sub>NTC2</sub> < V <sub>NTC</sub> < V <sub>NTC1</sub> | $k_{NTC}$ + [SFxNTC × ( $V_{NTC} - V_{NTC2}$ )] |

| V <sub>NTC</sub> < V <sub>NTC2</sub>                     | k <sub>NTC</sub>                                |

### Table 14: Values for k<sub>NTC</sub>

| k <sub>NTC</sub> | K <sub>NTC</sub> [1:0] | Code |

|------------------|------------------------|------|

| 0.8              | 00                     | 0    |

| 0.7              | 01                     | 1    |

| 0.6              | 01                     | 2    |

| 0.5              | 11                     | 3    |

### Table 15: Values for VNTC1

| V <sub>NTC1</sub> | V <sub>NTC1</sub> [4:0] | Code |

|-------------------|-------------------------|------|

| 1.20              | 00000                   | 0    |

| 1.25              | 00001                   | 1    |

| 1.30              | 00010                   | 2    |

|                   |                         |      |

| 2.70              | 11110                   | 30   |

| 2.75              | 11111                   | 31   |

# Multi-Topology Synchronous LED Controller with PWM Dimming and High/Low Intensity Modes

Equation 14:

$$\label{eq:VNTC1} \begin{split} V_{NTC1} &= 1.2 + 0.05 \times code \\ & \text{for } 0 \leq code \leq 31 \end{split}$$

### **Combined Analog Dimming**

All three analog dimming functions work together to regulate the LED current to the minimum of the active bin gain, the input voltage derating gain, and the NTC derating gain.

Equation 15:

$I_{\text{LED}} = \min([I_{\text{LED(BIN)}}, I_{\text{LED(VIN)}}, I_{\text{LED(NTC)}}])$

where:

$$\begin{split} I_{LED(BIN)} \text{ is } I_{LED} \text{ for the active BIN,} \\ I_{LED(VIN)} \text{ is } I_{LED} \text{ for the current } V_{IN}, \\ I_{LED(NTC)} \text{ is } I_{LED} \text{ for the current } V_{NTC}. \end{split}$$

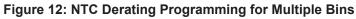

Figure 13 shows the effect of the combined analog dimming at three different temperatures with varied input voltage. At Temperature 1,  $I_{LED}$  is only limited by input voltage. At Tem-

perature 2,  $I_{LED}$  is limited by temperature until it meets the input voltage derating limit. Finally, at Temperature 3, the LED current is limited by temperature at all input voltages.

Figure 13: Effect of Combined Analog Dimming

# Multi-Topology Synchronous LED Controller with PWM Dimming and High/Low Intensity Modes

#### Table 16: Slope-Factors for Input Voltage Derating

| Slope Factor | SFxVIN[4:0] | Code |

|--------------|-------------|------|

| 0.0125       | 00000       | 0    |

| 0.0250       | 00001       | 1    |

| 0.0375       | 00010       | 2    |

| 0.0500       | 00011       | 3    |

| 0.0625       | 00100       | 4    |

| 0.0750       | 00101       | 5    |

| 0.0875       | 00110       | 6    |

| 0.1000       | 00111       | 7    |

| 0.1125       | 01000       | 8    |

| 0.1250       | 01001       | 9    |

| 0.1375       | 01010       | 10   |

| 0.1500       | 01011       | 11   |

| 0.1625       | 01100       | 12   |

| 0.1750       | 01101       | 13   |

| 0.1875       | 01110       | 14   |

| 0.2000       | 01111       | 15   |

| 0.2125       | 10000       | 16   |

| 0.2250       | 10001       | 17   |

| 0.2375       | 10010       | 18   |

| 0.2500       | 10011       | 19   |

| 0.2625       | 10100       | 20   |

| 0.2750       | 10101       | 21   |

| 0.2875       | 10110       | 22   |

| 0.3000       | 10111       | 23   |

| 0.3125       | 11000       | 24   |

| 0.3250       | 11001       | 25   |

| 0.3375       | 11010       | 26   |

| 0.3500       | 11011       | 27   |

| 0.3625       | 11100       | 28   |

| 0.3750       | 11101       | 29   |

| 0.3875       | 11110       | 30   |

| 0.4000       | 11111       | 31   |

#### Table 17: Slope-Factors for NTC Derating

| Slope Factor | SFxNTC[4:0] | Code |

|--------------|-------------|------|

| 0.032        | 00000       | 0    |

| 0.064        | 00001       | 1    |

| 0.096        | 00010       | 2    |

| 0.128        | 00011       | 3    |

| 0.160        | 00100       | 4    |

| 0.192        | 00101       | 5    |

| 0.224        | 00110       | 6    |

| 0.256        | 00111       | 7    |

| 0.288        | 01000       | 8    |

| 0.320        | 01001       | 9    |

| 0.352        | 01010       | 10   |

| 0.384        | 01011       | 11   |

| 0.416        | 01100       | 12   |

| 0.448        | 01101       | 13   |

| 0.480        | 01110       | 14   |

| 0.512        | 01111       | 15   |

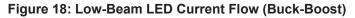

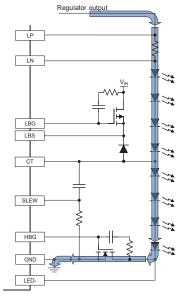

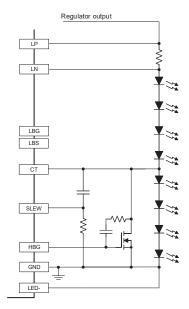

| 0.544        | 10000       | 16   |