#### FEATURES AND BENEFITS

- 5.5 to 85 V supply voltage operating range

- 58 V part variant available (A89120)

- 3.3 V or 5 V low quiescent current (I<sub>Q</sub>; typically, 8.5 μA) low-dropout (LDO) regulator, active during sleep mode

- Three-phase bridge MOSFET driver with bootstrap gate drive for N-channel MOSFET bridge

- Charge pump for low-supply-voltage operation.

- Cross-conduction protection with adjustable dead time

- Bridge control by direct logic inputs for maximum flexibility

Continued on next page...

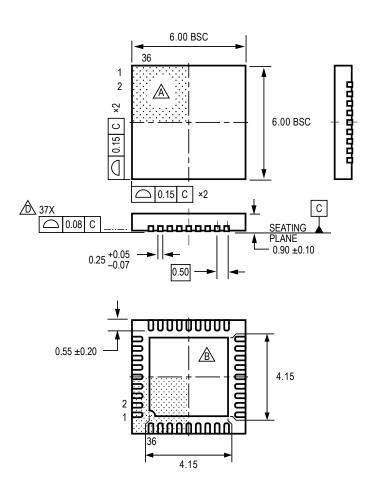

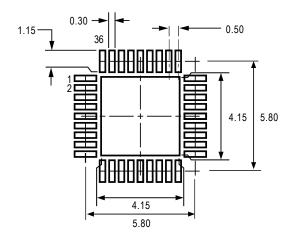

36-contact QFN with exposed thermal pad (suffix EV)

#### **DESCRIPTION**

The A89121 is designed to satisfy the demanding power requirements of brushless DC (BLDC) power tools from 12 V to 56 V with ultra-low current consumption.

The A89121 is optimized for pulse-width-modulated (PWM) current control of three-phase BLDC motors and is capable of high-current, robust gate driving for six external N-channel power MOSFETs. An internal charge pump ensures full gate drive capability over the full supply-voltage range, from 5.5 V to 85 V. A bootstrap capacitor is used to generate a supply

Continued on next page...

#### **TYPICAL APPLICATIONS**

- Cordless power tools

- Optimized for 12 V to 56 V-battery BLDC motor modules

- 48 V e-bikes

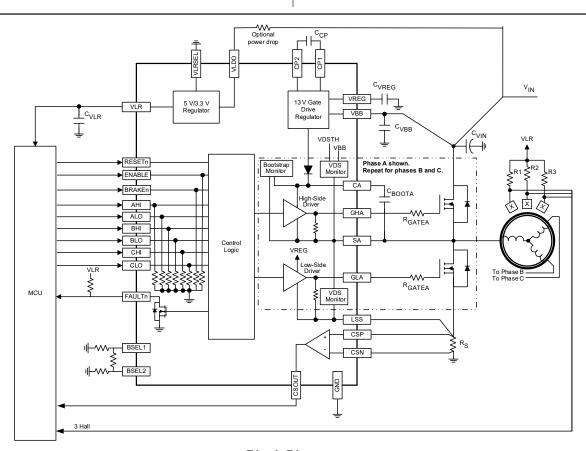

**Block Diagram**

# 85 V Three-Phase MOSFET Driver

#### **FEATURES AND BENEFITS (continued)**

- Differential current-sense amplifier

- ☐ Adjustable gain and offset

- □ 1 microsecond settling time

- Drand-to-source voltage (V<sub>DS</sub>), undervoltage lockout (UVLO), and thermal shutdown diagnostic

- · Latched thermal shutdown (TSD) with fault output

### **DESCRIPTION** (continued)

voltage greater than the source voltage of the high-side MOSFET. Internal circuit protection includes latched thermal shutdown, crossover current protection, undervoltage lockout, and short-circuit protection. Full control is provided over all six power MOSFETs in the three-phase bridge, allowing motors to be driven with block commutation or sinusoidal excitation.

Bridge current can be measured using an integrated current-sense amplifier with a below-ground common-mode range that allows it to be used in low-side current-sense applications. Gain and offset are defined by external resistors.

The device includes an efficient low-dropout (LDO) regulator to provide 3.3 V or 5 V to external circuitry.

The A89121 is supplied in a leadless 6 mm  $\times$  6 mm  $\times$  0.9 mm, 36-pin quad-flat no-lead (QFN) package (suffix EV) with exposed power tab for enhanced thermal performance. The package is lead (Pb) free, with 100% matte-tin leadframe plating.

#### **SELECTION GUIDE**

| Part Number | Rated Voltage | Packing                     | Package                                                                    |

|-------------|---------------|-----------------------------|----------------------------------------------------------------------------|

| A89121GEVSR | 85            | 1500 pieces per 13-in. reel | 6 mm × 6 mm; 0.9 mm nominal height<br>36-lead QFN with exposed thermal pad |

### **SPECIFICATIONS**

#### ABSOLUTE MAXIMUM RATINGS: With respect to GND

| Characteristic                             | Symbol                             | Notes         | Rating                                             | Unit |

|--------------------------------------------|------------------------------------|---------------|----------------------------------------------------|------|

| Load Supply Voltage                        | V <sub>VBBMAX</sub>                |               | -0.3 to 90                                         | V    |

| Analog Output                              | V <sub>VLR</sub>                   |               | -0.3 to 6                                          | V    |

| Terminal VREG                              | $V_{VREG}$                         |               | -0.3 to 18                                         | V    |

| Terminal CP1                               | V <sub>CP1</sub>                   |               | -0.3 to 16                                         | V    |

| Terminal CP2                               | V <sub>CP2</sub>                   |               | $(V_{CP1} - 0.3)$ to $(V_{VREG} + 0.3)$            | V    |

| Logic Inputs                               | V <sub>IN</sub>                    |               | -0.3 to 6                                          | V    |

| FAULTn Output                              | V <sub>FAULTn</sub>                |               | -0.3 to 6                                          | V    |

| Sense Amplifier Inputs                     | V <sub>CSP/</sub> V <sub>CSN</sub> |               | -4 to 6.5                                          | V    |

| Sense Amplifier Outputs                    | V <sub>CSO</sub>                   |               | -0.3 to 6.5                                        | V    |

| Terminals CA, CB, CC                       | V <sub>CX</sub>                    |               | -0.3 to (V <sub>VREG</sub> + V <sub>VBBMAX</sub> ) | V    |

| Terminals GHA, GHB, GHC                    | V <sub>GHX</sub>                   |               | $(V_C - 16)$ to $(V_C + .3)$                       | V    |

|                                            |                                    | Transient [1] | -18 to (V <sub>C</sub> +.3)                        | V    |

| Tamasinala CA CB CC                        |                                    |               | $(V_C - 16)$ to $V_{VBBMAX}$                       | V    |

| Terminals SA, SB, SC                       | V <sub>SX</sub>                    | Transient [1] | -18 to (V <sub>C</sub> +.3)                        | V    |

| Terminale CLA CLB CLC                      |                                    |               | (V <sub>VREG</sub> – 16) to 18                     | V    |

| Terminals GLA, GLB, GLC                    | $V_{GLX}$                          | Transient [1] | -8 to 18                                           | V    |

| Terminal LSS                               | V                                  |               | (V <sub>VREG</sub> – 16) to 18                     | V    |

| Terminal LSS                               | V <sub>LSS</sub>                   | Transient [1] | -8 to 18                                           | V    |

| Terminal VLDO                              | $V_{LDO}$                          |               | −0.3 to V <sub>VBBMAX</sub>                        | V    |

| Terminal VLRSEL                            | V <sub>VLRSEL</sub>                |               | -0.3 to 6                                          | V    |

| Maximum Continuous Junction<br>Temperature | T <sub>J</sub>                     |               | ≤150                                               | °C   |

| Storage Temperature Range                  | T <sub>s</sub>                     |               | -55 to 150                                         | °C   |

| Operating Temperature Range                | T <sub>A</sub>                     | Range G       | -40 to 125                                         | °C   |

<sup>[1]</sup> Duration less than 1  $\mu s$

### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol          | Test Conditions                                 | Value | Unit |

|----------------------------|-----------------|-------------------------------------------------|-------|------|

| Package Thermal Resistance | $R_{\theta JA}$ | EV package, 4-layer PCB based on JEDEC standard | 27    | °C/W |

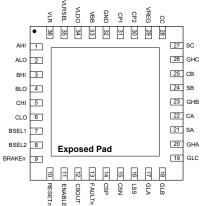

### PINOUT DIAGRAMS AND TERMINAL LIST TABLE

EV Package Pinouts

#### **Terminal List Table**

|             |        | ubic 5 F 7 5                                                                                                                                                                                    |

|-------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Num-<br>ber | Name   | Function                                                                                                                                                                                        |

| -           | PAD    | Thermal pad; connect to GND                                                                                                                                                                     |

| 1           | AHI    | Logic input: Direct control for high-side output A. Refer to logic decode table in Functional Description.                                                                                      |

| 2           | ALO    | Logic input: Direct control for low-side output A. Refer to logic decode table in Functional Description.                                                                                       |

| 3           | ВНІ    | Logic input: Direct control for high-side output B. Refer to logic decode table in Functional Description.                                                                                      |

| 4           | BLO    | Logic input: Direct control for low-side output B. Refer to logic decode table in Functional Description.                                                                                       |

| 5           | CHI    | Logic input: Direct control for high-side output C. Refer to logic decode table in Functional Description.                                                                                      |

| 6           | CLO    | Logic input: Direct control for low-side output C. Refer to logic decode table in Functional Description.                                                                                       |

| 7           | BSEL1  | Used in association with BSEL2 by detection circuitry to determine the values for the V <sub>DS</sub> threshold, offset, and gain of the current-sense amplifier.                               |

| 8           | BSEL2  | Used in association with BSEL1 by the detection circuitry to determine the values for the V <sub>DS</sub> threshold, offset, and gain of current-sense amplifier.                               |

| 9           | BRAKEn | Active low braking input; turns all low sides ON                                                                                                                                                |

| 10          | RESETn | Logic input to assert sleep mode                                                                                                                                                                |

| 11          | ENABLE | Active high logic input, enables output drivers                                                                                                                                                 |

| 12          | CSOUT  | Current-sense amplifier output                                                                                                                                                                  |

| 13          | FAULTn | Active low fault output. Open drain; requires external pull up resistor.                                                                                                                        |

| 14          | CSP    | Current-sense amplifier input                                                                                                                                                                   |

| 15          | CSN    | Current-sense amplifier input                                                                                                                                                                   |

| 16          | LSS    | Low-side source: low-side return path for discharge of the capacitance of the MOSFET gates, connected to the common sources of the low-side external MOSFETs through a low-impedance PCB trace. |

| 17          | GLA    | Gate drive for external low-side MOSFET connected to phase A.                                                                                                                                   |

| 18          | GLB    | Gate drive for external low-side MOSFET connected to phase B                                                                                                                                    |

| 19          | GLC    | Gate drive for external low-side MOSFET connected to phase C.                                                                                                                                   |

| Num-<br>ber | Name   | Function                                                                                                                                                                                                                                                                                                                                              |

|-------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20          | GHA    | Gate drive for external high-side MOSFET connected to phase A.                                                                                                                                                                                                                                                                                        |

| 21          | SA     | Negative supply for high-side gate drive. Connect to motor for phase A.                                                                                                                                                                                                                                                                               |

| 22          | CA     | Positive supply for high-side drive. Connect ceramic capacitor from CA to SA.                                                                                                                                                                                                                                                                         |

| 23          | GHB    | Gate drive for external high-side MOSFET connected to phase B.                                                                                                                                                                                                                                                                                        |

| 24          | SB     | Negative supply for high-side gate drive. Connect to motor for Phase B.                                                                                                                                                                                                                                                                               |

| 25          | СВ     | Positive supply for high-side drive. Connect ceramic capacitor from CB to SB.                                                                                                                                                                                                                                                                         |

| 26          | GHC    | Gate drive for external high -side MOSFET connected to phase C.                                                                                                                                                                                                                                                                                       |

| 27          | SC     | Negative supply for high-side gate drive. Connect to motor for phase C.                                                                                                                                                                                                                                                                               |

| 28          | СС     | Positive supply for high-side drive. Connect ceramic capacitor from CC to SC.                                                                                                                                                                                                                                                                         |

| 29          | VREG   | 13 V gate-drive supply regulator output. when the motor phase outputs are driven low, the high-side bootstrap capacitors are charged from VREG. VREG also directly powers low-side gate drive circuits. A sufficiently large storage capacitor must be connected between this terminal and the GND terminal to provide the transient charging current |

| 30          | CP2    | Charge-pump capacitor terminal                                                                                                                                                                                                                                                                                                                        |

| 31          | CP1    | Charge-pump capacitor terminal                                                                                                                                                                                                                                                                                                                        |

| 32          | GND    | Ground                                                                                                                                                                                                                                                                                                                                                |

| 33          | VBB    | Supply voltage input: Connect 0.22 µF (CVB2) X5R or X7R ceramic capacitor locally between VBB and GND, as close to the IC as practical.                                                                                                                                                                                                               |

| 34          | VLDO   | LDO supply input                                                                                                                                                                                                                                                                                                                                      |

| 35          | VLRSEL | Select VLR regulator output: for 3.3 V, connect to GND; for 5 V, connect to VLR.                                                                                                                                                                                                                                                                      |

| 36          | VLR    | 5 V or 3.3 V/30 mA regulator output used to power external microprocessor. Stabilize with typical 4.7 µF X5R or X7R ceramic capacitor.                                                                                                                                                                                                                |

### **CHARACTERISTIC PERFORMANCE**

**ELECTRICAL CHARACTERISTICS:** Valid for  $T_A = -40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$  V<sub>VBB</sub> = 5.5 V to 85 V (unless noted otherwise)

| Characteristics Symbol          |                    | Test Conditions                                                                                                                                                    | Min.  | Тур. | Max.  | Unit |

|---------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| Supply and Reference            |                    |                                                                                                                                                                    |       |      |       |      |

| Operating Voltage Range         | $V_{VBB}$          | Operating, outputs active                                                                                                                                          | 5.5   | _    | 85    | V    |

| Matar Supply Current [2]        | T                  | V <sub>VBB</sub> = 24 V, f <sub>PWM</sub> = 20 kHz, C <sub>LOAD</sub> = 10 nF                                                                                      | _     | 24   | 28    | mA   |

| Motor Supply Current [2]        | $I_{VBB}$          | V <sub>VBB</sub> = 24 V, outputs disabled                                                                                                                          | _     | 7.5  | 10    | mA   |

| LDO Ground Current During SLEEP | T                  | $V_{VBB}$ = 24 V, $I_{VLR}$ = 100 $\mu$ A, $V_{RESETn}$ < 0.3 V, $T_J$ = 25°C [1]                                                                                  | -     | 8.5  | 11    | μΑ   |

| Mode [2]                        | I <sub>SLEEP</sub> | $V_{VBB}$ = 24 V, $I_{VLR}$ = 100 $\mu$ A, $V_{RESETn}$ < 0.3 V, -40°C ≤ $T_J$ ≤ 125°C                                                                             | _     | -    | 15    | μΑ   |

|                                 | V <sub>VREG</sub>  | $V_{VBB} > 6.5 \text{ V}, 0 \text{ mA} \le I_{VREG} \le 33 \text{ mA}$                                                                                             | 9     | 13   | 14    | V    |

| VREG Output Voltage             |                    | $6 \text{ V} < \text{V}_{\text{VBB}} \le 6.5 \text{ V}, 0 \text{ mA} \le I_{\text{VREG}} \le 20 \text{ mA}$                                                        | 9     | -    | 14    | V    |

|                                 |                    | $6 \text{ V} < \text{V}_{\text{VBB}} \le 6.5 \text{ V}, 0 \text{ mA} \le I_{\text{VREG}} \le 15 \text{ mA}$                                                        | 9     | -    | 14    | V    |

| VREG Output Capacitance [1]     | C <sub>VREG</sub>  |                                                                                                                                                                    | 2     | _    | 22    | μF   |

| VLR Output Capacitance [1]      | C <sub>VLR</sub>   |                                                                                                                                                                    | 2.3   | 4.7  | 7     | μF   |

| Output Voltage                  | V <sub>VLR</sub>   | $5.5 \text{ V} \le \text{V}_{\text{VBB}} \le 85 \text{ V}, \text{V}_{\text{VLRSEL}} = \text{GND},$ $0 \text{ mA} \le I_{\text{OUT}} \le 40 \text{ mA}$             | 3.135 | 3.3  | 3.465 | V    |

|                                 |                    | $6.5 \text{ V} \le \text{V}_{\text{VBB}} \le 85 \text{ V}, \text{V}_{\text{VLRSEL}} = \text{V}_{\text{VLR}}, \\ 0 \text{ mA} \le I_{\text{OUT}} \le 40 \text{ mA}$ | 4.75  | 5    | 5.25  | V    |

| Output Overcurrent Limit [2]    | I <sub>OCL</sub>   | V <sub>VLR</sub> = 0 V                                                                                                                                             | 60    | _    | 120   | mA   |

# 85 V Three-Phase MOSFET Driver

## **ELECTRICAL CHARACTERISTICS:** Valid for $T_A = -40^{\circ}\text{C}$ to 125°C $V_{VBB} = 5.5 \text{ V}$ to 85 V (unless noted otherwise)

| Characteristics                        | Symbol                | Test Conditions                                                  | Min.                  | Тур. | Max.                  | Unit |  |  |  |

|----------------------------------------|-----------------------|------------------------------------------------------------------|-----------------------|------|-----------------------|------|--|--|--|

| GATE DRIVE                             |                       |                                                                  |                       |      |                       |      |  |  |  |

| Destatues Diede Femiliand Veltane      | .,                    | I <sub>D</sub> = 1 mA                                            | 0.4                   | 0.7  | 1                     | V    |  |  |  |

| Bootstrap Diode Forward Voltage        | V <sub>fBOOT</sub>    | I <sub>D</sub> = 100 mA                                          | 1.5                   | 2.2  | 3.3                   | V    |  |  |  |

| Bootstrap Diode Resistance             | R <sub>D</sub>        | $R_{D(100mA)} = (V_{fBOOT(150 mA)} - V_{fBOOT(50mA)})/100 mA$    | 6                     | 11   | 25                    | Ω    |  |  |  |

| Bootstrap Diode Current Limit [2]      | I <sub>DBOOT</sub>    |                                                                  | 250                   | 500  | 750                   | mA   |  |  |  |

| High-Side Gate Drive Output            | V <sub>GSH(H)</sub>   | Bootstrap fully charged, C <sub>LOAD</sub> = 10 nF               | V <sub>CX</sub> - 0.2 | _    | -                     | V    |  |  |  |

| night-side Gate Drive Output           | V <sub>GSH(L)</sub>   | I <sub>GATE</sub> < 10 μA                                        | _                     | _    | V <sub>SX</sub> + 0.3 | V    |  |  |  |

| Low-Side Gate Drive Output             | V <sub>GSL(H)</sub>   | V <sub>VREG</sub> = 13 V, C <sub>LOAD</sub> = 10 nF              | $V_{VREG} - 0.2$      | _    | _                     | V    |  |  |  |

| Low-Side Gate Drive Output             | V <sub>GSL(L)</sub>   | I <sub>GATE</sub> < 10 μA                                        | _                     | _    | 0.3                   | V    |  |  |  |

| Gate Drive Pull-Up Resistance          | R <sub>GATE(ON)</sub> | I <sub>GHX</sub> = 150 mA, T <sub>J</sub> = 25° C <sup>[1]</sup> | _                     | 6.8  | _                     | Ω    |  |  |  |

| Gate Drive Full-Op Nesistance          | UP                    | I <sub>GHX</sub> = 150 mA, T <sub>J</sub> = 125° C               | 5.5                   | 9.75 | 14.5                  | Ω    |  |  |  |

| Pull-Up Peak Source Current [1][2]     | I <sub>PUPK</sub>     |                                                                  | _                     | 0.9  | _                     | Α    |  |  |  |

| Gate Drive Pull-Down Resistance        | R <sub>GATE(ON)</sub> | I <sub>GLX</sub> = 150 mA, T <sub>J</sub> = 25° C [1]            | _                     | 1.8  | -                     | Ω    |  |  |  |

| Gate Drive Full-Down Resistance        | DOWN                  | I <sub>GLX</sub> = 150 mA, T <sub>J</sub> = 125° C               | 2                     | 3    | 4                     | Ω    |  |  |  |

| Pull-Down Peak Source Current [1][2]   | I <sub>PDPK</sub>     |                                                                  | _                     | 1.75 | _                     | Α    |  |  |  |

| Output Switching Time                  | t <sub>rGX</sub>      | 2 V to 10 V, C <sub>LOAD</sub> = 10 nF, V <sub>REG</sub> = 13 V  | _                     | 137  | _                     | ns   |  |  |  |

| Output Switching Time                  | t <sub>fGX</sub>      | 10 V to 2 V, C <sub>LOAD</sub> = 10 nF, V <sub>REG</sub> = 13 V  | _                     | 62   | _                     | ns   |  |  |  |

| Turn-Off Propagation Delay             | t <sub>P(OFF)</sub>   | Input change to unloaded gate-output change                      | _                     | 50   | -                     | ns   |  |  |  |

| Turn-On Propagation Delay              | t <sub>P(On)</sub>    | Input change to unloaded gate-output change                      | _                     | 50   | _                     | ns   |  |  |  |

| Propagation Delay Matching (On to Off) | t <sub>oo</sub>       |                                                                  | _                     | -    | 20                    | ns   |  |  |  |

| GHx Passive Pull-Down                  | R <sub>GHPD</sub>     | $V_{GHx} - V_{Sx} < 0.3 V$                                       | _                     | 950  | _                     | kΩ   |  |  |  |

| GLx Passive Pull-Down                  | R <sub>GLPD</sub>     | $V_{GLx} - V_{LSS} < 0.3 V$                                      | _                     | 950  | _                     | kΩ   |  |  |  |

|                                        |                       | BSEL1 = 100 ns                                                   | 40                    | 120  | 200                   | ns   |  |  |  |

| Dead Time                              |                       | BSEL1 = 500 ns                                                   | 325                   | 500  | 675                   | ns   |  |  |  |

| Deau IIIIle                            | t <sub>DEAD</sub>     | BSEL1 = 1000 ns                                                  | 675                   | 1000 | 1325                  | ns   |  |  |  |

|                                        |                       | BSEL1 = 1500 ns                                                  | 1050                  | 1500 | 1950                  | ns   |  |  |  |

# 85 V Three-Phase MOSFET Driver

## **ELECTRICAL CHARACTERISTICS:** Valid for $T_A = -40^{\circ}\text{C}$ to $125^{\circ}\text{C}$ V<sub>VBB</sub> = 5.5 V to 85 V (unless noted otherwise)

| Characteristics Symbol           |                         | Test Conditions                                           | Min. | Тур. | Max. | Unit |

|----------------------------------|-------------------------|-----------------------------------------------------------|------|------|------|------|

| PROTECTION                       |                         |                                                           |      |      |      |      |

| Thermal Shutdown Temperature [1] | T <sub>TSD</sub>        | T <sub>J</sub> increasing                                 | _    | 170  | _    | °C   |

| Thermal Shutdown Hysteresis [1]  | T <sub>TSD(HYS)</sub>   |                                                           | _    | 15   | _    | °C   |

| VREG Undervoltage                | V <sub>VREG(UV)</sub>   | V <sub>VREG</sub> rising                                  | 7.4  | 7.95 | 8.5  | V    |

| VREG Undervoltage Hysteresis     | V <sub>VREG(HYS)</sub>  |                                                           | -    | 770  | _    | mV   |

| Bootstrap Undervoltage           | V <sub>BOOT(UV)</sub>   | V <sub>BOOT</sub> rising, V <sub>C</sub> – V <sub>S</sub> | 6.2  | 7    | 7.8  | V    |

| Bootstrap Hysteresis             | V <sub>BOOT(HYS)</sub>  |                                                           | _    | 1    | _    | V    |

| VLR Undervoltage Threshold       | V <sub>VLRUV(3p3)</sub> | Voltage falling, V <sub>VLRSEL</sub> = GND                | 2.4  | 2.7  | 2.85 | V    |

| VER Officer voltage Threshold    | V <sub>VLRUV(5)</sub>   | Voltage falling, V <sub>VLRSEL</sub> = V <sub>VLR</sub>   | 3.87 | 4.1  | 4.33 | V    |

| VLR Undervoltage Hysteresis      | V <sub>VLR(HYS)</sub>   |                                                           | _    | 100  | _    | mV   |

| VDS Threshold Range              | V <sub>DSTH</sub>       | Programmable through BSEL1, BSEL2                         | 0.3  | _    | 1.2  | V    |

| VDS Fault Blank Time             | t <sub>BL</sub>         |                                                           | 1.3  | 2    | 3    | μs   |

| VDS Short-to-Ground              | V <sub>STGO</sub>       | V <sub>DSTH</sub> ≥ 900 mV                                | -200 | ±100 | 200  | mV   |

| Threshold Offset                 |                         | V <sub>DSTH</sub> < 900 mV                                | -150 | ±50  | 150  | mV   |

| VDS Short-to-Battery             | \/                      | V <sub>DSTH</sub> ≥ 900 mV                                | -200 | ±100 | 200  | mV   |

| Threshold Offset                 | V <sub>STBO</sub>       | V <sub>DSTH</sub> < 900 mV                                | -150 | ±50  | 150  | mV   |

| LOGIC I/O                        |                         |                                                           |      |      | ,    |      |

| Logic Input Voltage              | $V_{IN(H)}$             | AHI, ALO, BHI, BLO, CHI, CLO, ENABLE,                     | 2    | _    | _    | V    |

| Logic input voltage              | V <sub>IN(L)</sub>      | RESETn, BRAKEn                                            | _    | _    | 0.8  | V    |

| Input Hysteresis                 | V <sub>IN(HYS)</sub>    |                                                           | _    | 500  | _    | mV   |

| Logic Input Current [2]          | I <sub>IN(H)</sub>      | V <sub>IN</sub> = 5 V                                     | _    | 100  | _    | μΑ   |

| Logic input Current (-)          | I <sub>IN(L)</sub>      | V <sub>IN</sub> = 0 V                                     | -1   | 0    | 1    | μΑ   |

| Logic Input Pull-Down Resistor   | R <sub>LPD</sub>        | AHI, ALO, BHI, BLO, CHI, CLO, ENABLE, BRAKEn              | _    | 50   | _    | kΩ   |

| FAULTn Pull-Down Voltage         | V <sub>FAULT</sub>      | Fault present; I <sub>SINK</sub> = 1 mA                   | _    | -    | 0.3  | V    |

| Reset Pulse Width                | t <sub>RST</sub>        |                                                           | 0.2  | -    | 4.5  | μs   |

| Reset Shutdown Time              | t <sub>SLEEP</sub>      | RESETn high-to-low transition                             | 10   | -    | _    | μs   |

| Input Pin Glitch Reject [1]      | t <sub>GLITCH</sub>     | ENABLE, BRAKEn                                            | 200  | _    | 500  | ns   |

| Power-Up Time from Sleep         | t <sub>PU</sub>         | RESETn low-to-high, C <sub>VREG</sub> = 22 μF             | _    | _    | 3    | ms   |

# 85 V Three-Phase MOSFET Driver

**ELECTRICAL CHARACTERISTICS:** Valid for  $T_A = -40^{\circ}\text{C}$  to 125°C  $V_{VBB} = 5.5 \text{ V}$  to 85 V (unless noted otherwise)

| Characteristics                                  | Symbol                  | Test Conditions                                                                        | Min. | Тур.  | Max. | Unit  |

|--------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------|------|-------|------|-------|

| CURRENT-SENSE AMPLIFIER                          |                         |                                                                                        | ·    |       |      |       |

| Input Offset Voltage [1]                         | V <sub>IOS</sub>        |                                                                                        | _    | ±10   | _    | mV    |

| Input Offset Voltage Drift [1]                   | dV <sub>IOS</sub>       |                                                                                        | -    | ±4    | _    | μV/°C |

| Input Bias Current [2]                           | I <sub>BIAS</sub>       | V <sub>ID</sub> = 0, V <sub>CM</sub> in range                                          | -50  | -     | 5    | μA    |

| Input Offset Current [2]                         | I <sub>OS</sub>         | V <sub>ID</sub> = 0, V <sub>CM</sub> in range                                          | -1.5 | -     | 1.5  | μA    |

| Input Common-Mode Range (DC)                     | V <sub>CM</sub>         | $V_{ID} = 0$                                                                           | -1.3 | _     | 2    | V     |

| Gain                                             | A <sub>V</sub>          | Programmable through BSEL1, BSEL2                                                      | 10   | _     | 40   | V/V   |

| Gain Error                                       | E <sub>A</sub>          | V <sub>CM</sub> in range                                                               | -1.6 | _     | 1.6  | %     |

| Pedestal Voltage                                 | V <sub>oos</sub>        | Programmable through BSEL1, BSEL2                                                      | 0.2  | _     | 1.6  | V     |

| Pedestal Voltage Error                           | E <sub>VO</sub>         | V <sub>CM</sub> in range, V <sub>OOS</sub> > 0                                         | -10  | ±2    | 10   | %     |

| Small Signal –3 dB Bandwidth<br>Gain = 20 [1]    | BW                      | V <sub>IN</sub> = 10 mV <sub>PP</sub>                                                  | 2    | _     | _    | MHz   |

| Output Settling Time (to within 40 mV) [1]       | t <sub>SET</sub>        | $V_{CSO}$ = 1 $V_{PP}$ square wave, gain = 20,<br>$C_{OUT}$ = 50 pF                    | 0.2  | _     | 1    | μs    |

| Output Dynamic Range                             | V <sub>CSOUT</sub>      | –100 μA < I <sub>CSO</sub> < 100 μA                                                    | 0.45 | _     | 4.8  | V     |

| Output Voltage Clamp [1]                         | V <sub>csc</sub>        | I <sub>CSO</sub> = -2 mA                                                               | 3.7  | 4.2   | 5.1  | V     |

| Output Current Sink [2]                          | I <sub>CS(SINK)</sub>   | V <sub>ID</sub> = 0 V, V <sub>CSO</sub> = 0.8 V, gain = 20                             | 230  | -     | 490  | μA    |

| Output Current Sink (Boosted) [1][2]             | I <sub>CS(SINKB)</sub>  | $V_{OOS} = 0.8 \text{ V}, V_{ID} = -50 \text{ mV}, V_{CSO} = 1.5 \text{ V},$ gain = 20 | 1.8  | _     | 4.4  | mA    |

| Output Current Source [2]                        | I <sub>CS(SOURCE)</sub> | $V_{OOS}$ = 0.8 V, $V_{ID}$ = 200 mV, gain = 20, $V_{CSO}$ = 1.5 V                     | -4.5 | -     | -1.7 | mA    |

| VPD Cumby Dinala Daigation Datia [1]             | PSRR <sub>AC</sub>      | V <sub>ID</sub> = 0 V, 100 kHz, gain = 20                                              | _    | 65    | _    | dB    |

| VBB Supply-Ripple Rejection Ratio [1]            | PSRR <sub>DC</sub>      | V <sub>CSP</sub> = V <sub>CSM</sub> = 0 V, DC, gain = 20                               | 77   | _     | _    | dB    |

| DC Common-Mode Rejection Ratio [1]               | CMRR <sub>DC</sub>      | V <sub>CM</sub> step from 0 V to 200 mV, gain = 20                                     | 52   | 100   | _    | dB    |

|                                                  |                         | V <sub>CM</sub> = 200 mV <sub>PP</sub> , 100 kHz, gain = 20                            | -    | 62    | _    | dB    |

| AC Common-Mode Rejection Ratio [1]               | CMRR <sub>AC</sub>      | V <sub>CM</sub> = 200 mV <sub>PP</sub> , 1 MHz, gain = 20                              | -    | 43    | _    | dB    |

|                                                  | OWNER                   | V <sub>CM</sub> = 200 mV <sub>PP</sub> , 10 MHz, gain = 20                             | _    | 25    | _    | dB    |

| Common-Mode Recovery Time (to within 100 mV) [1] | t <sub>CM(REC)</sub>    | $V_{CM}$ step from –1.5 V to 1 V, gain = 20, $C_{OUT}$ = 50 pF                         | _    | < 2.1 | _    | μs    |

| Output Slew Rate 10% to 90% [1]                  | SR                      | V <sub>ID</sub> step from 0 V to 175 mV, gain = 20,<br>C <sub>OUT</sub> = 50 pF        | 1.8  | _     | 7.5  | V/µs  |

| Input Overload Recovery (to within 40 mV) [1]    | t <sub>ID(REC)</sub>    | $V_{ID}$ step from 250 mV to 0 V, gain = 20, $C_{OUT}$ = 50 pF                         | 0.4  | _     | 2.1  | μs    |

<sup>[1]</sup> Not production tested; assured by design and characterization.

<sup>[2]</sup> For input and output current specifications, negative current is defined as coming out of (sourcing from) the specified device terminal.

#### **FUNCTIONAL DESCRIPTION**

#### **Basic Operation**

The A89121 provides six high-current gate drives capable of driving a wide range of N-channel power MOSFETs. The gate drives are configured as three half bridges, each with a high-side drive and a low-side drive. Direct control pins enable independent operation of the three half bridges in BLDC motors or permanent-magnet synchronous motors (PMSMs). Independent control over each MOSFET allows each driver to be driven with an independent PWM signal for full sinusoidal excitation.

The VBB input terminal powers an internal charge pump that generates a regulated supply ( $V_{VREG}$ ) to provide all the current necessary to drive the low-side gate drive outputs directly plus the high-side drive via the bootstrap capacitors. This architecture ensures that all external MOSFETs are fully enhanced at battery voltages down to 5.5 V.

The A89121 is designed for use in battery-operated equipment where low-current operation is critical. An internal 3.3 V or 5 V LDO regulator provides the supply for an external microcontroller and/or external circuitry. A low-power sleep and standby mode allows the A89121, the power bridge, and the load to remain connected to a battery supply without the need for an additional supply switch.

The A89121 includes also a programmable amplifier designed for low-side current sensing in the presence of high current and voltage transients.

## **VLR Regulator**

An integrated regulator controller is provided for external logic level circuits such as a microcontroller or an interface circuit. The regulator includes current limit, undervoltage, and short protection.

An overcurrent circuit limits the output of the regulator in the event of an excessively high load demand (load current >  $I_{\rm OCL}$ ). If the output voltage falls below the regulator undervoltage threshold ( $V_{\rm VLRUV}$ ), a fault state is flagged on the FAULTn output to provide an external warning, and the gate drive outputs are disabled.

### Sleep Mode

Input terminal RESETn controls the low-power mode of operation of the A89121.

Low-power sleep mode is activated when RESETn is held low for longer than t<sub>SLEEP</sub>. Sleep mode disables all the internal circuitry, excluding the VLR regulator.

In sleep mode, the ground current consumption from VBB is less than  $I_{SLEEP}$  (typically 8.5  $\mu$ A) when the external load is less than 100  $\mu$ A.

#### **Gate Drivers**

The A89121 is designed to drive external, low on-resistance, power N-channel MOSFETs. It supplies the large transient currents necessary to quickly charge and discharge the external MOSFET gate capacitance in order to reduce dissipation in the external MOSFET during switching. The charge current for the low-side drives and the main recharge current for the bootstrap capacitors are provided by the capacitor on the VREG terminal. The charge current for the high-side drives is provided by the bootstrap capacitors connected between the Cx and Sx terminals, one for each phase.

### **Bootstrap Supply**

When the high-side drivers are active, the reference voltage (Sx) for the driver rises close to the bridge supply voltage. At that time, to ensure that the driver remains active, the supply to the driver must exceed the bridge supply voltage. This temporary high-side supply is provided by bootstrap capacitors, one for each high-side driver. These three bootstrap capacitors are connected between the bootstrap supply terminals, CA, CB, CC, and the corresponding high-side reference terminal, SA, SB, SC.

The bootstrap capacitors are independently charged to approximately  $V_{VREG}$  when the associated reference Sx terminal is low. When the output swings high, the voltage on the bootstrap supply terminal rises with the output to provide the boosted gate voltage needed for the high-side N-channel power MOSFETs.

It is necessary to charge the bootstrap capacitors by turning on the low-side drive (GLx) prior to attempting to turn on the complementary high-side (GHx). To protect the external MOS-FETs from insufficient gate drive, the bootstrap capacitor voltage is monitored. Each bootstrap undervoltage monitor circuit prevents the high side from turning on if the bootstrap capacitor is not changed.

### **VREG Charge-Pump Regulator**

The gate drivers are powered by an internal voltage regulator that generates a voltage,  $V_{VREG}$ , at the VREG terminal. It limits the supply voltage to the drivers and, therefore, the maximum gate voltage. At low supply voltage, the regulated supply is maintained by a charge-pump boost converter. A sufficiently large storage capacitor must be connected between this terminal and the GND terminal to provide the transient charging current.

The decoupling capacitance is based on the bootstrap capacitor, which is dependent on the MOSFET selection. For details about the correct sizing of the VREG and bootstrap capacitors, refer to the Application Information section.

The regulated supply is maintained by a charge-pump buck-boost converter with a switching frequency of 62.5 kHz. The pump capacitor,  $C_{CP}$ , should have a nominal value of 0.47  $\mu F$  and should be connected between the CP1 and CP2 terminals.

#### **Dead Time**

To prevent cross-conduction (shoot-through) in any phase of the power MOSFET bridge, it is necessary to have a dead-time delay between a high-side or low-side turn off and the next complementary turn-on event. The potential for cross-conduction occurs when any complementary high-side and low-side pair of MOSFETs are switched at the same time, for example, at the PWM switch point.

The dead time is generally set by the external controller driving the inputs; however, the A89121 has several options for dead time that can be selected via the configuration resistors connected to the BSEL1 and BSEL2 pins.

#### **Gate Drive Control**

Six logic-level digital inputs—AHI, ALO, BHI, BLO, CHI, and CLO—provide direct control for the gate drives, one for each drive. The xHI inputs correspond to the high-side drives, and the xLO inputs correspond to the low-side drives. Logic inputs have a typical hysteresis of 500 mV to improve noise performance. The operation of the inputs is shown Table 1. A pull-down resistor is connected to each input to ensure a safe state if the control becomes disconnected.

**Table 1: Control Logic**

| Inp | out | Out | put | Phase | Comment          |

|-----|-----|-----|-----|-------|------------------|

| xHI | xLO | GHx | GLx | Sx    |                  |

| 0   | 0   | L   | L   | Z     | Phase disabled   |

| 0   | 1   | L   | Н   | LO    | Low-side active  |

| 1   | 0   | Н   | L   | HI    | High-side active |

| 1   | 1   | L   | L   | Z     | Phase disabled   |

The ENABLE input is connected directly to the gate-drive-output command signal, bypassing the main synchronous logic block on the chip (including all phase-control logic). This input can be used to provide a fast output disable (emergency cut-off) or to provide nonsynchronous fast decay PWM.

The BRAKEn input overrides the direct-control inputs and enables all low-side drivers. If a high-side driver is already enabled, the respective low-side driver become enabled after a dead time. BRAKEn input overrides the ENABLE input except when in sleep mode.

#### Three-Wire Drive Option

The A89121 provides an option to drive the six external MOS-FETS using three lines from the microcontroller instead of six. This option is chosen via the configuration resistor selection. For the three-wire drive option, the high-side inputs are used and the low-side gates are driven in a complementary fashion, turning on after the selected dead time. The xLO inputs are ignored and can be left in the open circuit state.

Table 2: Control Logic—Three-Wire

| Input |     | Output |     | Phase | Comment          |

|-------|-----|--------|-----|-------|------------------|

| xHI   | xLO | GHx    | GLx | Sx    |                  |

| 0     | Х   | L      | Н   | LO    | Low-side active  |

| 1     | Х   | Н      | L   | HI    | High-side active |

#### **Diagnostic**

The A89121 includes many diagnostic features to provide indication of and/or protection against undervoltage, overvoltage, overtemperature, and power bridge faults (VDS monitor and bootstrap undervoltage).

When RESETn is high, the FAULTn pin can be used to communicate the failure condition. During typical operation, the open drain is pulled high externally, through a resistor. When a fault occurs, the open drain output is enabled and the FAULTn output is pulled low according to Table 3.

Table 3: Fault Logic

| Event     | Fault Pin | Outputs<br>Disabled | Latched |

|-----------|-----------|---------------------|---------|

| TSD       | Low       | Y                   | Y       |

| VREG      | Low       | Y                   | N       |

| Boot UVLO | Low       | Y(Note)             | N       |

| VLR UVLO  | Low       | Y                   | N       |

| VDS       | Low       | Y                   | Υ       |

NOTE: Upon detection of the boot UVLO condition, only the appropriate high side is disabled.

Latched faults that result in disabled outputs can be reset in two

## 85 V Three-Phase MOSFET Driver

ways. Putting the device into sleep mode (RESETn low) resets the latch. RESETn can also be used to clear any fault conditions without entering sleep mode by pulsing low for 1  $\mu$ s (within the range of the reset pulse width specification,  $t_{RST}$ ).

### **Overtemperature (TSD)**

If the die temperature exceeds T<sub>TSD</sub>, FAULTn is pulled low and the outputs are disabled. Thermal shutdown is a latched fault.

#### **Bootstrap UVLO Fault**

Before a high-side switch is allowed to turn on and when a high side is on, it must have sufficient charge on the bootstrap capacitor. If a high side is instructed to turn on and the voltage on the appropriate bootstrap capacitor is less than the bootstrap threshold, the A89121 triggers a fault (FAULTn goes low) and does not allow the high-side gate to turn on. After a high-side gate drive has been successfully turned on, the appropriate bootstrap capacitor voltage must continue to exceed the bootstrap undervoltage threshold,  $V_{\rm BOOT(UV)}$ . If the bootstrap capacitor voltage drops below  $V_{\rm BOOT(UV)}$ , the high-side driver in question is switched off and FAULT goes low. The driver remains off until the bootstrap capacitor is charged to  $(V_{\rm BOOT(UV)} + V_{\rm BOOT(HYS)})$  and the gate xHI input is active high.

If a bootstrap capacitor fault condition is detected, only the driver in question is disabled. All other gate drives continue to respond to control inputs on xHI and xLO.

### **VDS Overvoltage Fault**

Faults on any external MOSFETs are determined by monitoring the drain-to-source voltage of the MOSFET and comparing it to the drain-to-source overvoltage threshold. for the available threshold voltages, refer to Table 4.

If the measured voltage exceeds the configurable threshold value of the pin, the FAULTn output is set low and the gate drive outputs are disabled. A VDS fault is latched.

At every external MOSFET turn-on event, the output of all VDS comparators is ignored for the duration of the VDS fault blank time (t<sub>BL</sub>); this prevents the reporting of spurious faults in response to switching transients.

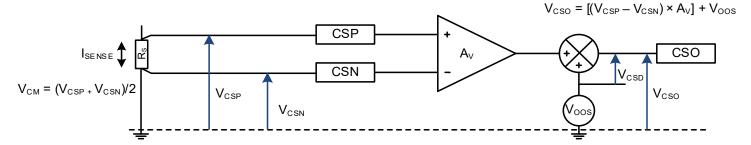

### **Current-Sense Amplifier**

A configurable-gain, differential, sense amplifier is provided to allow the use of low-value sense resistors or a current shunt as a low-side current-sensing element. The input common-mode range of the CSP and CSM inputs and programmable output offset allow below-ground current sensing—typically required for low-side current sense in PWM control of motors or other inductive loads—during switching transients. The output of the sense amplifier is available at the CSO output and can be used in peak-current or average-current control systems. The output can drive up to 4.8 V to permit maximized dynamic range with greater input-voltage analog-to-digital converters (ADCs).

The gain and offset of the sense amplifier are defined by the configuration of the pin-detect comparator, and shown in Table 4.

#### Pin-Detect Comparator

The A89121 is equipped with a pin-detect comparator on the BSEL1 and BSEL2 pins. This function allows the user to program 5 bits of digital features with three external E96 1% resistors. The pin-detect comparator requires a 51.1 k $\Omega$  resistor between BSEL1 and BSEL2, and the bit selections are determined by resistor values placed from BSEL1 to AGND and BSEL2 to AGND. The resistor values used for programming range from 511  $\Omega$  to 750 k $\Omega$ . The resistor from BSEL2 to GND programs the current-sense offset and gain. The resistor from BSEL1 to GND programs the VDS levels for short-to-ground and short-to-battery protection, dead time, and gate-drive logic mode.

The pin-detect circuitry is designed to be robust to ground differentials of  $\pm 20$  mV, pin leakages of  $\pm 500$  nA, and capacitances of up to 50 pF. These criteria allow for robust performance in all PCB layouts. For the configurable variables, refer to Table 4.

## **Current Amplifier**

Table 4: BSEL1 and BSEL2

| BSEL1  |                   |   |                    |     |               |  |  |

|--------|-------------------|---|--------------------|-----|---------------|--|--|

|        | 4                 | 3 | 2                  | 1   | 0             |  |  |

| RBSEL1 | Dead Time<br>(ns) |   | VDS Threshold (mv) |     | Inputs<br>(#) |  |  |

| 511    | 100               |   | 300                |     | 6             |  |  |

| 1620   |                   |   |                    |     | 3             |  |  |

| 3480   |                   |   | 600                |     | 6             |  |  |

| 5360   |                   |   |                    |     | 3             |  |  |

| 7150   |                   |   | 900                |     | 6             |  |  |

| 9530   |                   |   |                    |     | 3             |  |  |

| 11500  |                   |   | 1200               |     | 6             |  |  |

| 14000  |                   |   |                    |     | 3             |  |  |

| 16900  | 500               |   | 300                |     | 6             |  |  |

| 19600  |                   |   | 30                 | 300 |               |  |  |

| 23700  |                   |   | 600                |     | 6             |  |  |

| 26100  |                   |   |                    |     | 3             |  |  |

| 30100  |                   |   | 000                | 6   |               |  |  |

| 34800  |                   |   | 900                |     | 3             |  |  |

| 40200  |                   |   | 4000               | 6   |               |  |  |

| 44200  |                   |   | 1200               |     | 3             |  |  |

| 51100  | 1000              |   | 300                | 6   |               |  |  |

| 59000  |                   |   | 300                |     | 3             |  |  |

| 64900  |                   |   | 600                | 6   |               |  |  |

| 75000  |                   |   | 000                |     | 3             |  |  |

| 86600  |                   |   | 900                |     | 6             |  |  |

| 95300  |                   |   |                    |     | 3             |  |  |

| 110000 |                   |   | 1200               | 6   |               |  |  |

| 133000 |                   |   | 1200               |     | 3             |  |  |

| 154000 | 1500              |   | 300                | 6   |               |  |  |

| 187000 |                   |   | 30                 | 300 | 3             |  |  |

| 226000 |                   |   | 600                | 6   |               |  |  |

| 274000 |                   |   | 000                |     | 3             |  |  |

| 365000 |                   |   | 900                |     | 6             |  |  |

| 487000 |                   |   |                    |     | 3             |  |  |

| 750000 |                   |   | 1200               |     | 6             |  |  |

| Float  |                   |   |                    |     | 3             |  |  |

| BSEL2  |               |   |                  |      |   |  |

|--------|---------------|---|------------------|------|---|--|

|        | 4             | 3 | 2                | 1    | 0 |  |

| RBSEL2 | Gain<br>(V/V) |   | Pedestal<br>(mv) |      |   |  |

| 511    |               |   | 200              |      |   |  |

| 1620   |               |   | 400              |      |   |  |

| 3480   | 20            |   | 600              |      |   |  |

| 5360   |               |   | 800              |      |   |  |

| 7150   |               |   | 1000             |      |   |  |

| 9530   |               |   | 1200             |      |   |  |

| 11500  |               |   | 1400             |      |   |  |

| 14000  |               |   | 1600             |      |   |  |

| 16900  |               |   | 200              |      |   |  |

| 19600  |               |   | 400              |      |   |  |

| 23700  |               |   | 600              |      |   |  |

| 26100  |               |   | 800              |      |   |  |

| 30100  |               |   | 1000             |      |   |  |

| 34800  |               |   | 1200             |      |   |  |

| 40200  |               |   | 1400             |      |   |  |

| 44200  |               |   | 1600             |      |   |  |

| 51100  | 30            |   | 200              |      |   |  |

| 59000  |               |   | 400              |      |   |  |

| 64900  |               |   |                  | 600  |   |  |

| 75000  |               |   |                  | 800  |   |  |

| 86600  |               |   | 1000             |      |   |  |

| 95300  |               |   |                  | 1200 |   |  |

| 110000 |               |   | 1400             |      |   |  |

| 133000 |               |   | 1600             |      |   |  |

| 154000 |               |   | 200              |      |   |  |

| 187000 | 40            |   | 400              |      |   |  |

| 226000 |               |   | 600              |      |   |  |

| 274000 |               |   |                  | 800  |   |  |

| 365000 |               |   | 1000             |      |   |  |

| 487000 |               |   | 1200             |      |   |  |

| 750000 |               |   | 1400             |      |   |  |

| Float  |               |   | 1600             |      |   |  |

#### **APPLICATION INFORMATION**

#### **Bootstrap Capacitor Selection**

To properly size the capacitor,  $C_{\mbox{\footnotesize BOOT}}$ , the total gate charge must be known:

- If the bootstrap capacitor is too large, the charge time will be long, resulting in limits to the maximum duty cycle.

- If the bootstrap capacitor is too small, the voltage ripple will be large when charging the gate.

Size the  $C_{BOOT}$  capacitor such that the charge,  $Q_{BOOT}$ , is 20 times larger than the required charge for the gate of the MOSFET,  $Q_{GATE}$ , using:

$$C_{BOOT} = [Q_{GATE} \times 20]/[V_{BOOT}],$$

where V<sub>BOOT</sub> is the voltage across the bootstrap capacitor.

The voltage drop,  $\Delta V$ , across the bootstrap capacitor as the MOS-FET gate is being charged can be approximated by:

$$\Delta V = [Q_{GATE}]/[C_{BOOT}].$$

For the bootstrap capacitor, a ceramic type rated at 16 V or larger should be used.

### **VREG Capacitor Selection**

VREG is responsible for providing all the gate charge for the low-side MOSFETs and for providing all the charge current for the three bootstrap capacitors. For this purpose, the VREG capacitor should be 20 times the value of  $C_{\rm BOOT}$ :

$$C_{VREG} = 20 \times C_{BOOT}$$

#### PACKAGE OUTLINE DRAWING

All dimensions nominal, not for tooling use (reference Allegro DWG-0000378, Rev. 3)

Dimensions in millimeters

Exact case and lead configuration at supplier discretion within limits shown

A Terminal #1 mark area

Exposed thermal pad (reference only, terminal #1 identifier appearance at supplier discretion)

Reference land pattern layout (reference IPC7351

QFN50P600X600X100-37V1M); All pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to meet application process requirements and PCB layout tolerances; when mounting on a multilayer PCB, thermal vias at the exposed thermal pad land can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

Coplanarity includes exposed thermal pad and terminals

Figure 1: 36-Lead QFN with Exposed Pad (Suffix EV)

# 85 V Three-Phase MOSFET Driver

#### **Revision History**

| Number | Date              | Description                                               |  |

|--------|-------------------|-----------------------------------------------------------|--|

| _      | March 11, 2024    | Initial release                                           |  |

| 1      | November 26, 2024 | Updated Electrical Characteristics table (page 6, page 8) |  |

Copyright 2024, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com