## 50 V Ultra-Low Noise FOC Motor Controller

## FEATURES AND BENEFITS

- Code-free sensorless field-oriented control (FOC), for driving motors at up to 400 Hz

- Constant speed, constant torque, constant power, or openloop operating mode

- I<sup>2</sup>C interface for motor control and status readback

- Universal 32-point speed/power/torque/duty curve

- Ultra-quiet operation

- Proprietary non-reverse fast startup

- Soft-On Soft-Off (SOSO) for quiet operation

- Analog / PWM / Clock mode speed control

- Configurable current limit

- Windmill startup operation (fwd and rev)

- Lock detection

- Short-circuit protection (OCP)

- Brake and direction inputs

- · Adjustable gate drive

## **APPLICATIONS**

- Ceiling fans, pedestal fans

- Bathroom exhaust fans

- Air purifier, humidifier, dehumidifier fans

- Home appliance fans and pumps

## PACKAGE

Not to scale

DESCRIPTION

The A89306 is a 3-phase sensorless brushless DC (BLDC) motor driver (gate driver) which can operate from 5.5 to 50 V.

A field-oriented control (FOC) algorithm is fully integrated to achieve the best efficiency and acoustic noise performance. Constant torque and constant power modes are provided, as well as constant speed and open-loop operating modes. The device also optimizes the motor startup performance from a stationary condition, a windmill condition, and even from a reverse windmill condition.

Motor output, speed, torque, or power is controlled through analog, PWM, or using I<sup>2</sup>C. A universal speed/power/torque/ duty curve is stored in EEPROM and allows for flexible control schemes. An optional clock mode is available for closed-loop speed control, with a programmable clock frequency to rpm ratio.

A simple I<sup>2</sup>C interface is provided for setting motor-rated voltage, rated current, rated speed, resistance, and startup profiles. The I<sup>2</sup>C interface can also be used for on/off control, output control and for speed and status readback.

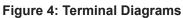

The A89306 is available in a surface mount 28-contact 5 mm  $\times$  5 mm QFN (suffix ET) package. The package has an exposed pad for enhanced thermal dissipation, and lead (Pb) free, with 100% matte-tin leadframe plating.

28-contact QFN with exposed thermal pad 5 mm  $\times$  5 mm  $\times$  0.90 mm

(ET package)

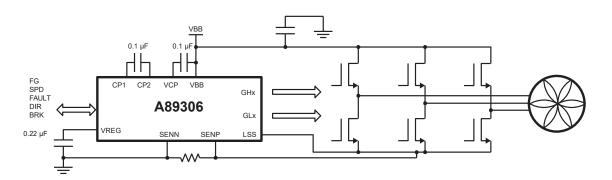

**Figure 1: Typical Application**

### SPECIFICATIONS

#### **SELECTION GUIDE**

| Part Number | Packaging                               | Packing                      |

|-------------|-----------------------------------------|------------------------------|

| A89306GETSR | 28-contact QFN with exposed thermal pad | 6000 pieces per 13-inch reel |

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic              | Symbol                                | Notes                              | Rating                           | Unit   |

|-----------------------------|---------------------------------------|------------------------------------|----------------------------------|--------|

| Supply Voltage              | V <sub>BB</sub>                       |                                    | 50                               | V      |

| Logic Input Voltage Range   | V <sub>IN</sub>                       | SPD, BRAKE, DIR                    | -0.3 to 6                        | V      |

| Logic Output                | Vo                                    | FG, FAULT (I < 5 mA)               | -0.3 to 6                        | V      |

| LSS                         |                                       | DC                                 | ±500                             | mV     |

| 155                         | V <sub>LSS</sub>                      | t <sub>W</sub> < 500 ns            | ±4                               | V      |

| VREG                        | V <sub>REG</sub>                      |                                    | 0 to 4                           | V      |

| OFNIN OFNID                 |                                       | DC                                 | ±500                             | mV     |

| SENN, SENP                  | V <sub>SENN</sub> , V <sub>SENP</sub> | t <sub>W</sub> < 500 ns            | ±4                               | V      |

| Output Valtage              | V <sub>OUT</sub>                      | SA, SB, SC                         | -2 to V <sub>BB</sub> + 2        | V      |

| Output Voltage              |                                       | SA, SB, SC, t <sub>W</sub> < 50 ns | -4 to V <sub>BB</sub> + 4        | V      |

| GHx                         | V <sub>GHx</sub>                      |                                    | $V_{Sx} - 0.3$ to $V_{CP} + 0.3$ | V      |

| GLx                         | V <sub>GLx</sub>                      |                                    | V <sub>LSS</sub> – 0.3 to 8.5    | V      |

| VCP                         | V <sub>CP</sub>                       |                                    | $V_{BB} - 0.3$ to $V_{BB}$ + 8   | V      |

| CP1                         | V <sub>CP1</sub>                      |                                    | -0.3 to V <sub>BB</sub> + 0.3    | V      |

| CP2                         | V <sub>CP2</sub>                      |                                    | $V_{BB} - 0.3$ to $V_{CP} + 0.3$ | V      |

| Maximum EEPROM write cycles | EEPROM <sub>W(MAX)</sub>              |                                    | 1000                             | cycles |

| Junction Temperature        | TJ                                    |                                    | 150                              | °C     |

| Storage Temperature Range   | T <sub>stg</sub>                      |                                    | -55 to 150                       | °C     |

| Operating Temperature Range | T <sub>A</sub>                        | Range G                            | -40 to 105                       | °C     |

#### THERMAL CHARACTERISTICS

| Characteristic             | Symbol          | Test Conditions*                                                      | Value | Unit |

|----------------------------|-----------------|-----------------------------------------------------------------------|-------|------|

| Package Thermal Resistance | $R_{\theta JA}$ | 28-contact QFN (package ET), on 2-sided PCB 1-in. <sup>2</sup> copper | 40    | °C/W |

\*Additional thermal information available on the Allegro website.

## 50 V Ultra-Low Noise FOC Motor Controller

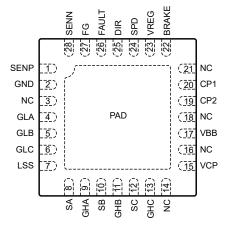

### **PINOUT DIAGRAM AND TERMINAL LIST TABLE**

#### **ET Package Pinouts**

#### **Terminal List Table**

| Number               | Name  | Function                                     |

|----------------------|-------|----------------------------------------------|

| 19                   | CP2   | Charge pump                                  |

| 20                   | CP1   | Charge pump                                  |

| 22                   | BRAKE | Logic input                                  |

| 23                   | VREG  | 2.8 V regulator voltage                      |

| 24                   | SPD   | PWM or clock mode speed control              |

| 25                   | DIR   | Direction control                            |

| 26                   | FAULT | Fault indicator output                       |

| 27                   | FG    | Motor speed output                           |

| 28                   | SENN  | Current sense negative terminal              |

| 1                    | SENP  | Current sense positive terminal              |

| 2                    | GND   | Ground                                       |

| 4                    | GLA   | Low-side gate drive output                   |

| 5                    | GLB   | Low-side gate drive output                   |

| 6                    | GLC   | Low-side gate drive output                   |

| 7                    | LSS   | Low-side source                              |

| 8                    | SA    | Motor output                                 |

| 9                    | GHA   | High-side gate drive output                  |

| 10                   | SB    | Motor output                                 |

| 11                   | GHB   | High-side gate drive output                  |

| 12                   | SC    | Motor output                                 |

| 13                   | GHC   | High-side gate drive output                  |

| 3, 14, 16,<br>18, 21 | NC    | No connect                                   |

| 15                   | VCP   | Charge pump                                  |

| 17                   | VBB   | Power supply                                 |

| PAD                  | PAD   | Exposed pad for enhanced thermal dissipation |

## 50 V Ultra-Low Noise FOC Motor Controller

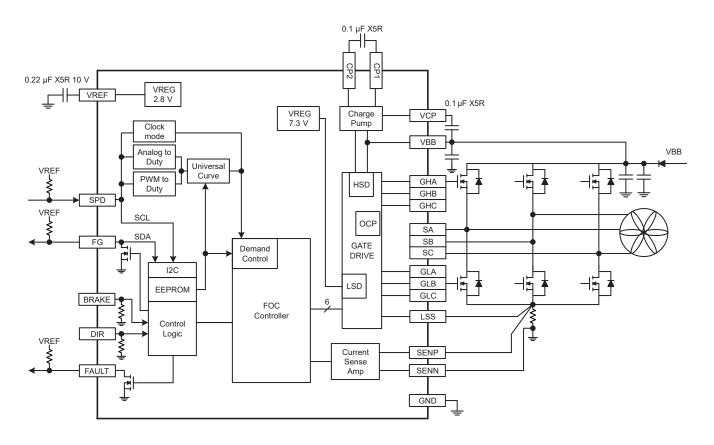

## FUNCTIONAL BLOCK DIAGRAM

## 50 V Ultra-Low Noise FOC Motor Controller

| ELECTRICAL CHARACTERISTICS: Valid over operating a | bient temperature range and voltage range, unless noted otherwise |

|----------------------------------------------------|-------------------------------------------------------------------|

|----------------------------------------------------|-------------------------------------------------------------------|

| Characteristics                         | Symbol                    | Test Conditions                 | Min. | Тур. | Max. | Unit |

|-----------------------------------------|---------------------------|---------------------------------|------|------|------|------|

| GENERAL                                 |                           | L.                              |      |      |      |      |

| 0 I.V.H. 5                              |                           | Driving                         | 5.5  | _    | 48   | V    |

| Supply Voltage Range                    | V <sub>BB</sub>           | Operating                       | 5.5  | _    | 50   | V    |

| V/DD Original Comment                   |                           | I <sub>VREG</sub> = 0 mA        | _    | 8    | 12   | mA   |

| VBB Supply Current                      | I <sub>BB</sub>           | Standby mode                    | _    | 10   | 20   | μA   |

| Reference Voltage                       | V <sub>REG</sub>          | I <sub>OUT</sub> = 10 mA        | 2.70 | 2.86 | 2.95 | V    |

| GATE DRIVE                              | 1                         |                                 |      |      |      |      |

| High Olds Octs Drive Octsut             |                           | V <sub>BB</sub> = 8 V           | 6.5  | 6.8  | _    | V    |

| High-Side Gate Drive Output             | V <sub>GH</sub>           | V <sub>BB</sub> = 24 V          | 6.5  | 6.8  | _    | V    |

|                                         |                           | V <sub>BB</sub> = 8 V           | 6.5  | 7.3  | -    | V    |

| Low-Side Gate Drive Output              | V <sub>GL</sub>           | V <sub>BB</sub> = 24 V          | 6.5  | 7.3  | -    | V    |

|                                         |                           | V <sub>BB</sub> = 8 V; level 0  | _    | 15   | -    | mA   |

| Gate Drive Source Current               | I <sub>SO</sub>           | V <sub>BB</sub> = 8 V; level 1  | _    | 30   | _    | mA   |

|                                         |                           | V <sub>BB</sub> = 8 V; level 2  | -    | 55   | _    | mA   |

|                                         |                           | V <sub>BB</sub> = 8 V; level 0  | -    | 30   | _    | mA   |

| Gate Drive Sink Current                 | I <sub>SI</sub>           | V <sub>BB</sub> = 8 V; level 1  | -    | 60   | _    | mA   |

|                                         |                           | V <sub>BB</sub> = 8 V; level 2  | _    | 105  | _    | mA   |

| VDS SENSING FOR OCP                     | ·                         |                                 |      |      |      |      |

| V/D0.0 / T/ / //                        |                           | Level 0                         | _    | 1    | _    | V    |

| VDS Comparator Threshold                | V <sub>DS_THR</sub>       | Level 1                         | _    | 2    | -    | V    |

| MOTOR DRIVE                             |                           |                                 | ·    | ·    |      |      |

| PWM Duty On Threshold PWM <sub>ON</sub> |                           | Relative to target              | -0.5 | _    | +0.5 | %    |

| PWM Duty Off Threshold                  | PWM <sub>OFF</sub>        | Relative to target              | -0.5 | -    | +0.5 | %    |

|                                         | 6                         | PWM input frequency setting = 0 | 2.5  | -    | 100  | kHz  |

| PWM Input Frequency Range               | <sup>†</sup> PWM(MIN)     | PWM input frequency setting = 1 | 80   | -    | 3200 | Hz   |

| Clock Input Frequency Range             | f <sub>CLOCK</sub>        | CLOCK mode                      | 1    | -    | 2000 | Hz   |

| SPD Standby Threshold<br>(Analog Enter) | V <sub>SPD(TH_ENT)</sub>  |                                 | 50   | 100  | 150  | mV   |

| SPD Standby Threshold<br>(Analog Exit)  | V <sub>SPD(TH_EXIT)</sub> |                                 | 0.4  | 0.75 | 1.0  | V    |

| SPD On Threshold                        | V <sub>SPD(ON)</sub>      | ON/OFF setting = 9.7%           | 210  | 250  | 290  | mV   |

| SPD Maximum                             | V <sub>SPD(MAX)</sub>     |                                 | _    | 2.5  | _    | V    |

| SPD ADC Resolution                      | V <sub>SPDADC(RES)</sub>  |                                 | - 1  | 9.78 | _    | mV   |

| SPD ADC Accuracy                        | V <sub>SPDADC(ACC)</sub>  | V <sub>SPD</sub> = 0.2 to 2.5 V | -40  | -    | 40   | mV   |

| Closed Leen Speed Assures               |                           | PWM mode or Analog mode         | -5   | -    | 5    | %    |

| Closed-Loop Speed Accuracy              | f <sub>SPD(ACC)</sub>     | Clock mode                      | -0.1 | _    | 0.1  | rpm  |

| Dead Time                               | t <sub>DT</sub>           | Code = 9                        | _    | 400  | _    | ns   |

| Motor PWM Frequency                     | f <sub>PWM</sub>          | T <sub>A</sub> = 25°C           | 23.3 | 24.4 | 25.3 | kHz  |

Continued on next page ...

## 50 V Ultra-Low Noise FOC Motor Controller

#### ELECTRICAL CHARACTERISTICS (continued): Valid over operating ambient temperature range and voltage range,

unless noted otherwise

| Characteristics                 | Symbol                | Test Conditions                       | Min. | Тур. | Max. | Unit |

|---------------------------------|-----------------------|---------------------------------------|------|------|------|------|

| PROTECTION                      |                       |                                       |      |      |      |      |

| VBB Undervoltage Threshold      | V <sub>BB(UVLO)</sub> | V <sub>BB</sub> rising                | -    | 4.75 | 4.95 | V    |

| VBB Undervoltage Hysteresis     | V <sub>BB(HYS)</sub>  |                                       | 200  | 300  | 450  | mV   |

| Thermal Shutdown Temperature    | T <sub>JTSD</sub>     | Temperature increasing                | -    | 165  | -    | °C   |

| Thermal Shutdown Hysteresis     | ΔT <sub>J</sub>       | Recovery = $T_{JTSD} - \Delta T_J$    | -    | 20   | -    | °C   |

| LOGIC, IO, I <sup>2</sup> C     |                       |                                       | ·    |      |      |      |

|                                 |                       | SPD, FG; V <sub>IN</sub> = 0 to 5.5 V | -5   | 1    | 5    | μA   |

| Logic Input Current             | I <sub>IN</sub>       | BRK, DIR; V <sub>IN</sub> = 5 V       | _    | 50   | -    | μA   |

| Logic Input Low Level           | V <sub>IL</sub>       |                                       | 0    | _    | 0.8  | V    |

| Logic Input High Level          | V <sub>IH</sub>       |                                       | 2.0  | _    | 5.5  | V    |

| Logic Input Hysteresis          | V <sub>HYS</sub>      |                                       | 150  | 300  | 600  | mV   |

| Logic Output Leakage            | ILEAK                 | FG, FAULT, V = 5.5 V, switch off      | _    | _    | 1    | μA   |

| Logic Output Saturation Voltage | V <sub>SAT</sub>      | FG, FAULT, I = 5 mA                   | -    | _    | 0.3  | V    |

<sup>[1]</sup> Specified limits are tested at 25°C and 125°C and statistically assured over operating temperature range by design and characterization.

## FUNCTIONAL DESCRIPTION

The A89306 is a three-phase BLDC controller with integrated gate driver. It operates from 5.5 to 50 V, and targets ceiling, pedestal, bathroom exhaust, air purifier, humidifier, and dehumidifier fans, and home appliance fans and pumps.

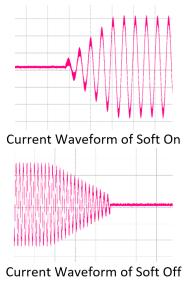

The integrated FOC control algorithm achieves the best efficiency and dynamic response and minimizes acoustic noise. Allegro's proprietary non-reverse startup algorithm improves the startup performance. The motor will start up towards the target direction after power up without reverse shaking or vibration. Three-phase modulation and deadtime compensation are used to provide the lowest acoustic noise, even at very low speeds. The optional Soft-On and Soft-Off features gradually increase the current to the motor at "on" command during a windmill condition (when the motor is already rotating in the correct direction), and gradually reduces the current from the motor at the "off" command, further reducing the acoustic noise and operating the motor smoothly.

## SPD - Speed, Torque (current), Power Control

Input demand is provided via the SPD terminal. Three SPD control modes are selectable through the EEPROM. The A89306 also features closed-loop speed, closed-loop torque (constant phase current), and closed-loop power functions, which can be enabled or disabled via the EEPROM.

The SPD terminal is also used as SCL for the  $I^2C$  interface. See the  $I^2C$  section for details.

**PWM Mode:** In this mode, the output to the motor is controlled by the PWM duty cycle on the SPD terminal, and higher duty cycle represents higher motor output (unless using the input transformer curve, described later). If open-loop mode is selected, the output voltage amplitude will be proportional to the PWM duty cycle. If closed-loop speed is selected, the motor speed is proportional to the PWM duty cycle, and 100% duty represents the speed set by the CONTROL LOOP RANGE setting programmed in the EEPROM. Likewise, if closed-loop torque/current is selected, the motor phase current is proportional to the PWM duty cycle, and 100% duty represents the current level set by the CONTROL LOOP RANGE setting programmed in the EEPROM. And if closed-loop power is selected, the power delivered to the motor is proportional to the PWM duty cycle, and 100% duty represents the power level set by the CONTROL LOOP RANGE setting programmed in the EEPROM.

CLOSED\_LOOP\_SPEED / CLOSED\_LOOP\_CURRENT / CLOSED\_LOOP\_POWER = CONTROL\_LOOP\_RANGE × DUTY INPUT

The SPD PWM frequency range is 80 Hz to 100 kHz. If the input frequency is higher than 2.8 kHz, PWMIN\_RANGE should be set to 0, and if it is lower than 2.8 kHz, PWMIN\_RANGE should be set to 1.

**Analog Mode:** In this mode, the motor output is controlled by the analog voltage on the SPD terminal, with higher voltage representing higher output demand. If open-loop mode is selected, the output voltage amplitude will be proportional to the analog voltage input. If closed-loop speed is enabled, the motor output is as follows:

CLOSED\_LOOP\_SPEED / CLOSED\_LOOP\_CURRENT / CLOSED\_LOOP\_POWER = CONTROL\_LOOP\_RANGE × ANALOG\_INPUT / SPD<sub>MAX</sub>

**CLOCK Mode:** When using clock mode, closed-loop speed is always enabled. The default input for clock mode is the SPD terminal, but there are options to use either the DIR or BRAKE terminals instead. Either of these options allows use of the I<sup>2</sup>C interface and clock mode at the same time. Higher frequency on the clock input will drive a higher motor speed as follows:

CLOSED\_LOOP\_SPEED (rpm) = CLOCK\_INPUT × SPEED\_CTRL\_RATIO,

where the SPEED\_CTRL\_RATIO is programmed in the

EEPROM. For example, if the ratio is 4 and the clock input frequency is 60 Hz, the motor will operate at 240 rpm. Note the number of motor pole-pairs must be set properly in the programming application for the rated speed (rpm) displayed for the setting to be accurate. Note the number of pole-pairs is saved in the programming application's setting file but is not stored in the EEPROM. Thus, after reading the settings from a device's EEPROM in the application, verify the pole-pairs entry is correct.

If the clock frequency commands a speed that is higher than twice the rated speed, the A89306 treats it as a clock input error and stops the motor.

CLOCK mode can achieve the best closed-loop speed accuracy.

When using any of the closed-loop modes, if the input demand is higher than the maximum speed/current/power, the system can run at the applied supply voltage and load condition, the A89306 will just provide the maximum output voltage (as long as current limit is not triggered), or the maximum output current (if current limit is triggered).

The input demand can also be controlled using the I<sup>2</sup>C interface. Refer to register table for more details. While in Analog mode, PWM mode, or CLOCK mode, sending an I<sup>2</sup>C command may cause motor speed change, unexpected startup attempts, or operation failure. Changing from I<sup>2</sup>C mode to CLOCK (Analog, PWM) mode requires either power cycle or enter and then exit from standby mode.

**Motor Stop and Standby Mode:** If the speed demand is less than the programmed threshold, the motor will stop.

| GUI setting | On threshold | Off threshold |

|-------------|--------------|---------------|

| 5.8%        | 7.9%         | 5.8%          |

| 9.7%        | 11.8%        | 9.7%          |

| 12.8%       | 15.0%        | 12.8%         |

| 19.5%       | 21.6%        | 19.5%         |

For example, consider 9.7% is set as the threshold. If PWM duty is less than 9.7% (in PWM mode), or the analog voltage is less than 243 mV (in Analog mode), or the CLOCK input frequency is less than 9.7% of the RATED\_SPEED (in CLOCK mode), the IC will stop the motor and enter the "idle" mode.

In order to enter standby two conditions must be met: the motor must be stationary (this requirement can be removed by a setting in the EEPROM), and the SPD terminal remains logic low (in PWM and CLOCK mode) or the SPD analog voltage remains less than SPDTH\_ENT (in Analog mode) for longer than one second. In the case that CLOCK mode is used with a terminal other than SPD (i.e. DIR or BRAKE), the SPD terminal is still used to put the device in standby mode.

A rising edge on the SPD terminal will wake the IC in PWM and CLOCK mode, and in Analog mode, the voltage on the SPD terminal must be higher than SPDTH\_EXIT to wake up the IC.

Standby Mode will turn off all circuitry including the charge pump and VREG.

After powering on, the device will always be in the active mode before entering standby mode.

The standby mode can be disabled in the EEPROM.

**Direction Input:** The DIR terminal is a logic input to control motor direction. For logic high, the motor phases are ordered  $A \rightarrow B \rightarrow C$ . For logic low, the motor phases are ordered  $A \rightarrow C \rightarrow B$ . The A89306 supports changing the direction input while the motor is running. The direction can also be controlled through register.

The direction can be controlled via I<sup>2</sup>C. When the DIR\_FROM\_ REG bit is set, the direction is controlled by the Direction bit XOR'd with the DIR terminal.

**BRAKE:** A logic high signal on the BRAKE terminal turns on all low sides for the braking function. The brake function overrides the input control. Typically, when braking, the winding current is limited only by  $V_{BEMF}/R_{MOTOR}$ . The A89306 includes an optional safe braking feature which holds off braking until the motor speed drops to a low enough level so that the braking current will not damage the MOSFETs. The safe braking current level is configurable in EEPROM. If this feature is not enabled, care should be taken to avoid stress on the MOSFETs when braking a spinning motor.

The Brake Function prevents the IC from entering standby mode.

Braking can be controlled via I<sup>2</sup>C. When the BRK\_FROM\_REG bit is set, the BRAKE pin is ignored, and the braking function is controlled by the BRK\_input bit.

**FAULT:** The FAULT terminal is an open-drain output which provides motor operation fault status. If used, the terminal must be pulled up externally and is high when there is no fault. The sink current should be limited to 10 mA or less.

An LED and a series resistor can be installed between the FAULT and VREG terminals for a visual indication of fault information.

| Fault type                      | FAULT terminal                                                                                                          | LED pattern                  |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Lock detected                   | low                                                                                                                     | constant on                  |

| OCP                             | 0.67 seconds high<br>0.67 seconds low                                                                                   | slow flashing                |

| Thermal shutdown                | 0.67 seconds low<br>0.17 seconds high<br>0.08 seconds low<br>0.17 seconds high<br>0.08 seconds low<br>0.17 seconds high | long-short-short<br>flashing |

| System error                    | 0.08 seconds low<br>0.08 seconds high<br>0.08 seconds low<br>1.09 seconds high                                          | double short flashing        |

| OVP                             | 0.17 seconds high<br>0.17 seconds low                                                                                   | fast flashing                |

| Input demand below<br>threshold | 0.25 seconds high<br>0.08 seconds low<br>0.34 seconds high<br>0.67 seconds low                                          | long-short flashing          |

**System Error:** A system error occurs when  $V_{BB}$ , the charge pump voltage, or the internal regulator which supplies the low-side gate drivers falls below the respective undervoltage threshold. The motor outputs are disabled upon a system error and will remain off until the voltage that caused the error rises above the respective UVLO threshold plus hysteresis.

**OVP:** An OVP event occurs when  $V_{BB}$  exceeds 47 V typical. OVP is only an indication and the outputs are not disabled. The indication is removed when  $V_{BB}$  falls below the threshold.

**FG:** The FG terminal is an open-drain output which provides motor speed information to the system. The open-drain output can be pulled up to VREG or an external 3.3 or 5 V supply.

The FG terminal is also used as SDA for the I<sup>2</sup>C interface. The first I<sup>2</sup>C command can only be written when the FG is high (i.e. the open drain is off). After the first I<sup>2</sup>C command, the FG terminal is no longer used for speed information output, and the FG terminal is dedicated as an SDA input for the I<sup>2</sup>C interface.

FG is default high after power on and exit from standby mode, and it remains high for at least 9.8 ms. After the 9.8 ms, the FG output will toggle as the motor spins. To ensure successful I<sup>2</sup>C communication, it is recommended to issue the first I<sup>2</sup>C command within 9.8 ms after power up or exiting from standby mode.

The FG function can be disabled in the EEPROM and in that case the FG terminal can be dedicated as the SDA signal for I<sup>2</sup>C. If observing FG signal is required in I<sup>2</sup>C mode, the FG output signal can be reassigned to the FAULT terminal by sending the

I<sup>2</sup>C command 0x00A0 to address 195 (decimal). To return the FAULT terminal to normal operation, send the I<sup>2</sup>C command 0x0000 to address 195 (decimal).

**VREG:** The VREG terminal is a voltage reference (2.8 V) to power internal digital logic and analog circuitry. VREG can be used to power external circuitry with up to 10 mA bias current, if desired. A ceramic capacitor with 0.22  $\mu$ F or greater is required on the terminal to stabilize the supply (X8R rating or better is recommended).

When VREG is loaded externally, the power consumption of the internal LDO is calculated by the equation:

$$P_{LDO} = (I_{LOAD} + I_{INTERNAL}) \times (V_{BB} - V_{REG}).$$

Ensure that the system has sufficient power dissipation and the temperature remains within the operating temperature range. The A89306 thermal shutdown function does not protect the LDO.

**Charge pump:** The VCP, CP1, and CP2 terminals are used to generate the voltage above  $V_{BB}$  to drive the high-side MOSFETs. A ceramic capacitor with 0.1  $\mu$ F or greater is required between VCP and VBB and between CP1 and CP2 (X8R rating or better is recommended).

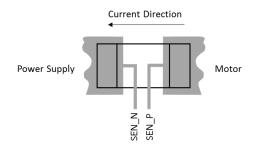

## **Bus Current Sensing**

A single shunt-resistor connecting between SENN and SENP is used to measure the bus current for the FOC algorithm and current limiting. The resistor value is about tens of a milliohm, depending on the rated current of the system. The integrated shunt-resistor amplifier has a gain of 14.5, and its output range is 0 to 1 V. Thus, the voltage difference between SENN and SENP should be less than 65 mV to prevent the signal saturation. For example, if the rated current is 4 A, it is recommended to use a 15 m $\Omega$  sensing resistor, so that 4 A × 15 m $\Omega$  is between 55 and 65 mV.

Use Kelvin sensing connections for the shunt resistor.

**Lock Detect:** A logic circuit monitors the motor position to determine if motor is running as expected. If a fault is detected, the motor drive will be disabled for the configurable  $t_{LOCK}$  time,

before an auto-restart is attempted. For additional information, refer to the application note.

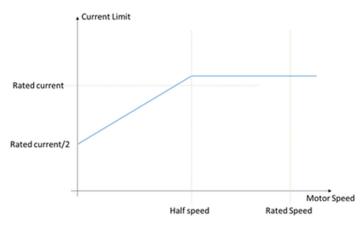

**Current Control:** The motor's rated current at rated speed and normal load must be programmed to the EEPROM for proper operation. The A89306 will limit the motor current (phase current peak value) to 1.125 times the programmed rated current during acceleration or increasing load, which protects the MOSFETs and the motor. A separate current limit for startup is programmed. At startup, the current limit increases linearly between the programmed startup current and 1.125 times the programmed rated current when the motor speed reaches one half of the rated speed setting. The following plot shows the current limit for the case when the startup current limit is set to rated current / 2:

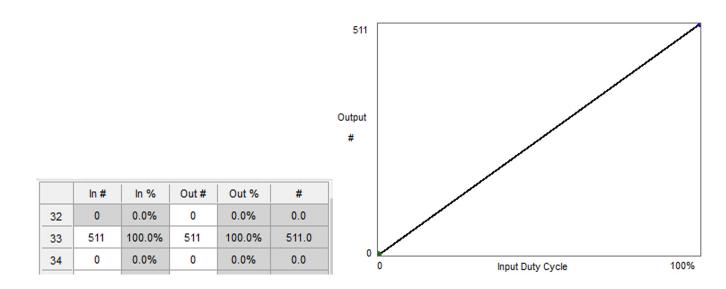

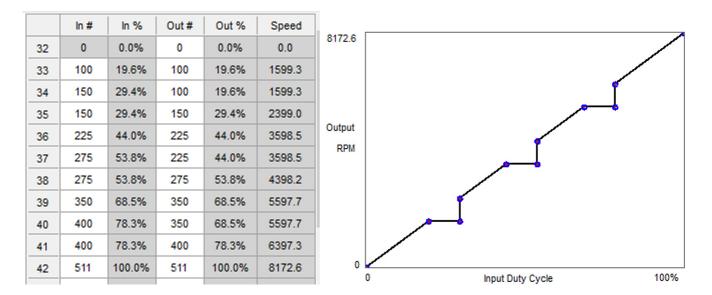

**Overcurrent Protection (short protection):** The VDS voltage across each power MOSFET is monitored by the A89306. When a MOSFET is switched on, its VDS is ignored for the programmable blank time. Also, the VDS is comparator is always filtered with a programmable filter time. If an enabled, MOS-FET's VDS is higher than the threshold after the blank time and for longer than the filter time, an OCP fault is triggered and the IC will latch all MOSFETs off. **Input-to-Output Transformer:** The A89306 implements an optional, highly flexible input-to-output mapping ability. The configuration is stored in EEPROM addresses 32 through 63. Fundamentally, the transformer is a 9-bit (0 to 511) to 9-bit (0 to 511) transfer function mapping the actual input value to a different value, and the meaning of the output value changes depending on the selected control mode. The transformer operates in whichever of the four control modes is selected: as a speed curve transformer, a current/torque curve transformer, a power curve transformer, or as a demand transformer in open-loop control mode.

If open-loop mode is selected, the specified output value determines the duty cycle applied to the motor. A value of 511 will cause the peak voltage applied to the motor to be the maximum. If one of the closed-loop modes is selected, the output range is determined by the CONTROL\_LOOP\_RANGE setting. That setting specifies the maximum speed, torque, or power that the application requires, and corresponds to the value 511. For example, in closed-loop speed mode, if the CONTROL\_LOOP\_ RANGE setting is set to 1000 rpm, then a transformer output value of 255 will result in the motor spinning at 500 rpm.

The curve is defined by corner points. The corner points specify specific input-to-output value pairs, and the remaining points are calculated using linear interpolation between the closest corner points. There must always be corner point entries for the input values 0 and 511, and up to 30 additional corner points can be defined.

The corner points are stored in the EEPROM, one point per address. The 9 MSBs of the EEPROM address are the input demand at the corner point, and the 9 LSBs of the address are the output demand for that point.

Only as many addresses that are needed to define the desired curve must be programmed. The last point defining the curve must have 511 as the input value, and all the following addresses in the EREPOM will be ignored. As many as 32 corner points can be stored, allowing for precise control of the demand.

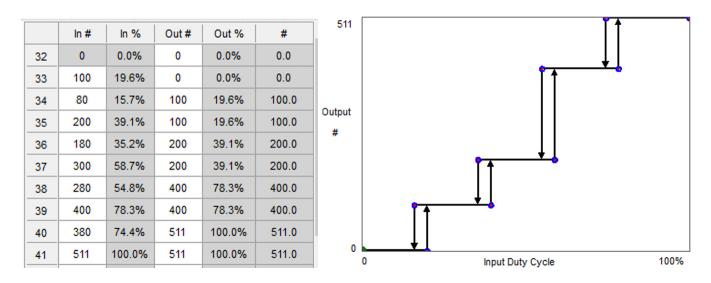

*Example 1:* These screenshots are taken from the A89306 application—white boxes are the entered values. This is the most trivial example, where input = output. This is the curve that is used when the transformer is disabled. Because 511 is the input value in the second address, the 30 following addresses are ignored.

*Example 2:* In this example, the control loop is set to closed-loop speed, and so the resulting rpm is shown in the last column of the table where the curve is defined. This curve is designed to avoid this motor's resonant frequency at 2000 rpm, and its harmonics at 4000 rpm and 6000 rpm.

*Example 3:* Hysteresis can be implemented by setting the input value of an address lower than the input value in the previous address. In this example, as the input demand is rising, the output demand will jump to next higher level at the vertical lines on the right of each transition. When the input demand is falling, the output demand will drop to next lower level following the vertical lines on the left of each transition. This prevents output jitter when the input is around a boundary.

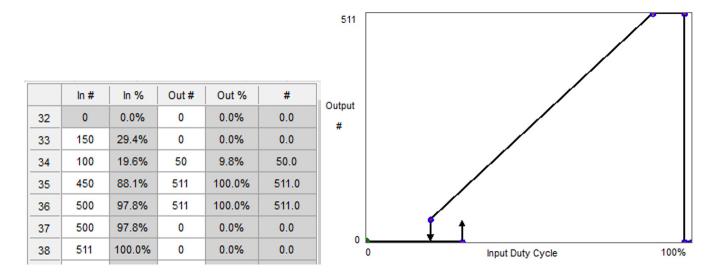

*Example 4:* In this example, the motor won't turn on until the input is about 30% and will turn off when the output falls below about 20%. The output will be at maximum when the input is between about 88% to 98%, and the motor will stop when the input is > 98%.

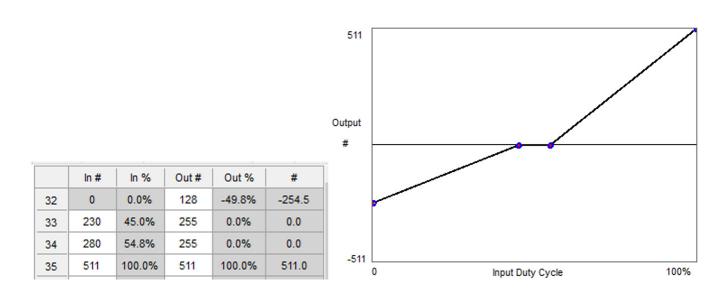

*Example 5:* The curve can be set to control bi-directional operation as well. When the bi-directional option is selected, the output value 511 is still the highest output in one direction, but the output value 255 will stop the motor, and the output value 0 is the highest output in the reverse direction. Here, the motor will run at half speed reverse when input demand is 0, will stop when the input is between 230 and 280, and will run at full speed forward when the input is 511.

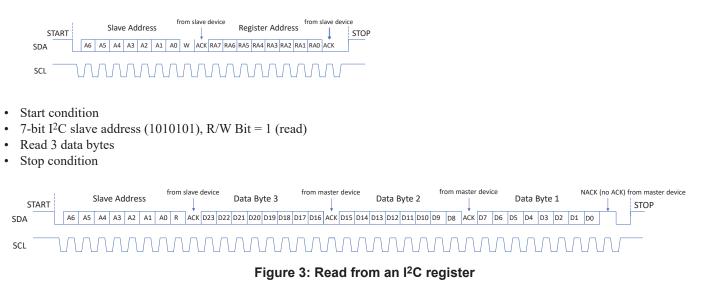

## I<sup>2</sup>C Operation and EEPROM/Register Map

The I<sup>2</sup>C interface allows the user to write to and read from the internal registers, and to program parameters into the EEPROM (writing to EEPROM is explained later in this document). The A89306 I<sup>2</sup>C 7-bit slave address, also referred to as the device ID, is fixed at 0x55. The figures below show the I<sup>2</sup>C interface timing. The I<sup>2</sup>C interface can operate at up to 400 kHz.

Upon power-up, the data in the EEPROM is loaded into a group of the internal registers (referred to as shadow registers), and those registers control the system operation. The register values can then be overwritten via the I<sup>2</sup>C port, and this will change the system operation on the fly. Any changes to the shadow registers will be overwritten upon the next power-up. Likewise, any changes made to the EEPROM will have no effect until the next power-up. The one exception to this is the data defining the input transformer curve, which does not have associated shadow registers—the data defining the curve is read directly from EEPROM during operation.

The addresses of the shadow registers are offset from their associated EEPROM addresses by 64. For example, EEPROM address 10 is loaded into shadow register 74 upon power-up. To change a parameter on the fly that is contained in EEPROM address 10, the data must be written to register 74 using the I<sup>2</sup>C port. There are no shadow registers associated with EEPROM addresses 0 through 7, or with addresses 32 through 63.

The following diagrams illustrate how to read and write to the registers using the I<sup>2</sup>C port.

### Write to a register:

- Start condition

- 7-bit I<sup>2</sup>C slave address (1010101), R/W Bit = 0 (write)

- Internal register address

- 3 data bytes, MSB first

- Stop condition

| START<br>SDA | Slave Address | from slave device<br>Register Address<br>A0 W ACK RA7 RA6 RA5 RA4 RA3 RA2 R | + | Data Byte 3 from slave | Data Byte 2 | from slave device | Data Byte 1 |     | STOP |

|--------------|---------------|-----------------------------------------------------------------------------|---|------------------------|-------------|-------------------|-------------|-----|------|

| SCL          |               |                                                                             |   |                        |             |                   |             | vvv |      |

Figure 2: Write to an I<sup>2</sup>C register

### Read from a register: a two-step process:

- Start condition

- 7-bit I<sup>2</sup>C slave address (1010101), R/W bit = 0 (write)

- Internal register address to be read

- Stop condition

## I<sup>2</sup>C Continuous Read

Note the master sends an ACK after each byte is received. After the 3 bytes of one register address is received, the master typically sends a NACK (no ACK) to indicate the transmission is complete. Alternatively, the master may continue reading from the next address by sending an ACK after the last byte, and the A89306 will begin sending data byte 3 of the next higher register address on the next clock edge. The A89306 will continue sending data from the next higher address until it receives a NACK. This allows for reading data from multiple registers quickly, without needing to write each specific address per the first step of this process. In this mode, the I<sup>2</sup>C speed must be limited to 100 kHz.

### **REGISTER AND EEPROM MAP**

Each register bit is associated with one EEPROM bit. The register address is the associated EEPROM bit address plus 64. For example, RATED\_SPEED is in EEPROM address 8, bits[10:0]; the associated register address is 72, bits[10:0].

In the following table, the bits that are not described should be kept at their default values. Changing these values may cause malfunction or damage to the part. If programming the EEPROM with a custom programmer, it is recommended to use the A89306 application to determine the appropriate settings, save the settings file, and use the file contents to program to the EEPROM. The application's settings file contains one line for each EEPROM address, containing addresses 8 through 63, but skipping address 31 (55 lines/addresses total).

Addresses 0 through 5 and address 31 are factory-locked and cannot be changed. Addresses 6 and 7 are available for the customer to use in any way that is useful, if desired.

Registers not shown in the table are not for users to access. Changing the value in undocumented registers may cause malfunction or damage to the part.

#### EEPROM address 0, Shadow register address 64

| Bits | Name      | Description                                                   |

|------|-----------|---------------------------------------------------------------|

| 15:0 | INFO_VAL0 | Allegro internal use (locked). No shadow register associated. |

#### EEPROM address 1, Shadow register address 65

| Bits | Name      | Description                                                   |

|------|-----------|---------------------------------------------------------------|

| 15:0 | INFO_VAL1 | Allegro internal use (locked). No shadow register associated. |

#### EEPROM address 2, Shadow register address 66

| Bits | Name      | Description                                                   |

|------|-----------|---------------------------------------------------------------|

| 15:0 | INFO_VAL2 | Allegro internal use (locked). No shadow register associated. |

#### EEPROM address 3, Shadow register address 67

| Bits | Name      | Description                                                   |

|------|-----------|---------------------------------------------------------------|

| 15:0 | INFO_VAL3 | Allegro internal use (locked). No shadow register associated. |

#### EEPROM address 4, Shadow register address 68

| Bits | Name      | Description                                                   |

|------|-----------|---------------------------------------------------------------|

| 15:0 | INFO_VAL4 | Allegro internal use (locked). No shadow register associated. |

#### EEPROM address 5, Shadow register address 69

| В | Bits | Name      | Description                                                   |

|---|------|-----------|---------------------------------------------------------------|

| 1 | 5:0  | INFO_VAL5 | Allegro internal use (locked). No shadow register associated. |

#### EEPROM address 6, Shadow register address 70

| Bits | Name      | Description                                                           |

|------|-----------|-----------------------------------------------------------------------|

| 15:0 | INFO_VAL6 | Available to customer for general use. No shadow register associated. |

#### EEPROM address 7, Shadow register address 71

| Bits | Name      | Description                                                           |

|------|-----------|-----------------------------------------------------------------------|

| 15:0 | INFO_VAL7 | Available to customer for general use. No shadow register associated. |

#### EEPROM address 8, Shadow register address 72

| Bits  | Name               | Description                                                                                                                                                            |

|-------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:15 | PWMIN_RANGE        | Input PWM frequency range selection<br>0: > 2.8 kHz<br>1: ≤ 2.8 kHz                                                                                                    |

| 14:14 | DIRECTION          | Direction of motor rotation<br>$0: A \rightarrow C \rightarrow B$<br>$1: A \rightarrow B \rightarrow C$                                                                |

| 13:13 | ACCELERATE_RANGE   | Acceleration range used for Startup Acceleration setting (Hz/s)<br>0: 0 to 816<br>1: 0 to 12.75                                                                        |

| 12:11 | DIGITAL_SPEED_MODE | SPD digital input mode<br>0: PWM mode<br>1: Clock mode (using SPD input)<br>2: Clock mode (using DIR input)<br>3: Clock mode (using BRAKE input)                       |

| 10:0  | RATED_SPEED        | This is the max speed used in the application.<br>In clock mode, this sets the max frequency, when PMW = 100%<br>Rated Speed (Hz) = RATED_SPEED_REGISTER_VALUE × 0.530 |

#### EEPROM address 9, Shadow register address 73

| Bits | Name | Description                                                                                                                      |

|------|------|----------------------------------------------------------------------------------------------------------------------------------|

|      |      | Specifies the motor acceleration rate at startup.<br>This setting's range is selected with the ACCELERATE RANGE setting, (Hz/s). |

#### EEPROM address 10, Shadow register address 74

| Bits  | Name            | Description                                                                                                                                                       |

|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:13 | STARTUP_CURRENT | Initial startup current limit (scale factor relative to Rated Current).<br>1 through 7: Startup Current = Rated Current × 1/8 × (value + 1).<br>Do not set to 0.  |

| 11:11 | SPD_MODE        | SPD input mode.<br>0: Digital (PWM or Clock mode).<br>1: Analog.                                                                                                  |

| 10:0  | RATED_CURRENT   | This is the motor current when running at the Rated_speed setting. Rated Current (mA) = RATED_<br>CURRENT_REGISTER_VALUE / (SENSE_RESISTOR_REGISTER_VALUE / 125). |

#### EEPROM address 11, Shadow register address 75

| Bits  | Name            | Description                                                                                                                                                     |

|-------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11:10 | STARTUP_MODE    | 00: 6-pulse mode<br>01: 2-pulse mode<br>10: Slight-move mode<br>11: Align & go                                                                                  |

| 7:7   | POWER_CTR_EN    | Power control enable<br>0: Disable the current limit and accelerate and decelerate buffers<br>1: Enable the current limit and accelerate and decelerate buffers |

| 4:4   | OPEN_PH_PROTECT | 0: Disable the open phase protection function<br>1: Enable the open phase protection function                                                                   |

| 3:3   | OPEN_DRIVE      | Open-drive debug control<br>0: Normal operation<br>1: Motor will be driven in open loop, Rated speed is then the target speed.                                  |

#### EEPROM address 12, Shadow register address 76

| Bits  | Name        | Description                                                                                            |

|-------|-------------|--------------------------------------------------------------------------------------------------------|

| 16:16 | OPEN_WINDOW | Opens a window for inductance tuning – see application note<br>0: Normal operation<br>1: Window opened |

| 4:0   | PID_P       | Position observer PI loop proportional constant                                                        |

#### EEPROM address 13, Shadow register address 77

| Bits  | Name        | Description                                                                                                                                                                                                          |

|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14:14 | DELAY_START | Delay startup (for startup modes other than Align & go)<br>0: V <sub>BB</sub> must be stable within 25 ms after applying start signal<br>1: V <sub>BB</sub> must be stable within 100 ms after applying start signal |

#### EEPROM address 14, Shadow register address 78

| Bits | Name       | Description                                                                                                                                          |

|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4:4  | FG_PIN_DIS | 0: FG terminal operates as FG (until 1st successful I <sup>2</sup> C write)<br>1: FG terminal disabled as FG, for I <sup>2</sup> C-only applications |

#### EEPROM address 15, Shadow register address 79

| Bits  | Name             | Description                                                                                                                                                                                                                                                                                        |

|-------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16:14 | SAFE_BRAKE_THRD  | Current below which to allow braking, relative to rated current<br>000: 1 × RATED_CURRENT<br>001: 1/2 × RATED_CURRENT<br>010: 1/4 × RATED_CURRENT<br>011: 1/8 × RATED_CURRENT<br>100: 1/16 × RATED_CURRENT<br>101: 1/32 × RATED_CURRENT<br>110: 1/64 × RATED_CURRENT<br>111: 1/128 × RATED_CURRENT |

| 11:8  | DEADTIME_SETTING | Deadtime selection<br>0: 640 ns<br>1 through 15: (value + 1) × 40 ns                                                                                                                                                                                                                               |

| 7:7   | SOFT_ON          | 0: Disabled<br>1: Gradually increases the current at startup during a windmilling startup                                                                                                                                                                                                          |

| 6:6   | SOFT_OFF         | 0: Disabled<br>1: Gradually reduces the current at motor stop                                                                                                                                                                                                                                      |

| 3:2   | ANGLE_ERROR_LOCK | Lock detect during startup.<br>00: disabled<br>01: 5 degrees<br>10: 9 degrees<br>11: 13 degrees                                                                                                                                                                                                    |

#### EEPROM address 16, Shadow register address 80

| Bits  | Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13:12 | BEMF_LOCK_FILTER  | Determines the filter time for the BEMF lock detection<br>00: Lock detection disabled<br>01: Robust<br>10: Medium<br>11: Sensitive                                                                                                                                                                                                                                                                                                                                                              |

| 11:10 | DECLARATE_BUFFER  | Determines how quickly the output command can slew<br>00: No buffer<br>01: Fast buffer<br>10: Medium buffer<br>11: Slow buffer                                                                                                                                                                                                                                                                                                                                                                  |

| 9:8   | ACCELERATE_BUFFER | Determines how quickly the output command can slew<br>00: No buffer<br>01: Fast buffer<br>10: Medium buffer<br>11: Slow buffer                                                                                                                                                                                                                                                                                                                                                                  |

| 7:6   | FIRST_CYCLE_SPEED | Determines the align duration for Align & go startup mode<br>00: 0.55 Hz (1.81 seconds)<br>01: 1.1 Hz (0.91 seconds)<br>10: 2.2 Hz (0.45 seconds)<br>11: 4.4 Hz (0.23 seconds)                                                                                                                                                                                                                                                                                                                  |

| 5:4   | OCP_MASKING       | OCP comparators mask/blank time. Mask/blank occurs at output on/off transition<br>00: No masking<br>01: 320 ns mask<br>10: 640 ns mask<br>11: 1280 ns mask                                                                                                                                                                                                                                                                                                                                      |

| 3:3   | OCP_RESET_MODE    | Determines when to restart motor after OCP is tripped<br>0: Upon motor restart<br>1: After 5 seconds                                                                                                                                                                                                                                                                                                                                                                                            |

| 2:0   | OCP_ENABLE        | OCP filter time and HS/LS OCP enabling. If an overcurrent condition exists at the time the OCP mask<br>expires, the OCP filter time must pass before an OCP fault is triggered.<br>000: No Filter, HS/LS OCP Enabled<br>001: 120 ns, HS/LS OCP Enabled<br>010: 240 ns, HS/LS OCP Enabled<br>011: 360 ns, HS/LS OCP Enabled<br>100: 480 ns, HS/LS OCP Enabled<br>101: 480 ns, LS OCP Enabled, HS OCP Disabled<br>110: 480 ns, LS OCP Disabled, HS OCP Enabled<br>111: 480 ns, HS/LS OCP Disabled |

#### EEPROM address 17, Shadow register address 81

| Bits | Name           | Description                                                                                                                                                                                    |

|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9:9  | I2C_SPEED_MODE | Input command via I <sup>2</sup> C enable<br>0: IC terminals are used for user input command, according to settings<br>1: Speed_demand setting in this register is used for user input command |

| 8:0  | SPEED_DEMAND   | Speed demand input, when I2C_SPEED_MODE is enabled $0 \rightarrow 511$ represents $0 \rightarrow 100\%$                                                                                        |

#### EEPROM address 18, Shadow register address 82

| Bits  | Name            | Description                                                                   |

|-------|-----------------|-------------------------------------------------------------------------------|

| 15:14 | DRIVE_GATE_SLEW | Gate driver current control. Refer to the Electronics Characterization table. |

| 13:8  | IPD_CURRENT_THR | IPD current threshold (A) = IPD_CURRENT_THRD_VALUE × 0.086                    |

#### EEPROM address 19, Shadow register address 83

| Bits  | Name                | Description                                                                  |

|-------|---------------------|------------------------------------------------------------------------------|

| 15:12 | MOSFET_COMP_FALLING | MOSFET CISS compensation, current falling.<br>Refer to the application note. |

| 11:8  | MOSFET_COMP_RISING  | MOSFET CISS compensation, current rising.<br>Refer to the application note.  |

#### EEPROM address 20, Shadow register address 84

| Bits | Name           | Description                                                     |

|------|----------------|-----------------------------------------------------------------|

| 15:8 | SENSE_RESISTOR | Sense resistor value (m $\Omega$ ) = SENSE_RESISTOR_VALUE / 3.7 |

| 7:0  | RATED_VOLTAGE  | Motor rated voltage (V) = RATED_VOLTAGE_REGISTER_VALUE / 5      |

#### EEPROM address 21, Shadow register address 85

| Bits  | Name                          | Description                                                                                                                                                                                                              |

|-------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:15 | STANDBY_DIS                   | Standby mode disable<br>0: Normal standby operation<br>1: Standby mode disabled                                                                                                                                          |

| 9:8   | SPEED_INPUT_OFF_<br>THRESHOLD | Input threshold below which the motor is turned off.<br>If the input transformer curve is enabled, this is applied after (to the output of) the transformer curve.<br>00: 9.7 %<br>01: 5.8 %<br>10: 12.8 %<br>11: 19.5 % |

| 7:5   | SLIGHT_MV_DEMAND              | Amplitude demand used for slight move startup mode<br>(%) = value × 3.2 + 2.4                                                                                                                                            |

#### EEPROM address 22, Shadow register address 86

| Bits  | Name              | Description                                                                                                                                                                                     |

|-------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:15 | VDS_THRESHOLD_SEL | Short-circuit protection VDS threshold<br>0: 1 V<br>1: 2 V                                                                                                                                      |

| 12:12 | DEADTIME_COMP     | Deadtime compensation enable<br>0: Disabled<br>1: Enabled                                                                                                                                       |

| 11:11 | LOCK_RESTART_SET  | How long to wait before restart after lock detect is triggered<br>0: 5 seconds<br>1: 10 seconds                                                                                                 |

| 10:10 | VIBRATION_LOCK    | Vibration lock detect<br>0: Disabled<br>1: Enabled                                                                                                                                              |

| 9:9   | SOFT_OFF_4S       | Soft-off duration<br>0: 1 second<br>1: 4 seconds                                                                                                                                                |

| 8:8   | BRAKE_MODE        | Brake mode<br>0: Brake when safe, according to the SAFE_BRAKE_THRD setting<br>1: Always brake, 100% uncontrolled                                                                                |

| 7:6   | RESTART_ATTEMPT   | When to restart after lock detect is triggered<br>00: Always<br>01: 3 times<br>10: 5 times<br>11: 10 times                                                                                      |

| 5:0   | CLOCK_SPEED_RATIO | The ratio between input frequency and rpm, used during clock mode.<br>(rpm/Hz) = CLOCK_SPEED_RATIO_VALUE × 0.25.<br>The maximum CLOCK_SPEED_RATIO value is 41; higher values will cause errors. |

#### EEPROM address 23, Shadow register address 87

| Bits  | Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17:17 | CHECK_CURVE     | Input transformer curve enable<br>0: Input curve disabled<br>1: Input curve enabled                                                                                                                                                                                                                                                                                                                                           |

| 16:16 | SPEED_CUR_BIDIR | Input transformer curve single or bi-directional mode<br>0: Input curve operates in a unidirectional mode and the direction is set by the device terminal or via I <sup>2</sup> C register<br>1: Input curve operates in a bidirectional mode where the value 0 is the fastest reverse direction, 511 is the fasted<br>forward direction, and 255 will stop the motor                                                         |

| 12:11 | OPERATION_MODE  | Control loop mode<br>00: Open loop operation, output voltage magnitude set by input demand<br>01: Constant torque operation, torque range is set by PARAMETERFULL (EEPROM_23[10:0]) × demand (as ratio)<br>10: Constant speed operation, speed range is set by PARAMETERFULL (EEPROM_23[10:0]) × demand (as ratio)<br>11: Constant power operation, power range is set by PARAMETERFULL (EEPROM_23[10:0]) × demand (as ratio) |

| 10:0  | PARAMETERFULL   | Used in constant speed/torque/power control loops to set the maximum control setpoint. This value is the setpoint when the input demand is 100%.                                                                                                                                                                                                                                                                              |

#### EEPROM address 24, Shadow register address 88

| Bits | Name           | Description                                                                 |

|------|----------------|-----------------------------------------------------------------------------|

| 7:0  | MOTOR_RESISTOR | Motor phase terminal to center-tap resistance (phase-phase resistance / 2). |

#### EEPROM address 25, Shadow register address 89

| Bits  | Name             | Description                                                                                                                                                    |

|-------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:15 | BRK_INPUT        | I <sup>2</sup> C brake mode input when BRK_FROM_REG = 1<br>0: Normal running<br>1: Brake mode applied                                                          |

| 14:14 | BRK_FROM_REG     | Motor brake mode control option<br>0: Brake is controlled via the device terminal<br>1: Brake is controlled via the I <sup>2</sup> C brake register            |

| 13:13 | DIR_FROM_REG     | Motor direction control option<br>0: Direction is controlled via the device terminal<br>1: Direction is controlled via the I <sup>2</sup> C direction register |

| 10:8  | INDUCTANCE_SHIFT | Motor inductance multiplier – the inductance setting is multiplied by 2 ^ INDUCTANCE_SHIFT                                                                     |

| 7:0   | INDUCTANCE       | Motor inductance, set along with the Inducatnce_shift setting – this value is multiplied by 2 ^ INDUCTANCE_SHIFT                                               |

#### EEPROM address 26, Shadow register address 90

| Bits | Name   | Description       |

|------|--------|-------------------|

| 8:0  | KT_SET | Motor Kt constant |

#### EEPROM address 28, Shadow register address 92

| Bits  | Name           | Description                           |

|-------|----------------|---------------------------------------|

| 17:15 | CURRENT_LOOP_I | Current PI loop integration constant  |

| 14:10 | POWER_LOOP_P   | Power PI loop proportional constant   |

| 9:5   | SPEED_LOOP_P   | Speed PI loop proportional constant   |

| 4:0   | CURRENT_LOOP_P | Current PI loop proportional constant |

#### EEPROM address 29, Shadow register address 93

| Bits | Name         | Description                        |

|------|--------------|------------------------------------|

| 5:3  | POWER_LOOP_I | Power PI loop integration constant |

| 2:0  | SPEED_LOOP_I | Speed PI loop integration constant |

#### EEPROM address 31, Shadow register address 95

| Bits | Name              | Description                             |

|------|-------------------|-----------------------------------------|

| 15:0 | OUTPUT_ARRAY_TRIM | Allegro-determined trim values (locked) |

#### EEPROM addresses 32-63 (No shadow registers associated)

| Bits | Name                  | Description                                                                               |

|------|-----------------------|-------------------------------------------------------------------------------------------|

| 17:9 | X_INTERPOLATION_POINT | Corner point input value for the input transformer curve. No shadow register associated.  |

| 8:0  | Y_INTERPOLATION_POINT | Corner point output value for the input transformer curve. No shadow register associated. |

Note: Refer to application note and user interface for additional detail.

## **PROGRAMMING THE EEPROM**

The A89306 contains 64 words of EEPROM, and each word is 24 bits long. The 6 most significant bits of each word are used internally for error detection and correction (ECC), and the 18 least significant bits are used to store data. The handling of the ECC data is done automatically by the IC, and the user does not need to (and cannot) read or write the ECC data.

The EEPROM is programmed using the I<sup>2</sup>C interface. Before accessing the EPEPOM, access must be enabled by writing the value 0x000001 I<sup>2</sup>C register address 196. When done accessing the EEPROM, revert to normal operation by writing the value 0x000000 to I<sup>2</sup>C register address 196. There are three basic actions which can be performed on the EEPROM: read, erase, and write. Erasing a single address in the EEPROM

requires 4 writes to the I<sup>2</sup>C port, and writing to a single address in the EEPROM require 3 writes to the I<sup>2</sup>C port. These registers, addresses 161, 162, and 163, are described below and the sequence for writing to these registers is described on the following page. Reading a single address from the EEPROM requires only 1 read from the I<sup>2</sup>C port. Each EEPROM address is mapped the corresponding I<sup>2</sup>C address. To read EEPROM address 8, for example, simply read I<sup>2</sup>C register address 8.

Each EEPROM address must be programmed individually. To change the contents of an EEPROM address, the word must first be erased before the new data is written. Programming each address requires about 45 ms (30 ms for erase and 15 ms for write).

#### EEPROM Control – Register 161: Used to control programming of EEPROM

| Bit  | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3  | 2  | 1  | 0  |

|------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|----|----|----|----|

| Name | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | RD | WR | ER | EN |

|      |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |    |    |    |    |

| Bit  | Name | Description                                                                                                           |

|------|------|-----------------------------------------------------------------------------------------------------------------------|

| 0    | EN   | Generate the high-voltage pulse required for writing or erasing. This bit self-clears when done, after 15 ms maximum. |

| 1    | ER   | Set this bit high when erasing data to the EEPROM.                                                                    |

| 2    | WR   | Set this bit high when writing data to the EEPROM.                                                                    |

| 3    | RD   | This bit is for reading data, but is not required for the method described in this datasheet to read the EEPROM.      |

| 23:4 | n/a  | Do not use; always set to zero (0) during programming process.                                                        |

#### EEPROM Address - Register 162: Used to set the EEPROM address to be altered

| Bit  | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3     | 2    | 1 | 0 |

|------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|-------|------|---|---|

| Name | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 |   |   | eeADD | RESS |   |   |

| Bit  | Name      | Description                                                                         |

|------|-----------|-------------------------------------------------------------------------------------|

| 5:0  | eeADDRESS | Used to specify the EEPROM address to be erased or written. There are 64 addresses. |

| 23:6 | n/a       | Do not use; always set to zero (0) during programming process.                      |

#### EEPROM Data\_In - Register 163: Used to set the new EEPROM data to be programmed

| Bit   | 23 | 22    | 21 | 20    | 19                                                                                         | 18          | 17 | 16       | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----|-------|----|-------|--------------------------------------------------------------------------------------------|-------------|----|----------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Name  | 0  | 0     | 0  | 0     | 0                                                                                          | 0           |    | eeDATAin |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|       |    |       |    |       |                                                                                            |             |    |          |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Bit   |    | Name  |    |       |                                                                                            | Description |    |          |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| 17:0  | e  | eDATA | in | Used  | d to specify the new EEPROM data. This must be set to 0 when erasing the current contents. |             |    |          |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| 23:18 |    | n/a   |    | Do no | not use; always set to zero (0) during programming process.                                |             |    |          |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

### **Programming the EEPROM Examples**

The example below is shown in the following format:

I<sup>2</sup>C Write/Read, I2C\_register\_address [data] // comment

\*Before accessing the EEPROM, the value 0x000001 must be written to I<sup>2</sup>C address 196.

Example #1: Write 261 (0x000105) to EEPROM address 7

1. Erase the existing data:

|    | A. I <sup>2</sup> C Write, 162 [7]                                            | // set which EEPROM address to erase.          |  |  |  |  |  |  |

|----|-------------------------------------------------------------------------------|------------------------------------------------|--|--|--|--|--|--|

|    | B. I <sup>2</sup> C Write, 163 [0]                                            | // set Data_In = $0x000000$ .                  |  |  |  |  |  |  |

|    | C. I <sup>2</sup> C Write, 161 [3]                                            | // set control to erase and set voltage high.  |  |  |  |  |  |  |

|    | D. Wait 15 ms                                                                 | // requires 15 ms high-voltage pulse to erase. |  |  |  |  |  |  |

|    | E. I <sup>2</sup> C Write, 161 [3]                                            | // set control to erase and set voltage high.  |  |  |  |  |  |  |

|    | F. Wait 15 ms                                                                 | // requires 15 ms high-voltage pulse to erase. |  |  |  |  |  |  |

| 2. | Write the new data:                                                           |                                                |  |  |  |  |  |  |

|    | A. I <sup>2</sup> C Write, 162 [7]                                            | // set which EEPROM address to write.          |  |  |  |  |  |  |

|    | B. I <sup>2</sup> C Write, 163 [261]                                          | // set Data_In = 261 (0x000105).               |  |  |  |  |  |  |

|    | C. I <sup>2</sup> C Write, 161 [5]                                            | // set control to write and set voltage high.  |  |  |  |  |  |  |

|    | D. Wait 15 ms                                                                 | // requires 15 ms high-voltage pulse to write. |  |  |  |  |  |  |

| Ex | Example #2: Read EEPROM address 7 to confirm the data was properly programmed |                                                |  |  |  |  |  |  |

|    |                                                                               |                                                |  |  |  |  |  |  |

1. Read the word:

A. I<sup>2</sup>C Read, 7 // read I2C register 7; this will be contents of EEPROM address 7.

\*When done accessing the EEPROM, write the value 0x000000 to I<sup>2</sup>C address 196.

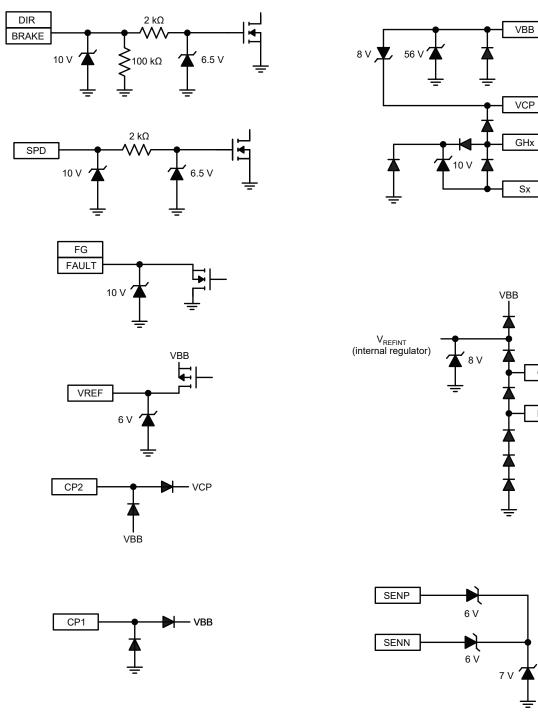

**TERMINAL DIAGRAMS**

Sx

GLx

LSS

#### Figure 5: Package ET, 28-Contact QFN with Exposed Pad

## 50 V Ultra-Low Noise FOC Motor Controller

#### **Revision History**

| Number | Date           | Description                                               |

|--------|----------------|-----------------------------------------------------------|

| -      | March 19, 2020 | Initial release                                           |

| 1      | March 17, 2022 | Updated package drawing (page 25)                         |

| 2      | March 27, 2024 | Updated register notation to current standard (uppercase) |

Copyright 2024, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.