### FEATURES AND BENEFITS

- Closed-loop speed control

- Overvoltage protection

- Power loss brake

- Fault mode brake

- Configurable RD or FG output

- Speed curve configuration via EEPROM

- I<sup>2</sup>C serial port

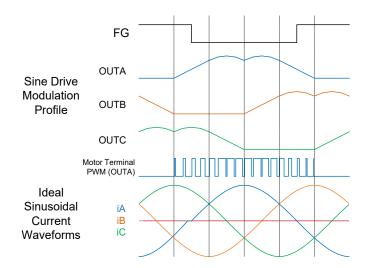

- Sinusoidal modulation for reduced audible noise and low vibration

- Sensorless (no Hall sensors required)

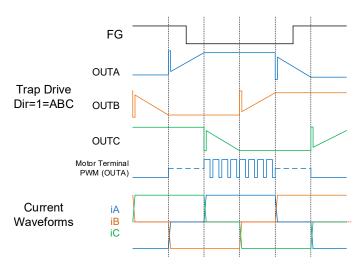

- Trapezoidal drive option for high speed

- Low R<sub>ds(on)</sub> power MOSFETs 3 A capability

- PWM duty cycle speed input

- FG speed output

- Lock detection

- Soft start

- Shorted load protection

## **APPLICATIONS**

- High-speed 12 V server cooling fans

- Industrial and consumer blowers and fans

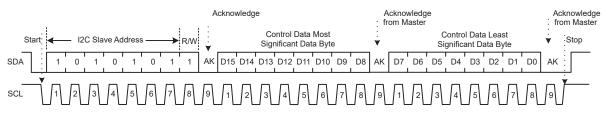

## DESCRIPTION

The A89331 three-phase motor driver incorporates sensorless sinusoidal drive to minimize vibration for high-speed server fans. Sensorless control eliminates the requirement for Hall sensors for server fan applications.

A flexible closed-loop speed control system is integrated into the IC. EEPROM is used to tailor the common functions of the fan speed curve to a specific application. This eliminates the requirement for a microprocessor-based system and minimizes programming requirements.

The A89331 is available in a 28-lead 5 mm  $\times$  5 mm QFN with exposed power pad (suffix ET), and a 20-lead TSSOP with exposed power pad (suffix LP).

### PACKAGES:

20-lead TSSOP with exposed thermal pad (LP package)

28-contact QFN with exposed thermal pad 5 mm × 5 mm × 0.90 mm (ET package)

Not to scale

#### +12 Vin 0.1 μF 0.1 uF 25 kΩ / 0.1% SYS ROS CIK Charge Pump VREF VINT Loss VBB Brake Vcp 22 uF 22 µF 3 p# Timing Control Duty In $-\Lambda \Lambda \Lambda$ PWM OUTC GATE OUTB DRIVE OUTA FG/RD P Speed System Control Variables Loop Current DATA Limit I2C/EEPROM CLK OUTA Position -OUTB GND CTA Measure OUTC

## TYPICAL APPLICATION

#### **SELECTION GUIDE**

| Part Number   | Package                             | Packing                      |

|---------------|-------------------------------------|------------------------------|

| A89331GETSR   | 28-pin QFN with exposed thermal pad | 6000 pieces per 13-inch reel |

| A89331GLPTR-T | 20-pin TSSOP with exposed power pad | 4000 pieces per 13-inch reel |

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic              | Symbol                                 | Notes                               | Rating              | Unit |

|-----------------------------|----------------------------------------|-------------------------------------|---------------------|------|

| Supply Veltoge              |                                        | DC                                  | –0.3 to 18          | V    |

| Supply Voltage              | V <sub>BB</sub>                        | t <sub>w</sub> < 10 ms              | -0.3 to 20          | V    |

| Control Input               | V <sub>IN</sub> , V <sub>PLBENB</sub>  | VIN, PLBENB                         | –0.3 to 18          | V    |

| Analog Input                | V <sub>ROSC</sub>                      | ROSC                                | 4                   | V    |

| Logic Input Voltage Range   | V <sub>PWM</sub> , V <sub>nBRAKE</sub> | PWM, nBRAKE                         | -0.3 to 6           | V    |

| Logic Output                | V <sub>FG/RD</sub> , V <sub>nFLT</sub> | FG/RD, nFLT                         | V <sub>BB</sub>     | V    |

| Output Current              | L [1]                                  | DC                                  | Internally Limited  | А    |

| Output Current              | I <sub>OUT</sub> <sup>[1]</sup>        | Peak Brake Mode Current; t < 500 ms | 6.5                 | А    |

| Output Voltage              | V <sub>OUT</sub>                       |                                     | V <sub>BB</sub> + 1 | V    |

| Junction Temperature        | TJ                                     |                                     | 150                 | °C   |

| Storage Temperature Range   | T <sub>stg</sub>                       |                                     | -55 to 150          | °C   |

| Operating Temperature Range | T <sub>A</sub>                         |                                     | -40 to 105          | °C   |

<sup>[1]</sup> Power dissipation and thermal limits must be observed.

#### THERMAL CHARACTERISTICS

| Characteristic             | Symbol           | Test Conditions*                                       | Value | Unit |

|----------------------------|------------------|--------------------------------------------------------|-------|------|

|                            |                  | ET package, 2-sided PCB with 1 in. <sup>2</sup> copper | 42    | °C/W |

| Package Thermal Resistance | R <sub>θJA</sub> | LP package, 2-sided PCB with 1 in. <sup>2</sup> copper | 35    | °C/W |

\*Additional thermal information available on the Allegro website.

### **RECOMMENDED OPERATIONAL RANGE**

| Characteristics           | Symbol                                 | Test Conditions                                       | Min. | Тур. | Max. | Unit |

|---------------------------|----------------------------------------|-------------------------------------------------------|------|------|------|------|

| Supply Voltage            | V <sub>BB</sub>                        | DC                                                    | 8    | 12   | 15   | V    |

| Logic Input Voltage Range | V <sub>PWM</sub> , V <sub>nBRAKE</sub> | PWM, nBRAKE                                           | -0.3 | _    | 5.5  | V    |

| Motor Current             | I <sub>OUT</sub>                       | Peak Motor Phase Current - Sinusoidal<br>Running Mode | _    | _    | 3    | А    |

## **Three-Phase Sensorless Fan Driver**

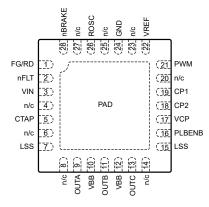

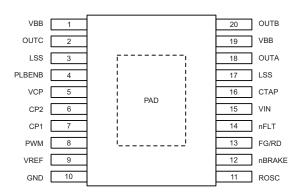

### **PINOUT DIAGRAMS AND PINOUT LIST**

**ET-28 Package Pinouts**

**LP-20 Package Pinouts**

#### **Pinout List**

| Pin N | umber | Pin Name  | Function                   |

|-------|-------|-----------|----------------------------|

| ET-28 | LP-20 | Fill Name | Function                   |

| 1     | 13    | FG/RD     | Output Signal              |

| 2     | 14    | nFLT      | Logic Output Signal        |

| 3     | 15    | VIN       | Power Supply Sense Node    |

| 4     | _     | n/c       | No Connect                 |

| 5     | 16    | CTAP      | Motor Terminal             |

| 6     | _     | n/c       | No Connect                 |

| 7     | 17    | LSS       | Low Side Source Connection |

| 8     | _     | n/c       | No Connect                 |

| 9     | 18    | OUTA      | Motor Terminal             |

| 10    | 19    | VBB       | Input Supply               |

| 11    | 20    | OUTB      | Motor Terminal             |

| 12    | 1     | VBB       | Input Supply               |

| 13    | 2     | OUTC      | Motor Terminal             |

| 14    | _     | n/c       | No Connect                 |

| Pin Nu | umber | Din Nome | Function                   |

|--------|-------|----------|----------------------------|

| ET-28  | LP-20 | Pin Name | Function                   |

| 15     | 3     | LSS      | Low Side Source Connection |

| 16     | 4     | PLBENB   | Logic Input                |

| 17     | 5     | VCP      | Charge Pump Capacitor      |

| 18     | 6     | CP2      | Charge Pump Capacitor      |

| 19     | 7     | CP1      | Charge Pump Capacitor      |

| 20     | _     | n/c      | No Connect                 |

| 21     | 8     | PWM      | Logic Input – Speed Demand |

| 22     | 9     | VREF     | Reference Voltage Output   |

| 23     | _     | n/c      | No Connect                 |

| 24     | 10    | GND      | Ground                     |

| 25     | _     | n/c      | No Connect                 |

| 26     | 11    | ROSC     | Analog Input               |

| 27     | _     | n/c      | No Connect                 |

| 28     | 12    | nBRAKE   | Logic Input                |

### **ELECTRICAL CHARACTERISTICS** <sup>[1]</sup>: Valid at $T_J = 25^{\circ}$ C, $V_{BB} = 5$ to 16 V, unless noted otherwise

| Characteristics                           | Symbol                | Test Conditions                                                             | Min. | Тур.  | Max. | Unit |

|-------------------------------------------|-----------------------|-----------------------------------------------------------------------------|------|-------|------|------|

| GENERAL                                   |                       | ·                                                                           |      |       |      |      |

| VPP Current Current                       | I <sub>BB</sub>       | V <sub>IN</sub> > V <sub>INTH</sub> , V <sub>BB</sub> > V <sub>BBUVLO</sub> | _    | 13.5  | 16.5 | mA   |

| VBB Supply Current                        | I <sub>BB2</sub>      | V <sub>IN</sub> < V <sub>INTH</sub>                                         | _    | 0.5   | 1.35 | mA   |

| VREF                                      | V <sub>REF</sub>      | I = 0 to 10 mA                                                              | 2.75 | 2.85  | 2.95 | V    |

|                                           |                       | Falling                                                                     | 3.6  | 3.9   | 4.2  | V    |

| VCP UVLO                                  | V <sub>CPUVLO</sub>   | Rising                                                                      | 3.95 | 4.25  | 4.55 | V    |

| POWER DRIVER                              |                       | ``````````````````````````````````````                                      |      |       |      |      |

|                                           |                       | I <sub>OUT</sub> = 1.5 A, T <sub>J</sub> = 25°C, V <sub>BB</sub> = 12 V     | _    | 210   | 250  | mΩ   |

|                                           |                       | Source driver                                                               | _    | 105   | _    | mΩ   |

|                                           |                       | Sink driver                                                                 | _    | 105   | _    | mΩ   |

| Total Driver $R_{ds(on)}$ (Sink + Source) | R <sub>ds(on)</sub>   | I <sub>OUT</sub> = 1.5 A, T <sub>J</sub> = 125°C, V <sub>BB</sub> = 12 V    | _    | 300   | 360  | mΩ   |

|                                           |                       | Source driver, T <sub>J</sub> = 125°C                                       | _    | 150   | _    | mΩ   |

|                                           |                       | Sink driver, T <sub>J</sub> = 125°C                                         | _    | 150   | _    | mΩ   |

| SPEED CONTROL                             |                       | · · · · · · · · · · · · · · · · · · ·                                       |      |       |      |      |

| PWM Duty Input                            | f <sub>PWM</sub>      |                                                                             | 0.1  | _     | 100  | kHz  |

| Duty Cycle On Threshold                   | DC <sub>ON</sub>      | Relative to target                                                          | -0.5 | _     | 0.5  | %    |

| Duty Cycle Off Threshold                  | DC <sub>OFF</sub>     | Relative to target                                                          | -0.5 | _     | 0.5  | %    |

|                                           | f <sub>SPD</sub>      | T <sub>J</sub> = 25°C, R <sub>OSC</sub> = 25 kΩ                             | -1.5 | _     | 1.5  | %    |

| Speed Setpoint                            |                       | $T_J = -40^{\circ}$ C to 125°C, $R_{OSC} = 25 \text{ k}\Omega$              | -2   | _     | 2    | %    |

|                                           |                       | T <sub>J</sub> = 25°C, R <sub>OSC</sub> = 25 kΩ                             | -1   | _     | 1    | %    |

| System Oscillator f <sub>OSC</sub>        |                       | $T_J = -40^{\circ}$ C to 125°C, $R_{OSC} = 25 \text{ k}\Omega$              | -1.5 | _     | 1.5  | %    |

| PROTECTION CIRCUITS                       |                       | ·                                                                           |      |       |      | ,    |

| Lock Protection                           | t <sub>OFF</sub>      | Relative to target                                                          | -10  | _     | 10   | %    |

| Overcurrent Limit                         | I <sub>OCL</sub>      | V <sub>BB</sub> > V <sub>BBUVLO</sub>                                       | -25  | _     | 25   | %    |

| Overcurrent Protection                    | I <sub>OCP</sub>      |                                                                             | 6.5  | _     | _    | A    |

| Thermal Shutdown Temperature              | T <sub>JTSD</sub>     | Temperature increasing                                                      | 150  | 165   | 180  | °C   |

| Thermal Shutdown Hysteresis               | ΔT <sub>J</sub>       | Recovery = $T_{JTSD} - \Delta T_J$                                          | _    | 20    | _    | °C   |

| N/DEE 11/1/ 0                             |                       | V <sub>REF</sub> rising                                                     | 2.56 | 2.63  | 2.75 | V    |

| VREF UVLO                                 | V <sub>REFUVLO</sub>  | V <sub>REF</sub> falling                                                    | 2.4  | 2.48  | 2.55 | V    |

| VREF UVLO Hysteresis                      | V <sub>REFHYS</sub>   |                                                                             | 100  | 150   | 200  | mV   |

| VBB Overvoltage                           | V <sub>BBOVTH</sub>   |                                                                             | 16.5 | 17.25 | 18   | V    |

| VBB Overvoltage Hysteresis                | V <sub>BBOHYS</sub>   |                                                                             | _    | 1.5   | _    | V    |

| VBB UVLO                                  | V <sub>BBUVLO</sub>   | V <sub>BB</sub> rising                                                      | 6.5  | 6.7   | 6.9  | V    |

| VBB UVLO Hysteresis                       | V <sub>BBULOHYS</sub> |                                                                             |      | 500   | _    | mV   |

| VIN Logic Threshold                       | V <sub>INTH</sub>     | V <sub>IN</sub> falling                                                     | _    | 2.5   | _    | V    |

| VIN Logic Hysteresis                      | V <sub>INHYS</sub>    |                                                                             |      | 400   | _    | mV   |

| VIN Pulldown Resistor                     | R <sub>VINPD</sub>    |                                                                             |      | 300   | _    | kΩ   |

| VBB Regulated Boost Voltage               | V <sub>BOOST</sub>    | V <sub>IN</sub> < V <sub>INTH</sub>                                         | 4.3  | 5     | 5.8  | V    |

| VBB Boost Low Threshold                   | V <sub>BBTH</sub>     |                                                                             |      | 1.1   | _    | V    |

| Boost Switching Frequency                 | f <sub>BOOST</sub>    |                                                                             |      | 41    | _    | kHz  |

Continued on next page ...

### ELECTRICAL CHARACTERISTICS <sup>[1]</sup> (continued): Valid at T<sub>J</sub> = 25°C, V<sub>BB</sub> = 5 to 16 V, unless noted otherwise

| Characteristics                            | Symbol              | Test Conditions               | Min. | Тур. | Max. | Unit |

|--------------------------------------------|---------------------|-------------------------------|------|------|------|------|

| LOGIC / IO / I <sup>2</sup> C              |                     |                               |      |      |      |      |

| Logic Input Low Level                      | VIL                 |                               | 0    | -    | 0.8  | V    |

| Logic Input High Level                     | V <sub>IH</sub>     |                               | 2    | -    | 5.5  | V    |

| Logic Input Hysteresis                     | V <sub>HYS</sub>    |                               | 200  | 300  | 600  | mv   |

| Le sie lanut Cument                        |                     | PWM, nBRAKE                   | -10  | <1   | 10   | uA   |

| Logic Input Current                        | I <sub>IN</sub>     | PLBENB, V <sub>IN</sub> = 0 V | -    | 100  | _    | uA   |

| Output Saturation Voltage<br>(FG/RD, nFLT) | V <sub>SAT</sub>    | I = 5 mA                      | -    | _    | 0.3  | V    |

| Output Leakage (FG/RD, nFLT)               | Ι <sub>ο</sub>      | V = 16 V, switch OFF          | -    | -    | 5    | μA   |

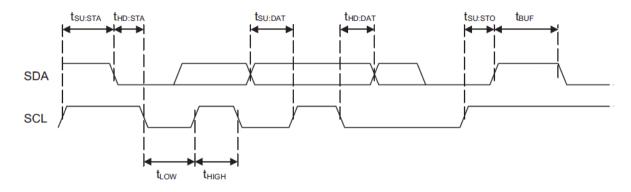

| I <sup>2</sup> C TIMING                    |                     |                               | ·    | ·    |      | ·    |

| SCL Clock Frequency                        | f <sub>CLK</sub>    |                               | 8    | -    | 400  | kHz  |

| Bus Free Time Between Stop/Start           | t <sub>BUF</sub>    |                               | 1.3  | -    | -    | μs   |

| Hold Time Start Condition                  | t <sub>HD:STA</sub> |                               | 0.6  | -    | -    | μs   |

| Setup Time for Start Condition             | t <sub>SU:STA</sub> |                               | 0.6  | -    | _    | μs   |

| SCL Low Time                               | t <sub>LOW</sub>    |                               | 1.3  | -    | _    | μs   |

| SCL High Time                              | t <sub>HIGH</sub>   |                               | 0.6  | -    | _    | μs   |

| Data Setup Time                            | t <sub>SU:DAT</sub> |                               | 100  | -    | -    | ns   |

| Data Hold Time                             | t <sub>HD:DAT</sub> |                               | 0    | -    | 900  | ns   |

| Setup Time for Stop Condition              | t <sub>SU:STO</sub> |                               | 0.6  | -    | -    | ms   |

<sup>[1]</sup> Specified limits are tested at a single temperature and assured over operating temperature range by design and characterization.

## **Three-Phase Sensorless Fan Driver**

## FUNCTIONAL DESCRIPTION

The A89331 targets high-speed fan applications to meet the objectives of minimal vibration, high efficiency, and ability to customize the IC to the speed control specification.

In typical systems, an MCU is required to meet each application specification. The A89331 integrates the basic closed-loop speed control function, thus allowing elimination of the cost, PCB space, and programming requirements of a custom MCU.

For each specific application, the EEPROM settings can be created with the Allegro EVB and software. Contact Allegro sales

to order the custom IC. (Minimum volume requirements will apply).

The speed of the fan is typically controlled by variable duty cycle PWM input. The duty cycle is measured and converted to a 10-bit number. This "demand" is translated to a speed signal based on settings that are configured via EEPROM.

Protection features include lock detection with restart, overcurrent limit, motor output short circuit, supply undervoltage monitor, overvoltage monitor, and thermal shutdown.

Figure 1: Sinusoidal Drive Sequence for DIR = HI

Figure 2: Trapezoidal Drive Sequence for DIR = HI

## **Three-Phase Sensorless Fan Driver**

## FG/RD

Open-drain output, function determined by selection of EEPROM bit FGRD as shown in table below. Additionally, the FG/RD pin serves as the data line (SDA) for I<sup>2</sup>C communication.

| FGRD EEPROM Bit | FG/RD Function |

|-----------------|----------------|

| 0               | FG             |

| 1               | RD Alarm       |

### PWM

Speed demand input. Duty cycle is measured and translated to target speed request. Additionally, the PWM pin serves as the clock line (SCL) for I<sup>2</sup>C communication.

## СТАР

This analog input is an optional connection for motor common (Wye motors). If not used, as in case of delta wound motor, then pin must be left open circuit.

## ROSC

System clock reference. Connect 0.1% 25  $k\Omega$  resistor between ROSC and GND pin.

### nBRAKE

Active low signal turns on all low-sides for braking function. This pin can be used to prevent coast operation during fault conditions. Brake function overrides speed control input. Brake input is ignored during TSD event or if ( $V_{BB} > V_{BBOVLO}$ ) or ( $V_{BB} < V_{BBUVLO}$ ). Care should be taken to avoid exceeding the maximum ratings of the MOSFETs when braking while motor is running. With braking, the current will be limited by  $V_{BEMF}/R_{MOTOR}$ .

## PLBENB

Active high control input to enable power loss brake function. Pin should be connected directly to VBB or GND on PCB. If PLBENB function is disabled, the motor will coast when power is disconnected.

### VIN

Connect to input power supply at connector to the anode of the required power supply blocking diode. This pin will pull down when power supply is disconnected and trigger the power loss function when voltage drops to  $\rm V_{\rm INTH}.\,$  A series resistor is needed for reverse polarity protection.

### **Overvoltage Protection**

The A89331 will disable the motor outputs when the power supply voltage exceeds  $V_{BBOVTH}$ .

### Lock Detect

The A89331 will turn off for the programmed time  $(t_{\rm OFF})$  when the rotor is in a locked condition.

### OCL

An optional overcurrent limit function can be set to four different levels via EEPROM. Current limit must be enabled via EEROM bit OCLD set low. If enabled, then OCL bits in the EEPROM control the level as follows.

| Code | I <sub>OCL</sub> (A) |

|------|----------------------|

| 00   | 3.2                  |

| 01   | 2.6                  |

| 10   | 1.8                  |

| 11   | 1                    |

| OCLOPT | OCLD | Overcurrent Limit Function                                                   |

|--------|------|------------------------------------------------------------------------------|

| 0      | 0    | Source drivers disabled for fixed t <sub>OFF</sub> when threshold is reached |

| 1      | 0    | Applied duty is reduced when<br>overcurrent threshold is reached             |

| Х      | 1    | Disabled                                                                     |

## ОСР

Overcurrent protection is intended to protect the IC from application conditions of shorted load, motor short to ground, and motor short to battery. The OCP protection monitors the drain to source voltage ( $V_{DS}$ ) across any source or sink driver when the output is turned on. If the OCP threshold is exceeded for a short blank time, all drivers are shut off. This fault mode can be reset by PWM OFF/ON cycle or power cycle.

Pin shorts to GND (low inductance) on PCB should be avoided. It is possible during startup that the applied duty can be set below the blank time of the OCP circuit. For this scenario, there can be multiple pulses of high current that may overstress the IC before the OCP shutdown can occur.

### FG/RD

The following signals will bring output nFAULT low:

- VBB Undervoltage

- Thermal Shutdown

- Charge Pump UVLO

- VBB Overvoltage

- Output VDS Fault (OCP)

- Loss of synchronization

The fault output can be connected to Brake pin to allow motor brake mode for particular faults as shown in the table below.

| Fault            | Brake i/p | Fault Action                                                           | Latched | Readback Reg. [Bit] |

|------------------|-----------|------------------------------------------------------------------------|---------|---------------------|

| VBB Undervoltage | Х         | Disable Outputs                                                        | N       | 147[8]              |

| TSD              | Х         | Disable Outputs                                                        | N       | 147[6]              |

| VBB Overvoltage  | Х         | Disable Outputs                                                        | N       | 147[9]              |

| Charge Pump      | Н         | Disable Outputs                                                        | N       | 147[7]              |

|                  | L         | Brake                                                                  | N       |                     |

| VDS Fault        | Н         | Disable outputs, Fault reset by PWM off→on command or VBB Undervoltage | Y       | 147[5:0]            |

|                  | L         | Brake                                                                  | Y       | 147[5:0]            |

| Loss of Sync     | Н         | Set Lock detect timeout – motor coasts                                 | N       | 148[6:0]            |

|                  | L         | Set Lock detect timeout – motor Brake                                  | N       | 148[6:0]            |

## **Charge Pump**

An integrated charge pump provides an above VBB supply to drive the gates of the high-side MOSFETS. Connect 0.1  $\mu$ F / 25 V ceramic capacitors between VCP and VBB and between CP1 and CP2. To prevent negative voltages on CP1 terminal, connect a Schottky diode between GND and CP1 as shown on block diagram.

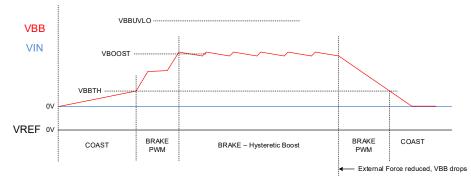

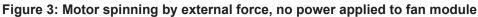

### **Power Loss Brake**

If input power is lost to AMT89331, a brake function can be applied to slow down the motor. With a spinning motor, bemf voltage is generated on motor outputs. This voltage will be rectified by the body diodes on output DMOS devices and the VBB power supply capacitor. If adequate voltage can be stored on VBB capacitor, then the low-side DMOS devices can be turned on to provide braking force to the motor. When the motor slows down, the bemf voltage is reduced. At some point there will not be enough voltage on VBB pin to power the low-side drive, so the braking force will not be applied.

The AMT89331 power loss brake circuitry boosts the voltage on VBB line when motor is spinning by pulsing the motor windings off. If motor is rotating, there will be current in the motor winding during the applied brake. This current can be used to charge up VBB line by pulsing off the brake mode for a short time, similar to hysteretic boost converter operation.

| VIN  | PLBENB | V <sub>BB</sub>                                 | Mode of Operation        | Notes                                                           |

|------|--------|-------------------------------------------------|--------------------------|-----------------------------------------------------------------|

| LOW  | VBB    | < V <sub>BBTH</sub>                             | Coast – No Braking       |                                                                 |

| LOW  | VBB    | > V <sub>BBTH</sub> and<br>< V <sub>BOOST</sub> | BRAKE PWM                | $V_{BB}$ ramps up to $V_{BOOST}$ if motor spinning fast enough. |

| LOW  | VBB    | V <sub>BOOST</sub>                              | BRAKE - hysteretic boost | V <sub>BB</sub> regulated to V <sub>BOOST</sub> .               |

| LOW  | VBB    | > V <sub>BOOST</sub>                            | BRAKE                    | $V_{BB}$ decays depending on IBB2 and $V_{BB}$ capacitance.     |

| HIGH | Х      | < V <sub>BBUVLO</sub>                           | Coast – No Braking       | Power up or power down                                          |

| HIGH | Х      | > V <sub>BBUVLO</sub>                           | Run Mode                 | VREF powers up logic; motor starts if PWM signal valid          |

| LOW  | GND    | Х                                               | Coast – No Braking       | Connect PLBENB to GND to disable power loss brake               |

Note:  $V_{IN} < V_{INTH}$  = LOW,  $V_{IN} > V_{INTH}$  = High

Figure 4: Normal Power Sequence

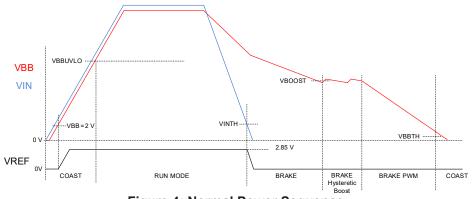

Figure 5: Speed Curve Parameters

### **Speed Curve Parameters (continued)**

Refer to Figure 5 for below items.

#### **Minimum Speed Set Point**

The minimum speed is defined by the value stored in EEPROM variable MINPWM. The resolution is 1 rpm.

MINPWM (RPM) = 0..4095

#### **Maximum Speed Set Point**

The A89331 calculates the maximum speed based on line equation y = mx + B. The maximum speed is defined as the speed with input duty = 100%.

The desired maximum speed is used to set the EEPROM variable PWMSLP.

$PWMSLP = 64 \times (Maximum Speed (rpm) - MINPWM) / 1023$

Example: Max Speed = 25000, Min Speed = 3000.

$PWMSLP = 64 \times 22000 / 1023 = 1376$

where PWMSLP = 0..8192.

Motor Speed (rpm) = Slope  $\times$  DutyIN + MINPWM.

where Slope = PWMSLP  $\times$  1023 / 64 and DutyIN expressed in %.

#### **Duty In Enable Threshold**

EEPROM variable DCON defines the input duty signal that enables the drive. DCON is a 8-bit number with a resolution of 0.2%, which results in a maximum setting of 49.9%.

Duty On (%) =  $100 \times (DCON \times 2) / 1023$

If DCON is set to "0", the motor will turn on with 0% duty cycle input.

#### **Duty In Disable Threshold**

EEPROM variable DCOFF defines the input duty signal that disables the drive. DCOFF is an 8-bit number with resolution of 0.2%, which results in a maximum setting of 49.9%.

Duty Off(%) = DCOFF  $\times 2 / 1023$

DCOFF should always be set to a lower number than DCON.

#### **Duty Cycle Invert**

To create mirror image of speed curve, set duty cycle invert bit to "1".

#### **Minimum Duty Clamp**

Minimum speed can be clamped to a value to allow the motor to run at defined low-level speed. This is achieved by ignoring the duty cycle input if below the programmed MINDTY level.

Min Duty Clamp (%) =  $100 \times MINDTY \times 4 / 1023$

Therefore, the minimum speed will be defined by:

MinSpeedClamp(RPM) = Slope × MinDutyClamp + MINPWM

Setting MINDTY to 0 disables the function.

MINDTY = 0..127

#### **Maximum Duty Clamp**

EEPROM variable DTYMAX defines a duty level at which the motor will change operation from closed-loop curve. The change of operation would depend on MAXDTYOPT setting. If MAXDTYOP = 0, then open-loop operation will result; if MAXDTYOPT = 1, then operation will remain closed loop; however, the speed will be clamped at the value calculated by DTYMAX level.

Four bits are used for this setting at resolution of 1.6% to cover the range 76.5% to 100%.

Maximum Duty (%) =  $100 \times (511 - MAXDTY \times 8) / 511$

MAXDTY = 0..15; If MAXDTY = 0 then function is disabled.

Hysteresis is needed to prevent motor from going back and forth between open- and closed-loop mode.

MAXDTYHYS = 0...15

$Hys(\%) = (MAXDTYHYS + 1) \times 0.4$

#### **RD** Function

Rotor Detect output RD can be used to indicate that the motor is not running as expected. A high level on RD will indicate a fault.

There are two situations for RD fault:

- 1. Motor has lock events, enable into lock, or lock while running. There are two different methods for handling lock events, controlled by setting of EEPROM bit LOCKEVT.

- 2. Motor running at target speed and falls below defined speed thresholds.

A. Rd signals after RD Delay Timer times out.

| Parameter     | Range               | Resolution | Comment                                                                      |

|---------------|---------------------|------------|------------------------------------------------------------------------------|

| LOCKEVT       | 0/1                 |            | 0 = RD triggered at lock event count of 2<br>1 = Use RDBLANK for lock events |

| RD_High (RPM) | 0 to 4080 rpm       | 16 rpm     | If set to 0; RD function disabled                                            |

| RD_Low (RPM)  | 0 to 4080 rpm       | 16 rpm     | Must be programmed lower than RD_high                                        |

| RDDLY         | 0 to 15 seconds     | 1 second   |                                                                              |

| RDBLANK       | 0.1 to 25.4 seconds | 100 ms     |                                                                              |

| T_LOCK_OFF    | 0.1 to 25.4 seconds | 100 ms     |                                                                              |

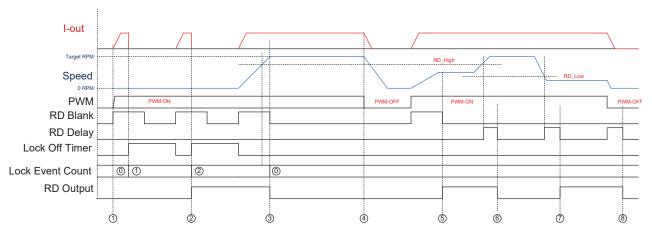

- 1. Power On with Rotor locked condition

- 2. Rd is High after 2nd lock event

- 3. Rd resets Low after RDBLANK if (Speed > RD\_high); Lock Event count reset to Zero

- 4. PWM off RD is low since normal condition

- 5. RD is High after RDBLANK if (Speed < RD\_High)

- 6. Rd is Low if (Speed > RD\_high) after RDDLY

- 7. Rd is High if (Speed < RD\_Low) after RDDLY

- 8. PWM off RD goes low after RDDLY low since normal condition

#### Figure 6: Rd Timing Diagram (LOCKEVT = 0)

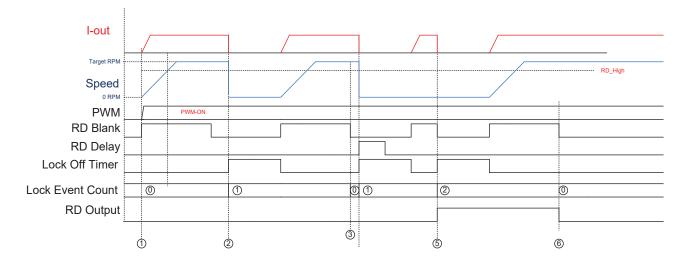

- 1. Power On with PWM normal Startup

- 2. Rotor Locked while running Lock Event counter is One

- 3. If Speed > RD\_high after RDBLANK; Lock Event count reset to Zero

- 4. Rotor Locked while running Lock Event counter is One

- 5. Rd is High after 2nd lock event

- 6. Rd reset to Low after RD BLANK if (Speed > RD\_high); Lock Event count reset to Zero

#### Figure 7: Rd Timing Diagram (LOCKEVT = 0); lock condition while running

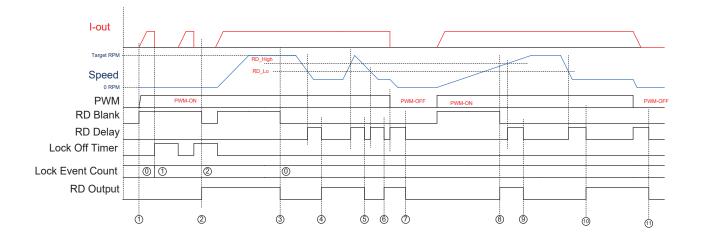

- 1. Power On with Rotor locked condition

- 2. Rd is High after RDBLANK if Speed < RD\_High

- 3. Rd resets Low after RDBLANK if (Speed > RD\_high)

- 4. RD changes to HI if speed < RD\_low after RDDLY

- 5. RD changes to LO if speed > RD\_high after RDDLY

- 6. RD changes to HI if speed < Rd\_low after RDDLY

- 7. RD changes to LO when PWM goes off after RDDLY

- 8. RD changes to HI after RDBLANK is Speed < RD\_high (even if > RD\_low)

- 9. RD changes to LO if speed >R\_high after RDDLY

- 10. RD changes to HI if speed < RD\_low after RDDLY

- 11. RD changes to LO when PWM goes off after RDDLY

Note: RDBlank should be programmed longer than the time it takes to accelerate to the RD\_high level. Startup time + time to accelerate to RD\_high.

#### Figure 8: Rd Timing Diagram (LOCKEVT = 1)

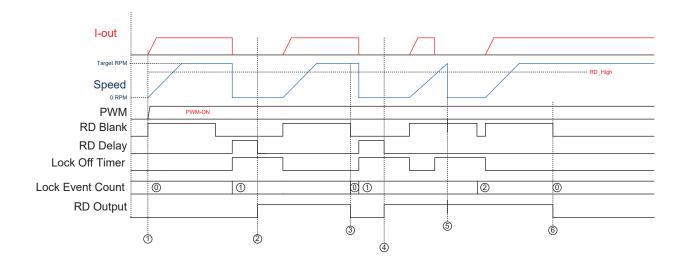

- 1. Power On with PWM normal Startup

- 2. Rotor Locked while running RD changes to HI after RDDLY if Speed < RD\_Low

- 3. RD changes to LO If Speed > RD\_high after RDBLANK

- 4. Rotor Locked while running RD changes to HI after RDDLY if Speed < RD\_Low

- 5. Rd remains HI, even if speed is OK since RDBLANK has not timed out

- 6. Rd reset to Low after RD BLANK if (Speed > RD\_high)

#### Figure 9: Rd Timing Diagram (LOCKEVT = 1) lock condition while running

#### **EEPROM MAP**

Note: refer to application note and user interface for additional detail.

| I <sup>2</sup> C REG | EE ADDR                                        | Bits  | Name      | Description                                                  | Default Setting |  |  |

|----------------------|------------------------------------------------|-------|-----------|--------------------------------------------------------------|-----------------|--|--|

| 64                   | 0                                              | 15:0  | Dev1      | Allegro Reserved                                             | n/a             |  |  |

| 65                   | 1                                              | 15:0  | Dev1      | Allegro Reserved                                             | n/a             |  |  |

| 66                   | 2                                              | 15:0  | Dev1      | Allegro Reserved                                             | n/a             |  |  |

| 67                   | 3                                              | 15:0  | Dev1      | Allegro Reserved                                             | n/a             |  |  |

| 68                   | 4                                              | 15:0  | Dev1      | Allegro Reserved                                             | n/a             |  |  |

|                      |                                                | 0     | DTYIN     | 0 = Low Freq. < 3.2 kHz 1: High > 2.5 kHz                    |                 |  |  |

| <u> </u>             | 69         5         2:1           3         3 |       | REVDMD    | 0 = 1×, 1 = 1.5×, 2 = 2×, 3 = 2.5×                           | 0.0045          |  |  |

| 69                   |                                                |       | FGMSK     | 0 = Disabled, 1 = Enabled                                    | 0x0015          |  |  |

|                      |                                                | 4     | FCOLCHK   | 0 = Enabled, 1 = Disabled                                    |                 |  |  |

| 70                   | 6                                              | 15:0  | Trim1     | Allegro Reserved                                             | n/a             |  |  |

| 71                   | 7                                              | 15:0  | Trim2     | Allegro Reserved                                             | n/a             |  |  |

|                      |                                                | 3:0   | MAXDTYCLP | Range = 100% to 76.5%, LSB = 1.6%                            |                 |  |  |

| 70                   | 0                                              | 7:4   | MAXDTYHYS | Range = 0 to 5.9%, LSB = 0.4%                                | 0.0000          |  |  |

| 72                   | 8                                              | 14:8  | MINDTYCLP | Range = 0 to 49.9%, LSB = 0.78%                              | 0x8000          |  |  |

|                      |                                                | 15    | CL25      | 0: Close loop when > target speed, 1: Close Loop at 25% Duty |                 |  |  |

|                      |                                                | 8:0   | STRTDMD   | LSB = VBBRNG / 511                                           |                 |  |  |

| 73                   | 9                                              | 15:9  | DMDPOST   | Range = 0 to 100%, LSB = 0.8%                                | 0xDC26          |  |  |

|                      |                                                | 7:0   | ALIGNT    | Range = 0 to 20.4 seconds, LSB = 100 ms                      | 0.5500          |  |  |

| 74                   | 74 10                                          |       | ASLOPE    | Range = 160 ms to 40 seconds                                 | 0xFF06          |  |  |

| 75                   | 7:0                                            |       | STRTF     | Range = 0 to 15.94 Hz, LSB = 0.0625 MHz                      | 0,4000          |  |  |

| 75                   | 11                                             | 15:8  | ACCEL     | Range = 0 to 99.6 Hz/s, LSB = 0.78                           | 0xA020          |  |  |

| 76                   | 10                                             | 7:0   | ACCELT    | Range = 0 to 10.2 seconds, LSB = 40 ms                       | 0,000           |  |  |

| 70                   | 12                                             | 15:8  | MAXOFFDTY | Range = 100% to 76.5%, LSB = 0.4%                            | 0x000F          |  |  |

|                      |                                                | 3:0   | DMDRMPAL  | Range = 0.9 to 15.3 ms/count, LSB = 0.9                      |                 |  |  |

| 77                   | 10                                             | 7:4   | DMDRMPAH  | Range = 0.9 to 15.3 ms/count, LSB = 0.9                      | 0.0000          |  |  |

| 77                   | 13                                             | 11:8  | DMDRMPDL  | Range = 0.9 to 15.3 ms/count, LSB = 0.9                      | 0x6669          |  |  |

|                      |                                                | 15:12 | DMDRMPDH  | Range = 0.9 to 15.3 ms/count, LSB = 0.9                      |                 |  |  |

| 70                   | 14                                             | 8:0   | RESDTY    | Range = 0 to 100%, LSB = 0.2%                                | 0,2000          |  |  |

| 78                   | 14                                             |       | RESWID    | Range = 0 to 50%, LSB = 0.4%                                 | 0x0000          |  |  |

| 70                   | 45                                             | 7:0   | MAXSPD    | Maximum Electrical Frequency                                 | 0               |  |  |

| 79                   | 15                                             | 15:8  | TLOCK     | 0 to 25.5 seconds                                            | 0x320C          |  |  |

| 00                   | 40                                             | 7:0   | RDLOW     | Range = 0 to 4095, LSB = 16 rpm                              | 00000           |  |  |

| 80                   | 16                                             | 15:8  | RDHIGH    | Range = 0 to 4095, LSB = 16 rpm                              | 0x0000          |  |  |

|                      |                                                | 7:0   | RDBLK     | Range = 0 to 25.5 seconds, LSB = 100 ms                      |                 |  |  |

| 81                   | 17                                             |       |           | 0x0000                                                       |                 |  |  |

|                      |                                                | 15:12 | RETRY     | Count > 1 = number of lock detect events before disable      |                 |  |  |

| 00                   | 10                                             | 11:0  | PHASLP    | Calculated Slope for Linear Phase Advance                    | 0.5047          |  |  |

| 82                   | 18                                             | 15:12 | SOWLIN    | Window Width With Linear Phase Advance                       | 0xF0A7          |  |  |

Continued on next page ...

#### **EEPROM MAP (continued)**

Note: refer to application note and user interface for additional detail.

| I <sup>2</sup> C REG | EE ADDR | Bits                               | Name      | Description                                                    | Default Setting |  |

|----------------------|---------|------------------------------------|-----------|----------------------------------------------------------------|-----------------|--|

|                      |         | 0                                  | OCLDIS    | 0 = Normal, 1 = Disabled                                       |                 |  |

|                      |         | 1                                  | OCLOPT    | 0 = Cycle by cycle, 1 = Reduce demand                          |                 |  |

|                      |         | 3:2                                | PWMF      | Motor PWM Selection                                            |                 |  |

|                      |         | 5:4                                | BEMFFILT  | Bemf comp filter                                               |                 |  |

| 83                   | 83 19   |                                    | TCENB     | Temperature Compensation, 0 = Off, 1 = On                      | 0xA508          |  |

|                      |         | 8:7                                | WINDM     | Windmill Option                                                |                 |  |

|                      |         | 12:9                               | SPDCLP    | Minimum clamp is speed control mode                            |                 |  |

|                      |         | 14:13                              | PHARNG    | 0 = >32 krpm, 1 = 16 to 32 krpm, 2 = 8 to 16 krpm, 3 = <8 krpm |                 |  |

|                      |         | 15                                 | PCDLY     | Post Coast delay, 0 = 100 ms, 1 = 500 ms                       |                 |  |

|                      |         | 0                                  | CL        | Speed Control Mode, 0 = Open Loop, 1 = Closed                  |                 |  |

|                      |         | 1                                  | PHA       | Running Mode, 0 = Auto, 1 = Linear Phase Advance               |                 |  |

|                      |         | 2                                  | RDOPT     | Rd Function Mode select                                        |                 |  |

|                      |         | 3                                  | FGRD      | Pin Function for FG/RD; 0 = FG, 1 = RD                         |                 |  |

|                      |         | 6:4                                | PP        | Pole Pair = PP + 1                                             |                 |  |

|                      |         | 7                                  | NOCOAST   | 1 = No Coast, 0 = Coast                                        |                 |  |

| 84                   | 20      | 8                                  | ALIGNMODE | 0 = Align, 1 = One Cycle                                       | 0x5111          |  |

|                      |         | 9                                  | QCKSTRT   | 0 = Disable, 1 = Enable                                        |                 |  |

|                      |         | 10                                 | RDPWM     | 0 = No Alarm if PWM off, 1 = Alarm ignores PWM off             |                 |  |

|                      |         | 11                                 | FGSTRT    | 0 = FG disabled during Startup, 1 = FG Enabled                 |                 |  |

|                      |         | 13:12                              | BEMFHYS   | Bemf Hys Level for Startup                                     |                 |  |

|                      |         | 14 SOWAUTO Initial Value of Window |           |                                                                |                 |  |

|                      |         | 15                                 | DIR       | 0 = ACB, 1 = ABC                                               |                 |  |

|                      |         | 7:0                                | KP        | Closed Loop                                                    |                 |  |

| 85                   | 21      | 15:8                               | KI        | Closed Loop                                                    | 0x0210          |  |

|                      |         | 7:0                                | SLPSWDTY  | Duty at which slope changes                                    |                 |  |

| 86                   | 22      | 11:8                               | TRAPSWDTY | Duty to switch to trap                                         | 0x0000          |  |

|                      |         | 15:12                              | PHAOFF    | Offset for Linear Phase Advance                                |                 |  |

| 87                   | 23      | 14:0                               | SLPSWRPM  | Range 0 to 16384, LSB = 1 rpm                                  | 0x0000          |  |

|                      |         | 13:0                               | SPDSLP2   | Calculated Slope                                               |                 |  |

| 88                   | 24      | 15:14                              | Unused    |                                                                | 0x0000          |  |

|                      |         | 0                                  | DUTYINV   | 0 = Normal, 1 = Invert                                         |                 |  |

|                      |         | 1                                  | MAXDTYOPT | 0 = Run at Open Loop, 1 = Run at MAXDTYCLP                     |                 |  |

|                      |         | 2                                  | ONOFFCNTL | 0 = Normal hysteretic on/off, 1 = Off between DC_ON and DC_OFF |                 |  |

|                      |         | 3                                  | PIOPT     | 0 = 1×, 1 = 8×                                                 |                 |  |

| 89                   | 25      | 4                                  | REVOPT    | 1 = reverse when duty < DC_OFF and ONOFFCNTL = 1               | 0x6102          |  |

|                      |         | 6:5                                | OCLLEV    | OCL Level                                                      |                 |  |

|                      |         | 8:7                                | ACOCL     | AC loss OCL level                                              |                 |  |

|                      |         | 12:9                               | DCDISTH   | Threshold for DC disable function                              |                 |  |

|                      |         | 15:13                              | TRAPOL    | Trapezoidal Overlap Control                                    |                 |  |

Continued on next page ...

#### **EEPROM MAP (continued)**

Note: refer to application note and user interface for additional detail.

| I <sup>2</sup> C REG | EE ADDR                             | Bits  | Name      | Description                                                      | Default Setting |  |  |  |

|----------------------|-------------------------------------|-------|-----------|------------------------------------------------------------------|-----------------|--|--|--|

| 90                   | 26                                  | 7:0   | TCOAST    | Coast time for brake or dir change                               | 0xAF1E          |  |  |  |

| 90                   | 20                                  | 15:8  | OPNLPMAX  | Max speed limit for open-loop mode                               | UXAFTE          |  |  |  |

|                      |                                     | 11:0  | MINSPD    | Minimum Speed (y intercept)                                      |                 |  |  |  |

| 91                   | 04 07                               |       | OVPDIS    | 0 = Normal, 1 = Disable                                          | 0x07D0          |  |  |  |

| 91                   | 27                                  | 14:13 | Unused    |                                                                  | 0x07D0          |  |  |  |

|                      |                                     | 15    | BRKOFF    | 0 = Coast, 1 = Brake when PWM off state after t <sub>COAST</sub> |                 |  |  |  |

| 02                   | 92 28 13:0 SPDSLP1<br>15:14 OCLTOFF |       | SPDSLP1   | Calculated Slope of Speed Curve                                  | 0-0450          |  |  |  |

| 92                   |                                     |       | OCLTOFF   | OCL Offtime Select                                               | 0x84E3          |  |  |  |

| 02                   | 93 29 7:0 DCON<br>15:8 DCOFF        |       | DCON      | Range = 0 to 49.9%, LSB = 0.2%                                   | 0x101A          |  |  |  |

| 93                   |                                     |       | DCOFF     | Range = 0 to 49.9% LSB = 0.2%                                    | UXIUIA          |  |  |  |

|                      |                                     | 5:0   | Unused    |                                                                  |                 |  |  |  |

|                      |                                     | 7:6   | BLANK     | Blank Time for OCL                                               |                 |  |  |  |

|                      |                                     | 8     | OCPDIS    | OCP Disable, 0 = Enabled, 1 = Disabled                           |                 |  |  |  |

|                      |                                     | 9     | ACLOSS    | 0 = Disable, 1 = Enable                                          |                 |  |  |  |

| 94                   | 30                                  | 11:10 | ACLOSSREL | Duty at which ACLOSS OCL function is released                    | 0x004A          |  |  |  |

|                      |                                     | 12    | ACLOSSOCL | 0 = Disable, 1 = Enable                                          |                 |  |  |  |

|                      |                                     | 13    | FCOLOPT   | Wait before Data Output                                          |                 |  |  |  |

|                      |                                     | 14    | FCOLCOAST | 0 = Normal Drive, 1 = Disable motor during Data output           |                 |  |  |  |

|                      |                                     | 15    | FCOLENB   | 0 = Disable, 1 = Enable                                          |                 |  |  |  |

| 95                   | 31                                  | 15:0  | Trim3     | Allegro Reserve                                                  | n/a             |  |  |  |

| n/a                  | 32-63                               | 15:0  | USER      | User-defined Memory                                              | 0x0000          |  |  |  |

### **Serial Port Control Option**

Normally, the IC is controlled by duty cycle input and uses the EEPROM data that is stored to create the speed curve profile. However, it is possible to use direct serial port control to avoid programming EEPROM.

When using direct control, the input duty cycle command is replaced by writing to a 10-bit number to register 165.

Example:

REGADDR[data]: (in decimal)

$165[1023] \rightarrow \text{Duty}=100\%$

$165[102] \rightarrow \text{Duty}=102/1023=10\%$

Upon power-up, the IC defaults to duty cycle input mode. To use serial port mode, the internal registers should be programmed before turning the part on. The sequence to use serial port mode is:

- 1. Drive FG and PWM pins low\*\*

- 2. Power up IC

- 3. Program registers for parameter setting that correspond to each of the EEPROM memory locations.

- A. REGADDR = 64 + EEPROM ADDR.

- B. Program register addresses 65 to 84 corresponding to EEPROM addresses 1 to 20.

- C. It may be helpful to use the GUI text file to help define the hex data for each of the EEPROM addresses.

- 4. Write to register 165 to start motor.

\*\*Note: If PWM is not driven low before power-up, the motor will try to start immediately as the default high value will demand 100% on signal.

## **Three-Phase Sensorless Fan Driver**

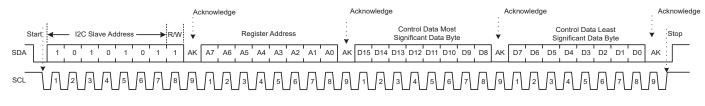

### **Serial Port**

The A89331 uses standard fast mode I<sup>2</sup>C serial port format to program the EEPROM or to control the IC speed serially. The PWM pin functions as the clock (SCL) input, and the FG pin is the data line (SDA). No special sequence is needed to begin transferring data. If the motor is running, the FG may pull the data line low while trying to initialize into serial port mode. Once an I<sup>2</sup>C command is sent, the PWM input is ignored, and the motor will turn off as if a PWM duty command of 0% was sent.

The A89331 7-bit slave address is 0x55.

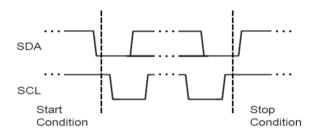

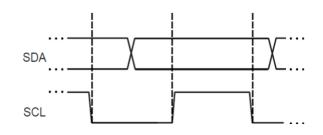

## I<sup>2</sup>C Timing Diagrams

Figure 10: Start and Stop Conditions

#### Figure 11: Clock and data bit synchronization

Figure 12: I<sup>2</sup>C-Compatible Timing Requirements

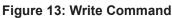

### Write Command

- 1. Start Condition

- 2. 7-bit I<sup>2</sup>C Slave Address (Device ID) 1010101, R/W Bit = 0

- 3. Internal Register Address

- 4. 2 data bytes, MSB first

- 5. Stop Condition

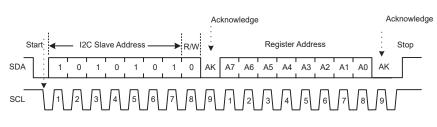

## Read Command: Two-Step Process

- 1. Start Condition

- 2. 7-bit I<sup>2</sup>C Slave Address (Device ID) 1010101, R/W Bit = 0

- 3. Internal Register Address to be read

- 4. Stop Condition

- 5. Start Condition

- 6. 7-bit I<sup>2</sup>C Slave Address (Device ID) 1010101, R/W Bit = 1

- 7. Read 2 data bytes

- 8. Stop Condition

### Figure 14: Read Command

### **Programming EEPROM**

The A89331 contains 63 words of 16-bit length. The EEPROM is controlled with the following I<sup>2</sup>C registers. Refer to application note for EEPROM definition.

| EEPROM Control - Register 161: Used to control | ol programming of EEPROM |

|------------------------------------------------|--------------------------|

|------------------------------------------------|--------------------------|

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|---|---|---|---|---|---|----|----|----|----|

| 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | RD | WR | ER | EN |

| Bit  | Name | Description                                               |

|------|------|-----------------------------------------------------------|

| 0    | EN   | Set EEPROM Voltage required for Writing or Erasing        |

| 1    | ER   | Sets Mode to Erase                                        |

| 2    | WR   | Sets Mode to Write                                        |

| 3    | RD   | Sets Mode to Read                                         |

| 15:4 | n/a  | Do not use, always set to zero during programming process |

EEPROM Address – Register 162: Used to set the EEPROM address to be altered

| [ | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2       | 1  | 0 |

|---|----|----|----|----|----|----|---|---|---|---|---|---|---|---------|----|---|

|   | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 |   |   | eADDRES | 50 |   |

| Bit  | Name Description |                                                                                                                                     |  |  |  |  |  |

|------|------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0    | eeADDRESS        | Used to specify EEPROM address to be changed. There are 20 addresses. Do not change address 0 or 19 as these are factory controlled |  |  |  |  |  |

| 15:5 | n/a              | Do not use always set to zero during programming process                                                                            |  |  |  |  |  |

EEPROM DataIn - Register 163: Used to set the EEPROM new data to be programmed

| 15 | 14       | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    | eeDATAin |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Bit  | Name     | Description                                       |

|------|----------|---------------------------------------------------|

| 15:0 | eeDATAin | Used to specify the new EEPROM data to be changed |

#### EEPROM DataOUT - Register 164: Used for read operations

| 15 | 14        | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|-----------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    | eeDATAout |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| [ | Bit  | Name      | Description                                                       |

|---|------|-----------|-------------------------------------------------------------------|

|   | 15:0 | eeDATAout | Used to readback EEPROM data from address defined in register 162 |

## **Three-Phase Sensorless Fan Driver**

There are 3 basic commands, Read, Erase, and Write. To change the contents of a memory location, the word must be first erased. The EEPROM programming process (writing or erasing) takes 12 ms per word.

Each word must be written individually.

Example #1: Write EEPROM address 5 to 261 (hex = 0x0105).

| Erase the word<br>I <sup>2</sup> C Write REGADDR[Data] | ; comment                                                                                                                                                                                                                     |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A. 162[5]                                              | ; set EEPROM address to erase                                                                                                                                                                                                 |

| B. 163[0]                                              | ; set 0000 as Data In                                                                                                                                                                                                         |

| C. 161[3]                                              | ; set control to Erase and Voltage High                                                                                                                                                                                       |

| D. Wait 12 ms                                          | ; requires 12 ms High Voltage Pulse to Write                                                                                                                                                                                  |

| Write the new data                                     |                                                                                                                                                                                                                               |

| A. 162[5]                                              | ; set EEPROM address to write                                                                                                                                                                                                 |

| B. 163[261]                                            | ; set Data In = 261                                                                                                                                                                                                           |

| C. 161[5]                                              | ; set control to Write and Set Voltage High                                                                                                                                                                                   |

| D. Wait 12 ms                                          | ; requires 12 ms High Voltage Pulse to Write                                                                                                                                                                                  |

|                                                        | <ul> <li>I<sup>2</sup>C Write REGADDR[Data]</li> <li>A. 162[5]</li> <li>B. 163[0]</li> <li>C. 161[3]</li> <li>D. Wait 12 ms</li> <li>Write the new data</li> <li>A. 162[5]</li> <li>B. 163[261]</li> <li>C. 161[5]</li> </ul> |

Example #2: Read address 5 to confirm correct data properly programmed.

- 1. Read the word

- A. 5[i2c read]

; read register 5; this will be contents of EEPROM

## **APPLICATION INFORMATION**

| Name                                | Suggested   | Comment                                                                                 |  |  |

|-------------------------------------|-------------|-----------------------------------------------------------------------------------------|--|--|

| C <sub>VREF</sub> 0.22 μF / X5R / 2 |             | Ceramic capacitor required                                                              |  |  |

| C <sub>VBB</sub> 22 to 220 μF       |             | Power Supply Stabilization – electrolytic or ceramic                                    |  |  |

|                                     |             | Pull-up resistor to VREF                                                                |  |  |

| C <sub>VCP</sub>                    | 0.1 µF      | Ceramic capacitor required                                                              |  |  |

| C <sub>CP</sub>                     | 0.1 µF      | Ceramic capacitor required                                                              |  |  |

| D1                                  | B24013F     | Required to isolate motor for reverse polarity protection and power loss brake function |  |  |

| D2                                  | PMEG3002AEL | Schottky diode, V <sub>f</sub> < 500 mV @ 100 mA                                        |  |  |

| ZD1                                 | SMBJ14A     | TVS to limit max $V_{BB}$ due to transients due to motor generation on power line       |  |  |

| R <sub>FG</sub> , R <sub>PWM</sub>  | 500 Ω       | Isolate IC pin from noise or overvoltage transients or protect from connector issues    |  |  |

| R1                                  | 10 kΩ       | Required for reverse polarity protection VIN pin                                        |  |  |

| R2                                  | 10 kΩ       | Pulldown for VIN                                                                        |  |  |

| C <sub>VIN</sub> 0.1 µF             |             | Noise filter for hot swap events                                                        |  |  |

Layout Notes

1. Add thermal vias to exposed pad area.

2. Add ground plane on top and bottom of PCB.

3. Place  $C_{VREF}$  and  $C_{VBB}$  as close as possible to IC, connected to GND plane.

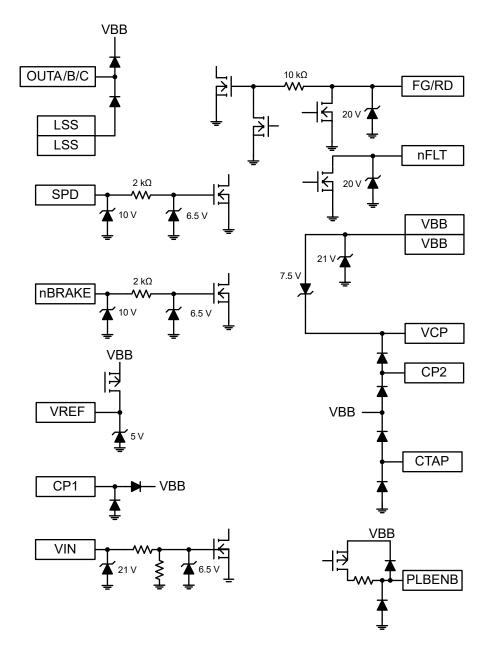

**PIN DIAGRAMS**

## PACKAGE OUTLINE DRAWINGS

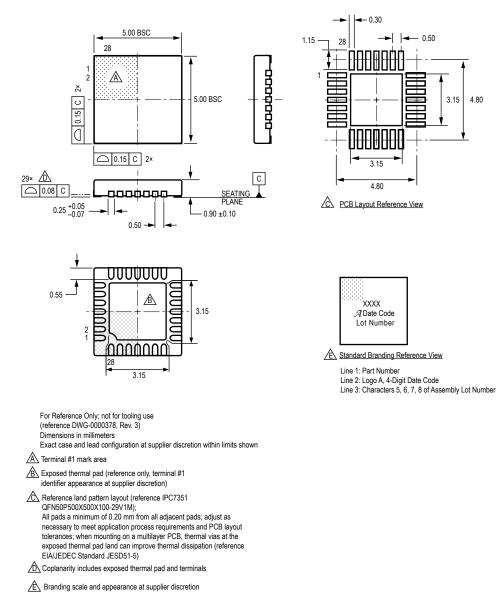

Figure 15: ET Package, 28-Pin QFN with Exposed Pad

## **Three-Phase Sensorless Fan Driver**

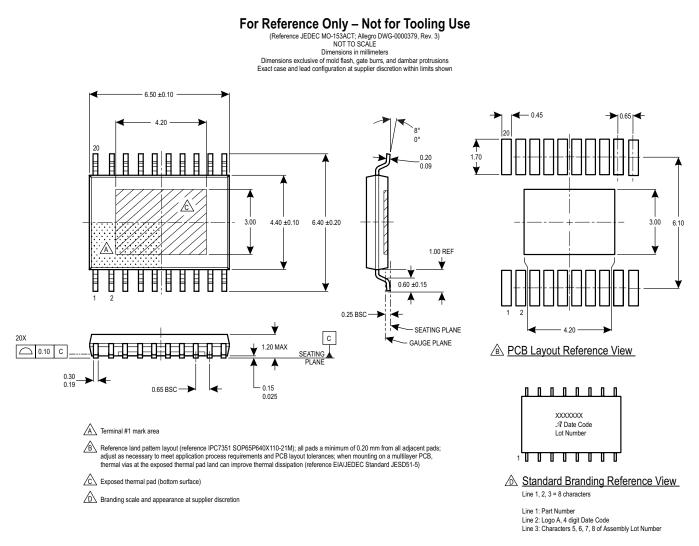

Figure 16: LP Package, 20-Pin TSSOP with Exposed Pad

## **Three-Phase Sensorless Fan Driver**

#### **Revision History**

| Number | Date         | Description                                                                         |  |  |  |

|--------|--------------|-------------------------------------------------------------------------------------|--|--|--|

| _      | May 20, 2020 | Initial release                                                                     |  |  |  |

| 1      | June 8, 2022 | Updated package drawings (pages 26-27) and A89331GETSR packing information (page 2) |  |  |  |

Copyright 2022, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com