### FEATURES AND BENEFITS

- 90 V maximum rating with integrated buck regulator for high efficiency

- Fully integrated single-shunt sensorless FOC controller (code-free)

- Speed, torque, and power mode operation

- Power-loss brake functionality

- Universal speed curve

- Fault mode brake

- Analog/PWM/Clock mode speed control

- Precision speed control

- Configurable RD or FG output

- Slew-rate control for electromagnetic-interference (EMI) mitigation

- Proprietary nonreverse fast startup

- Ultra-quiet low-speed operation

- Current-control soft start

- Windmill startup operation

- No  $V_{BB}$  boost on powerup with spinning motor

- I<sup>2</sup>C serial port

- Power limit protection

- · Configurable current and power limit

- Lock detection

- Overcurrent limit (OCL)

- Overvoltage protection (OVP)

- Short-circuit protection (OCP)

- Logic input compatible with 3.3 V and 5 V  $\,$

### DESCRIPTION

The A89333 is a three-phase, sensorless, brushless DC (BLDC) motor controller. A field-oriented control (FOC) algorithm is fully integrated to achieve the best efficiency and acoustic noise performance. The device also optimizes motor-startup performance in stationary, forward, and reverse windmill conditions.

Programmable profiles and closed-loop controls are included for constant power and constant speed operations. This eliminates the requirement for a microprocessor-based system and minimizes programming requirements.

A simple inter-integrated circuit (I<sup>2</sup>C) interface is provided for setting motor-related parameters, control-related parameters, and startup profiles, which are stored in nonvolatile memory (NVM). The I<sup>2</sup>C interface can also be used to control the motor directly and to provide speed and status feedback. Password protection is available for stored NVM data.

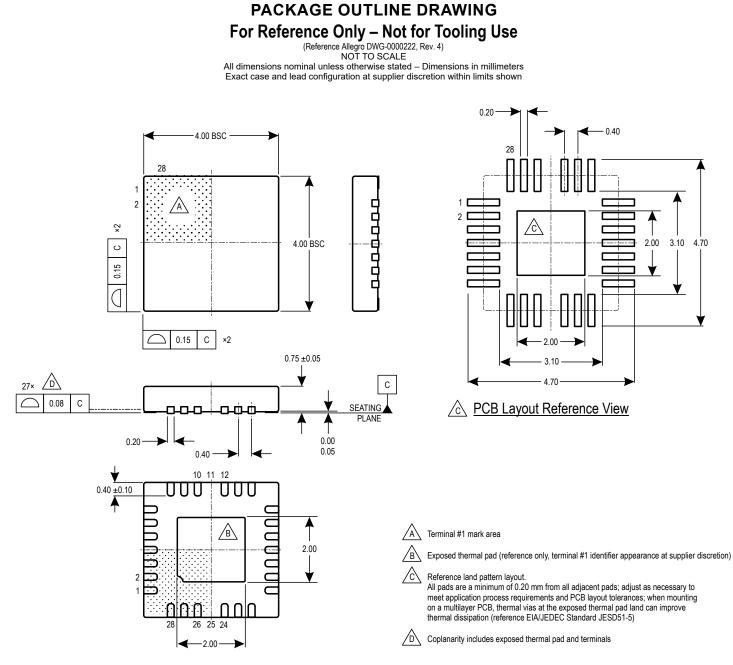

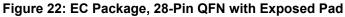

The A89333 is available in a 28-contact 4 mm  $\times$  4 mm quad-flat no-leads (QFN) package with exposed thermal pad (suffix EC).

### APPLICATIONS

- 48 V server fans

- Telecommunications (telecom) fans

- Home appliance fans

#### PACKAGE

28-Contact QFN with exposed pad (EC package)

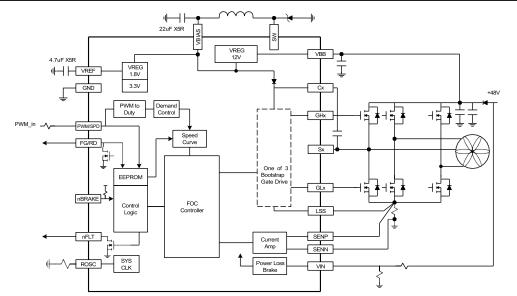

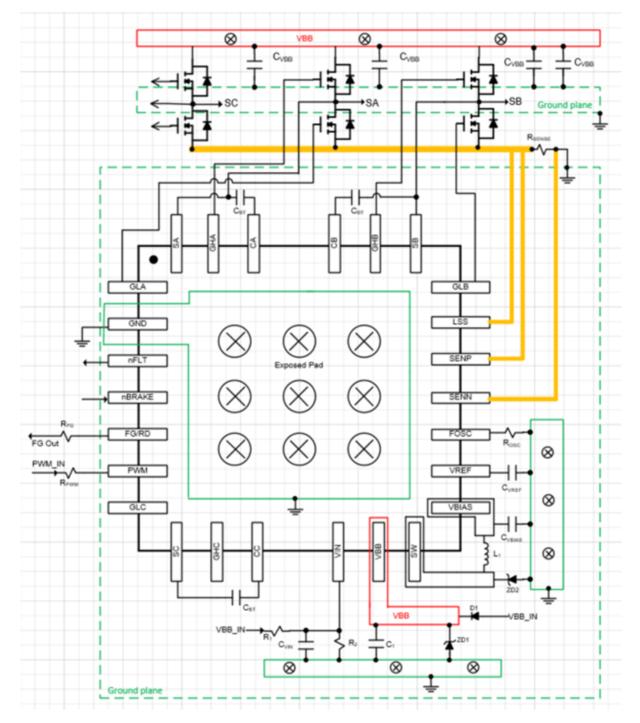

Figure 1: Typical Application

### 48 V Sensorless Code-Free FOC BLDC Motor Controller

### TABLE OF CONTENTS

| Specifications                                             |    |

|------------------------------------------------------------|----|

| Pinout Diagram and Terminal List Table                     | 4  |

| Pin Descriptions                                           | 8  |

| VBB                                                        | 8  |

| VREF                                                       | 8  |

| VBIAS                                                      | 8  |

| SW                                                         | 8  |

| FG/RD                                                      | 8  |

| PWM/SPD                                                    |    |

| ROSC                                                       |    |

| Sx                                                         | 8  |

| Сх                                                         |    |

| GHx                                                        |    |

| GLx                                                        | 8  |

| LSS                                                        |    |

| SENN                                                       |    |

| SENP                                                       |    |

| nBRAKE                                                     |    |

| nFLT                                                       |    |

| Functional Description                                     |    |

| Powerup and Initialization                                 |    |

| External Command Source                                    | 11 |

| Analog Input Voltage (EXT CMD SRC, 0x1).                   | 11 |

| PWM Duty Cycle (EXT_CMD_SRC, 0x2)                          |    |

| Frequency Mode (EXT_CMD_SRC, 0x3)                          |    |

| I <sup>2</sup> C Mode (EXT_CMD_SRC, 0x0)                   | 12 |

| Universal Curve Controller: UCC                            | 13 |

| Motor Rotation Direction                                   |    |

| Speed, Torque, or Power Control Modes                      |    |

| Torque Mode (0x2)                                          |    |

| Power Mode (0x1)                                           |    |

| Maximum System Speed                                       |    |

| Maximum System Current and Bus Current Sensing             |    |

| DC-Link Voltage                                            | 16 |

| Maximum Electrical Power                                   |    |

| Speed Limit                                                |    |

| Power Limit                                                |    |

| Motor Control Application (MCA) Finite State Machine (FSM) | 16 |

| Standby—SBY                                                |    |

| Windmilling—WNDML                                          |    |

| IPD and Align                                              |    |

| Ramp-Up—RAMPUP                                             |    |

| Drive—DRIVE                                                |    |

| Regenerative Mode                                          |    |

| Brake—BRAKE                                                |    |

| FOC Algorithm Speed and Current Loop                       | 19 |

| Observer                                                   |    |

|                                                            |    |

| Diagnostic and Protection Features               |    |

|--------------------------------------------------|----|

| VBB Undervoltage—VBB UVS                         |    |

| VBB, UV, and NVM Reprogramming                   | 21 |

| Over-Temperature Protection—OVT/TSD              | 22 |

| VBB Overvoltage Protection—VBB OVP               | 22 |

| Overcurrent Protection—OCP (Short Protection)    | 22 |

| Loss of Sync (Lock/Stall Detection)              |    |

| No-Motor Start                                   | 23 |

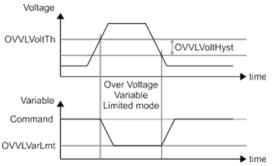

| VBB Overvoltage Variable Limiter                 | 23 |

| Overcurrent Limit                                | 24 |

| Maximum Power Limit                              |    |

| Application Features                             | 25 |

| EEPROM NVM for Storing Motor Control             |    |

| and Configuration Data                           | 25 |

| FG/RD Pin                                        | 25 |

| FG                                               | 25 |

| RD                                               |    |

| FG in VBB UV Condition                           |    |

| FG ID Pattern Generation                         |    |

| Dead Time Configuration                          | 27 |

| Slew Rate Control                                |    |

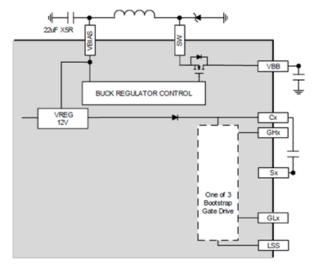

| Buck Converter                                   | 27 |

| Advanced Features                                |    |

| BEMF Compensation                                |    |

| Soft-Off Deceleration                            |    |

| Soft Start                                       |    |

| Quiet Start                                      |    |

| Forced OL                                        |    |

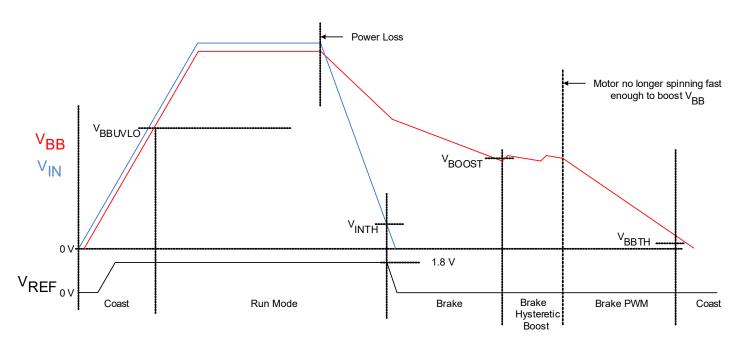

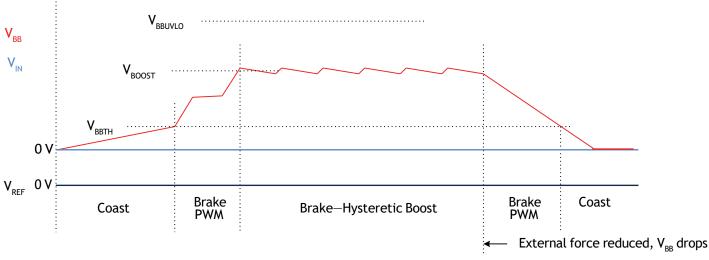

| VIN and Power-Loss Brake                         |    |

| No-Power Brake                                   | 30 |

| Registers and Nonvolatile Memory (NVM) Map       | 31 |

| User Registers                                   | 41 |

| SW Status Register, SW_STATUS                    |    |

| I <sup>2</sup> C Command Register, REF_CMD       | 43 |

| SW Fixed-Address Variables                       |    |

| FOC Internal Variables                           | 45 |

| Programming the EEPROM                           | 46 |

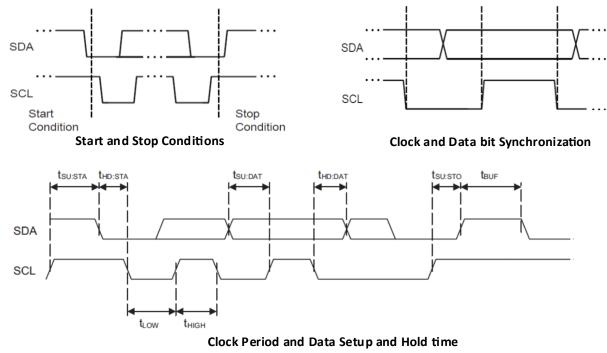

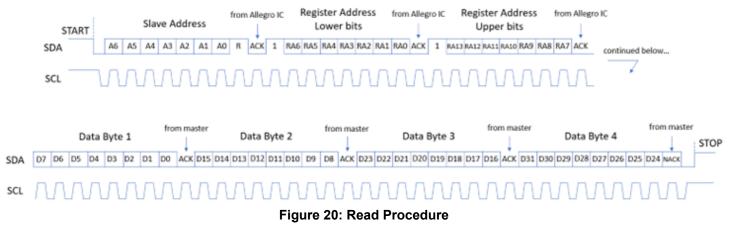

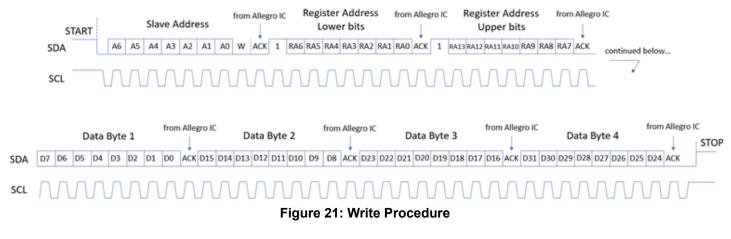

| I <sup>2</sup> C Serial Interface                | 46 |

| I <sup>2</sup> C Timing Diagrams                 | 46 |

| Read Procedure                                   |    |

| Write Procedure                                  | 47 |

| Operation Modes and Customer Password Protection |    |

| Application Information                          |    |

| Layout Notes                                     |    |

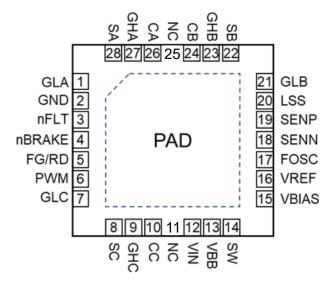

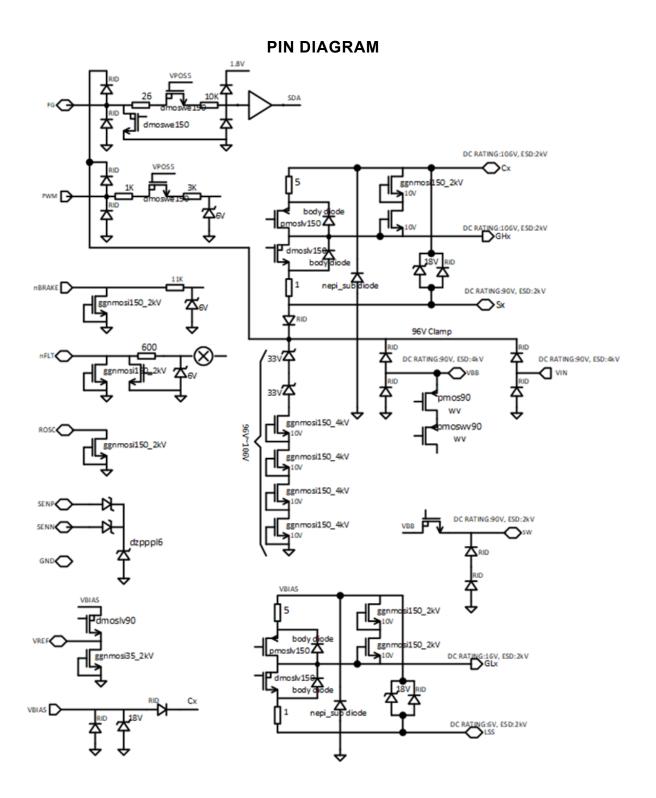

| Pin Diagram                                      |    |

| Package Outline Drawing                          | 52 |

#### SPECIFICATIONS

#### **SELECTION GUIDE**

| Part Number | Package                                          | Packing                      |

|-------------|--------------------------------------------------|------------------------------|

| A89333GECSR | 28-lead 4 mm × 4 mm QFN with exposed thermal pad | 6000 pieces per 13-inch reel |

#### ABSOLUTE MAXIMUM RATINGS [1][2]

| Parameter                             | Symbol           | Conditions              | Rating                              | Units |

|---------------------------------------|------------------|-------------------------|-------------------------------------|-------|

| Supply Voltage                        | V <sub>BB</sub>  | V <sub>BB</sub> = 90 V  | -0.3 to 90                          | V     |

| Power Loss Brake Terminal             | VI               | V <sub>IN</sub>         | -0.3 to 90                          | V     |

| Speed Control Terminal                | V <sub>I</sub>   | PWM/SPD                 | -0.3 to 90                          | V     |

| Logic Input Terminal                  | VI               | nBRAKE                  | -0.3 to 6                           | V     |

| Logic Bidirectional Terminal          | V <sub>IO</sub>  | FG/RD                   | -0.3 to 90                          | V     |

| Logic Output Terminal                 | Vo               | nFLT                    | -0.3 to 6                           | V     |

| Durch Quittals Transitional           |                  |                         | -1 to 90                            | V     |

| Buck Switch Terminal                  | V <sub>SW</sub>  | t <sub>W</sub> < 0.5 μs | -4 to 90                            | V     |

| Bootstrap Supply Terminals            | V <sub>CX</sub>  | CA, CB, CC              | -0.3 to V <sub>BIAS</sub> + 90      | V     |

| Motor-Phase Terminals                 | V <sub>SX</sub>  | SA, SB, SC              | $V_{CX} - 4$ to $V_{CX} + 0.3$      | V     |

| High-Side Gate Drive Output Terminals | V <sub>GHX</sub> | GHA, GHB, GHC           | $V_{SX} - 0.3$ to $V_{CX} + 0.3$    | V     |

| Low-Side Gate Drive Output Terminals  | V <sub>GLX</sub> | GLA, GLB, GLC           | $V_{LSS} - 0.3$ to $V_{BIAS} + 0.3$ | V     |

| Input Terminal                        | V <sub>I</sub>   | ROSC                    | -0.3 to 6                           | V     |

| Output Terminal                       | Vo               | VBIAS                   | –0.3 to 15                          | V     |

| Output Terminal                       | Vo               | VREF                    | -0.3 to 3.4                         | V     |

| Input Terminal                        | VI               | SENP, SENN              | -4 to 6                             | V     |

|                                       |                  |                         | -500 to 500                         | mV    |

| Bridge Low-Side Source Terminals      | V <sub>LSS</sub> | t <sub>w</sub> < 200 ns | -4 to 6                             | V     |

| Junction Temperature                  | Tj               |                         | 150                                 | °C    |

| Storage Temperature Range             | T <sub>s</sub>   |                         | -55 to 150                          | °C    |

<sup>[1]</sup> With respect to GND, unless otherwise noted. Ratings apply when no other circuit operating constraints are present.

<sup>[2]</sup> Lowercase "x" in terminal names and symbols indicates a variable sequence character.

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information.

| Characteristic                                   | Symbol                | Test Conditions [1]                                                       |    | Unit |

|--------------------------------------------------|-----------------------|---------------------------------------------------------------------------|----|------|

| Package Thermal Resistance (Junction to Ambient) | R <sub>θJA</sub>      | 28-contact QFN (package EC), on 2-sided PCB with 1 in <sup>2</sup> copper | 45 | °C/W |

| Package Thermal Resistance<br>(Junction to Pad)  | $R_{	extsf{	heta}JP}$ |                                                                           | 2  | °C/W |

<sup>[1]</sup> Additional thermal information is available on the Allegro website.

#### **RECOMMENDED OPERATIONAL RANGE**

| Characteristics             | Symbol          | Test Conditions | Min. | Тур. | Max. | Units |

|-----------------------------|-----------------|-----------------|------|------|------|-------|

| Power Supply Voltage        | V <sub>BB</sub> | DC              | 7    | 48   | 75   | V     |

| Logic Voltage Range         | V <sub>I</sub>  | nBRAKE          | -0.3 | -    | 5.5  | V     |

| Operating Temperature Range | T <sub>a</sub>  |                 | -40  | -    | 105  | °C    |

## 48 V Sensorless Code-Free FOC BLDC Motor Controller

#### **PINOUT DIAGRAM AND TERMINAL LIST TABLE**

EC Package (Top View)

#### **Terminal List Table**

| Number | Name    | Function                                            |

|--------|---------|-----------------------------------------------------|

| 1      | GLA     | Gate drive output                                   |

| 2      | GND     | Ground                                              |

| 3      | nFLT    | Logic output                                        |

| 4      | nBRAKE  | Logic input                                         |

| 5      | FG/RD   | Logic output; also used as SDA for I <sup>2</sup> C |

| 6      | PWM/SPD | Logic input; also used as SCK for I <sup>2</sup> C  |

| 7      | GLC     | Gate drive output                                   |

| 8      | SC      | Motor output                                        |

| 9      | GHC     | Gate drive output                                   |

| 10     | CC      | C <sub>BOOTSTRAP</sub>                              |

| 11     | NC      | No connection                                       |

| 12     | VIN     | Analog input                                        |

| 13     | VBB     | Power supply input                                  |

| 14     | SW      | Switch node                                         |

| Number | Name  | Function                        |

|--------|-------|---------------------------------|

| 15     | VBIAS | Voltage regulator output        |

| 16     | VREF  | Logic supply output             |

| 17     | ROSC  | Analog input                    |

| 18     | SENN  | Current sense negative terminal |

| 19     | SENP  | Current sense positive terminal |

| 20     | LSS   | Low-side source                 |

| 21     | GLB   | Gate drive output               |

| 22     | SB    | Motor output                    |

| 23     | GHB   | Gate drive output               |

| 24     | СВ    | C <sub>BOOTSTRAP</sub>          |

| 25     | NC    | No connection                   |

| 26     | CA    | C <sub>BOOTSTRAP</sub>          |

| 27     | GHA   | Gate drive output               |

| 28     | SA    | Motor output                    |

## 48 V Sensorless Code-Free FOC BLDC Motor Controller

| Characteristics             | Symbol               | Test Conditions                                                                      | Min.  | Тур. | Max. | Units |

|-----------------------------|----------------------|--------------------------------------------------------------------------------------|-------|------|------|-------|

| Power Supply Voltage        | V <sub>BB</sub>      | V <sub>BB</sub> = 90 V                                                               | 7 [2] | 48   | 90   | V     |

| VPP Cumply Cumpat           | I <sub>BB1</sub>     | Standby, V <sub>IN</sub> > V <sub>INTH</sub> , V <sub>BB</sub> > V <sub>BBUVLO</sub> | -     | 6    | -    | mA    |

| VBB Supply Current          | I <sub>BB2</sub>     | V <sub>IN</sub> < V <sub>INTH</sub>                                                  | -     | 0.8  | 3.3  | mA    |

| VBIAS Output Voltage        | V <sub>BIAS</sub>    | V <sub>BB</sub> > 13 V, I <sub>EXT_LOAD</sub> < 10 mA                                | 10    | 12.5 | 14   | V     |

| VREF                        | V <sub>REF</sub>     | $I_{EXT\_LOAD} < 5mA$                                                                | 1.7   | 1.8  | 1.9  | V     |

| VREF Current Limit          | V <sub>REFOCL</sub>  | V <sub>REF</sub> = 0 V, internal current limit                                       | 70    | 92   | 135  | mA    |

| GATE DRIVER                 |                      |                                                                                      |       |      |      |       |

| High-Side Gate Drive Output | V <sub>GH</sub>      | V <sub>BB</sub> = 48 V, DC                                                           | 9.3   | 11.8 | 13.3 | V     |

| Low-Side Gate Drive Output  | V <sub>GL</sub>      | V <sub>BB</sub> = 48 V, DC                                                           | 10    | 12.5 | 14   | V     |

|                             |                      | PWMGDSLEWRATE = 0, DC, V <sub>GS_TH</sub> = 3 V                                      | 7     | 8.5  | 10   | mA    |

| Cata Daiva Caura Currant    | Y                    | PWMGDSLEWRATE = 1, DC, V <sub>GS_TH</sub> = 3 V                                      | 19    | 25.5 | 32   | mA    |

| Gate Drive Source Current   | I <sub>SRC</sub>     | PWMGDSLEWRATE = 2, DC, $V_{GS_{TH}}$ = 3 V                                           | 31    | 42   | 53   | mA    |

|                             |                      | PWMGDSLEWRATE = 3, DC, V <sub>GS_TH</sub> = 3 V                                      | 48    | 63   | 78   | mA    |

|                             |                      | PWMGDSLEWRATE = 0, DC, V <sub>GS_TH</sub> = 3 V                                      | 16    | 23   | 30   | mA    |

| Gate Drive Sink Current     | Y                    | PWMGDSLEWRATE = 1, DC, V <sub>GS_TH</sub> = 3 V                                      | 33    | 46   | 60   | mA    |

|                             | I <sub>SNK</sub>     | PWMGDSLEWRATE = 2, DC, V <sub>GS_TH</sub> = 3 V                                      | 50    | 68   | 87   | mA    |

|                             |                      | PWMGDSLEWRATE = 3, DC, V <sub>GS_TH</sub> = 3 V                                      | 50    | 68   | 87   | mA    |

| GHx Passive Pull-Down       | R <sub>GHPD</sub>    | V <sub>BB</sub> = 0, V <sub>GHx</sub> – V <sub>Sx</sub> < 0.1 V                      | 0.5   | -    | 2    | MΩ    |

| GLx Passive Pull-Down       | R <sub>GLPD</sub>    | $V_{BB} = 0, V_{GLx} - V_{LSS} < 0.1 V$                                              | 0.5   | -    | 2    | MΩ    |

| PROTECTION CIRCUITS         |                      |                                                                                      |       |      |      |       |

| Lock Protection             | t <sub>OFF</sub>     | Relative to programmed target,<br>ROTSTARTRETRYTOUT                                  | -10   | _    | 10   | %     |

| Overcurrent Limit           | I <sub>OCL</sub>     | Relative to programmed target,<br>SFOCDRVCURRLMT                                     | -15   | _    | 15   | %     |

| Thermal Shutdown Temp.      | T <sub>JTSD</sub>    | Temperature increasing                                                               | 145   | 160  | 175  | °C    |

| Thermal Shutdown Hysteresis | $\Delta T_{J}$       | Recovery = $T_{JTSD} - \Delta T_J$                                                   | _     | 20   | _    | °C    |

| VREF UVLO                   | V <sub>REFUVLO</sub> | V <sub>BIAS</sub> rising                                                             | 1.35  | 1.45 | 1.55 | V     |

| VBB Overvoltage             | V <sub>BBOVTH</sub>  | Relative to programmed target, OVP_TH                                                | -3    | -    | 3    | %     |

|                             |                      | V <sub>BB</sub> rising, UVSTH = 0                                                    | 29    | 30   | 32   | V     |

| VBB UVLO                    | V <sub>BBUVLO</sub>  | V <sub>BB</sub> rising, UVSTH = 1                                                    | 23    | 24   | 25   | V     |

|                             |                      | V <sub>BB</sub> rising, UVSTH = 2                                                    | 6.2   | 6.7  | 7.5  | V     |

### **ELECTRICAL CHARACTERISTICS** <sup>[1]</sup>: Valid at $T_J = 25^{\circ}C$ , $V_{BB} = 48$ V (unless noted otherwise)

<sup>[1]</sup> Specified limits are tested at a single temperature and assured over operating temperature range by design and characterization. <sup>[2]</sup> When  $V_{BB} < 13 \text{ V}$ , gate drive output voltage tracks  $V_{BB}$  voltage.

### 48 V Sensorless Code-Free FOC BLDC Motor Controller

| Characteristics                            | Symbol              | Test Conditions                     | Min. | Тур. | Max. | Units |

|--------------------------------------------|---------------------|-------------------------------------|------|------|------|-------|

| POWER LOSS BRAKE                           |                     |                                     | •    |      |      |       |

| V <sub>IN</sub> Logic Threshold            | V <sub>INTH</sub>   | V <sub>IN</sub> falling             | -    | 2.7  | _    | V     |

| Hysteresis                                 | VINHYS              |                                     | -    | 500  | _    | mV    |

| V <sub>IN</sub> Pull-Down Resistor         | V <sub>INPD</sub>   |                                     | _    | 870  | -    | kΩ    |

| V <sub>BB</sub> Regulated Boost Voltage    | V <sub>BOOST</sub>  | V <sub>IN</sub> < V <sub>INTH</sub> | 7.4  | 8.1  | 8.9  | V     |

| V <sub>BB</sub> Boost Low Threshold        | V <sub>BBTH</sub>   |                                     | -    | 1.1  | -    | V     |

| Boost Switching Frequency                  | f <sub>BOOST</sub>  |                                     | _    | 40   | -    | kHz   |

| LOGIC INPUTS AND OUTPUT                    |                     |                                     |      |      |      |       |

| Logic Input Low Level                      | V <sub>IL</sub>     | nBRAKE                              | 0    | -    | 0.8  | V     |

| Logic Input High Level                     | V <sub>IH</sub>     | nBRAKE                              | 2    | -    | 6    | V     |

| Logic Input Hysteresis                     | V <sub>HYS</sub>    | nBRAKE                              | 200  | 300  | 600  | mV    |

| Logic Input Current                        | I <sub>IN</sub>     | SPD, nBRAKE                         | -10  | < 1  | 15   | μA    |

| Output Saturation Voltage<br>(FG/RD, nFLT) | V <sub>SAT</sub>    | I = 1 mA                            | -    | _    | 0.3  | V     |

| Output Leakage (FG/RD)                     | Ι <sub>Ο</sub>      | V = 12 V, switch OFF                | -    | -    | 5    | μA    |

| Output Leakage (nFLT)                      | Ι <sub>Ο</sub>      | V = 6 V, switch OFF                 | -    | -    | 10   | μA    |

| INTERNAL OPEN-DRAIN PUL                    | L-UP                |                                     |      |      |      |       |

|                                            |                     | FG/RD                               | 10   | 12.5 | 14   | V     |

| Internal Pull-Up Voltage                   |                     | nFLT, nBRAKE                        | 4.25 | 5    | 5.75 | V     |

|                                            |                     | PWM/SPD                             | 3.75 | 4    | 4.25 | V     |

| Internal Pull-Up Resistor                  |                     | FG/RD                               | 12   | 20   | 28   | kΩ    |

| internal Full-Op Resistor                  |                     | PWM/SPD, nFLT, nBRAKE               | 60   | 100  | 140  | kΩ    |

| I <sup>2</sup> C TIMING                    |                     |                                     |      |      |      |       |

| SCL Clock Frequency                        | f <sub>CLK</sub>    |                                     | 10   | -    | 400  | kHz   |

| Bus Free Time Between Stop/<br>Start       | t <sub>BUF</sub>    |                                     | 1.3  | -    | -    | μs    |

| Hold Time Start Condition                  | t <sub>HD:STA</sub> |                                     | 0.6  | -    | -    | μs    |

| Setup Time for Start Condition             | t <sub>SU:STA</sub> |                                     | 0.6  | -    | _    | μs    |

| SCL Low Time                               | t <sub>LOW</sub>    |                                     | 1.3  | -    | _    | μs    |

| SCL High Time                              | t <sub>HIGH</sub>   |                                     | 0.6  | _    | -    | μs    |

| Data Setup Time                            | t <sub>SU:DAT</sub> |                                     | 100  | -    | -    | ns    |

| Data Hold Time                             | t <sub>HD:DAT</sub> |                                     | 0    | -    | 900  | ns    |

| Setup Time for Stop Condition              | t <sub>su:sto</sub> |                                     | 0.6  | _    | _    | ms    |

#### **ELECTRICAL CHARACTERISTICS (cont.)** <sup>[1]</sup>: Valid at T<sub>J</sub> = 25°C, V<sub>BB</sub> = 48 V (unless noted otherwise)

#### ELECTRICAL CHARACTERISTICS (cont.) <sup>[1]</sup>: Valid at T<sub>J</sub> = 25°C, V<sub>BB</sub> = 48 V (unless noted otherwise)

| Characteristics                                                                                  | Symbol                | Test Conditions                           | Min. | Тур. | Max. | Units |

|--------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------|------|------|------|-------|

| SPEED CONTROL                                                                                    |                       |                                           |      |      |      |       |

| PWM Duty Input, for PWM<br>Duty Control Mode                                                     | f <sub>PWM</sub>      |                                           | 0.1  | _    | 100  | kHz   |

| Duty Cycle On Threshold                                                                          | DC <sub>ON</sub>      | Relative to programmed target             | -0.5 | _    | 0.5  | %     |

| Duty Cycle Off Threshold                                                                         | DC <sub>OFF</sub>     | Relative to programmed target             | -0.5 | _    | 0.5  | %     |

| Analog SPD Full-Range<br>Voltage, for Analog External<br>Command Source (Analog<br>Control Mode) | AnaSpd <sub>MAX</sub> | I <sub>LOAD</sub> = 10 μA                 | 0    | _    | 3.6  | V     |

| Analog SPD Resolution                                                                            |                       |                                           | -    | 1    | _    | mV    |

| Input Clock Frequency Range<br>(Clock Mode)                                                      |                       | Relative to programmed target, CLKCOMPREF | 0.1  | _    | 1    | kHz   |

| Speed Setpoint (Digital, Not<br>Clock Mode)                                                      | F <sub>SPD</sub>      | R <sub>OSC</sub> = 25 kΩ (0.1%)           | -2.5 | _    | 2.5  | %     |

| Speed Setpoint (Digital, Clock<br>Mode)                                                          | F <sub>SPDClk</sub>   | PWM input frequency = CLKCOMPREF ±0.05%   | -0.1 | _    | 0.1  | %     |

| System Oscillator                                                                                | f <sub>OSC</sub>      | R <sub>OSC</sub> = 25 kΩ (0.1%)           | 24.5 | 25   | 25.5 | MHz   |

| ID CLOCK TIMING                                                                                  |                       | •                                         |      |      |      |       |

| Maximum ID Clock Time                                                                            | t <sub>idmax</sub>    | Relative to programmed target, FGIDDUR    | -10% | _    | 10%  | s     |

| ID Clock Frequency                                                                               | f <sub>idclk</sub>    | Relative to programmed target, FGIDFREQ   | -5%  | _    | 5%   | Hz    |

| V <sub>BB</sub> UVLO to ID Clock Delay                                                           | t <sub>dly1</sub>     | Relative to programmed target, FGIDFREQ   | -    | _    | 5%   | s     |

| PWM Rising Edge to End of ID Clock                                                               | t <sub>dly2</sub>     | Relative to programmed target, FGIDFREQ   | -    | _    | 5%   | s     |

| NONVOLATILE MEMORY (NV                                                                           | M) PROGRAM            | MING                                      |      |      |      |       |

| Minimum V <sub>BB</sub> for Programming                                                          | V <sub>NVM_Prog</sub> | V <sub>BB</sub>                           | 25   | _    | _    | V     |

#### PIN DESCRIPTIONS

#### VBB

Main power supply for internal regulators. Tie the VBB pin to the GND pin using a low-equivalent series resistor (ESR) ceramic bypass capacitor of 0.1  $\mu$ F. This capacitor should be situated as close as possible to the VBB pin with a thick trace.

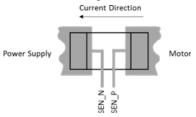

#### VIN

The VIN input is used to sense the supply voltage for the powerloss braking (PLB) function. The PLB function becomes active if the voltage on this input reduces to less than  $V_{INTH}$ . VIN must be connected to the power supply on the anode side of the blocking diode shown in Figure 1.

#### VREF

Voltage reference (1.8 V) to power internal digital logic. A low-ESR ceramic capacitor with 4.7  $\mu$ F or greater is required on the pin to stabilize the supply. This regulator can supply up to 5 mA externally.

#### VBIAS

Internal buck regulator output. Connected to external inductor and output capacitor. VBIAS provides supply current for gate drive, digital logic, bootstrap capacitors, and low-voltage analog circuitry. Up to 10 mA can be externally sourced from the VBIAS pin.

### SW

Buck regulator switching node connected to inductor and rectifier diode.

### FG/RD

FG/RD is an open-drain output that can be pulled up to VBB externally. It also has by default an internal pullup to 12V that can be disabled through IPUP\_FGRD\_DIS parameter in NVM. The selection of function is programmed via NVM parameters as well to provide either speed (FG) or rotation detection (RD) data. For more information, refer to the FG/RD Pin Section.

The FG/RD pin is also used as a serial data (SDA) port in the  $I^2\mathrm{C}$  mode.

The I<sup>2</sup>C command can pass only when this pin is high (open drain).

### PWM/SPD

Device control demand input. Supports analog, PWM, or frequency command.

It also has, by default, an internal pullup to 4 V that can be disabled through IPUP\_PWMSPD\_DIS NVM parameter. The PWM/SPD pin is also used as SCK in the I<sup>2</sup>C mode.

#### ROSC

The ROSC terminal is used to improve the accuracy of the internal system clock for better accuracy control of motor speed. To use this feature, connection of a 0.1% 25 k $\Omega$  resistor between the ROSC terminal and GND is recommended. A 1% resistor can be used for applications where speed control accuracy is not critical.

#### Sx

Load phase connections. These terminals are the negative supply connections for the floating high-side drivers and are also connected to the negative side of the bootstrap capacitors.

### Сх

High-side connections for the bootstrap capacitors and positive supply for high-side gate drivers.

#### GHx

High-side, gate-drive outputs for external N-channel MOSFETs.

#### GLx

Low-side, gate-drive outputs for external N-channel MOSFETs.

#### LSS

Low-side return path for discharge of the capacitance on the MOSFET gates, connected to the common sources of the low-side external MOSFETs through a low-impedance track.

#### SENN

Current sense negative terminal.

#### SENP

Current sense positive terminal.

#### nBRAKE

This is the active low-input signal. It turns on all low sides for the braking function. The brake function overrides input control. Brake input is ignored during a thermal shutdown (TSD) event or

if (V<sub>BB</sub> > V<sub>OVP\_TH</sub>) or (V<sub>BB</sub> < V<sub>BBUVLO</sub>). Care should be taken to avoid stressing the MOSFET when braking while the motor is running. When braking, the current is limited only by V<sub>BEMF</sub>/ R<sub>MOTOR</sub>. The A89333 includes an optional feature that delays braking until the motor speed reduces to a level that is sufficiently low (configurable BRAKE\_FREQ\_TOO\_HIGH\_TH parameter in NVM) that the braking current does not damage the MOSFET.

The nBRAKE pin also has, by default, an internal pull-up to 5 V that can be disabled through the IPUP\_NBRAKE\_DIS parameter in NVM.

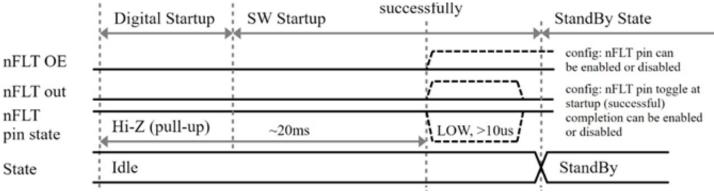

#### nFLT

This open-drain output provides the fault status of the motor operation.

This pin is internally pulled up to 5 V by default. Pull-up can be disabled through NVM. The default is high when there is no fault. When a fault is detected, the nFLT pin transitions to low and remains active (low) until the fault is cleared according to the latched or not-latched mechanism.

The nFLT fault reporting function is enabled by default, but it can be disabled by selecting NFLT\_DIS = 1 in the NVM.

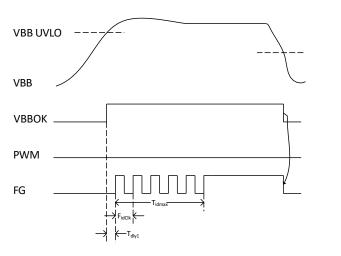

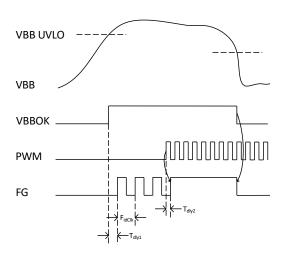

The nFLT feature can be used to indicate a successful software startup after POR by being low for a short period of time as detailed in Figure 2.

This feature can be enabled/disabled in the CONFIG register of the NVM using NFLT\_STARTUP\_DIS.

Figure 2: nFLT Pin at Startup

## 48 V Sensorless Code-Free FOC BLDC Motor Controller

### FUNCTIONAL DESCRIPTION

The A89333 integrates a sensorless FOC algorithm using singleshunt resistance. The FOC algorithm implements a feedback current loop to control the current during dynamic load conditions, guaranteeing minimum torque ripple and maximum efficiency. The integrated buck converter allows it to operate from maximum  $V_{BB}$  with high efficiency and better thermal performance. The A89333 requires minimal external components thanks to the use of the single-shunt technique for current sensing and its advanced algorithm to reconstruct the current of each phase.

Allegro proprietary algorithms have been used to achieve high efficiency, fast start-up, and high dynamic response, minimizing acoustic noise in an easy-to use device.

The A89333 can be controlled through PWM, analog, or I<sup>2</sup>C, depending on the application, with an easy interface to the most common microcontroller.

The motor can be controlled in speed, torque, or power mode, with the FOC algorithm maintaining regulation in the presence of load and supply voltage change. The A89333 integrates advanced diagnostics to detect the internal/external power stage and motor faults. Faults are reported through a dedicated fault pin and the detailed diagnostic status of faults are available through the I<sup>2</sup>C register.

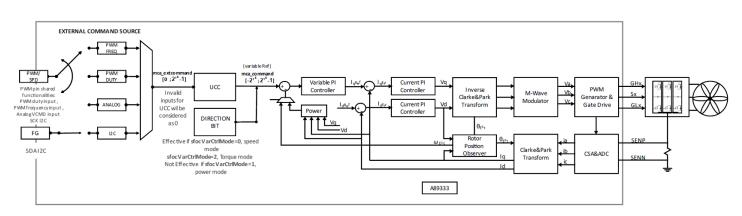

An internal nonvolatile memory (NVM) allows configuration of the motor parameters and the FOC algorithm. The basic FOC control algorithm of A89333 is shown in Figure 3.

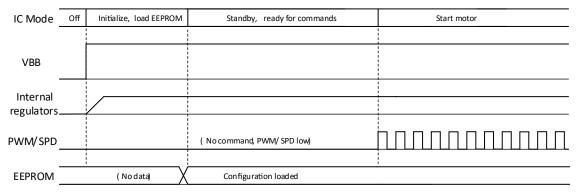

#### **Powerup and Initialization**

Upon power-up, the A89333 waits for the internal regulators to reach their UVLO levels, then loads the configuration data from the NVM into the internal registers. After the configuration is loaded, the A89333 is in the standby mode and is ready to respond to user input through the PWM/SPD pin or the I<sup>2</sup>C port, according to the external command source selected. (For more information, refer to the External Command Source section.)

Figure 3: External Command Source and FOC Algorithm

#### **External Command Source**

The A89333 can be controlled with five different sources of command according to the EXT\_CMD\_SRC in the NVM register setting.

#### ANALOG INPUT VOLTAGE (EXT\_CMD\_SRC, 0X1).

Motor command is proportional to the analog voltage applied on the PWM/SPD pin.

Direction data, when available, is defined in the NVM and the UCC. For further information, refer to the Motor Rotation Direction section.

The analog command is converted into the digital domain and is rescaled according to:

Equation 1:

$$mca_{extcommand} = (2^{15} - 1) \times \frac{V_{PWM/SPD}}{AnaSpdMax}$$

where AnaSpd<sub>Max</sub> is a fixed voltage equal to 3.6 V. For example, see Table 1.

#### PWM DUTY CYCLE (EXT\_CMD\_SRC, 0X2)

Motor control is proportional to the duty cycle applied on the PWM/SPD pin. The frequency range of the input PWM is from 100 Hz to 100 kHz.

Direction data, when available, is defined in the NVM and the UCC. For further information, refer to the Motor Rotation Direction section.

The duty cycle command is converted into the digital domain according to:

Equation 2:

$$mca_{extcommand} = (2^{15} - 1) \times duty$$

.

For example, see Table 2.

In this mode, it is possible to enable the clock mode feature to synchronize the internal clock with the external PWM signal frequency. This can provide higher speed accuracy and can eliminate the need for a precision external resistor on the ROSC terminal. The external PWM signal is used to compensate for the inaccuracy of the integrated oscillator, allowing speed accuracy to be achieved down to 0.1%. When this feature is activated (CLK\_COMP\_ENABLE), the input admissible frequencies of the external PWM signal are fixed and need to be specified in the CLK\_COMP\_REF register. To detect the frequency, the input duty cycle of the PWM signal must be greater than 0% and less than 99%. If a 0% or 100% duty cycle value is applied, the clock compensation is not applied. Speed accuracy is directly related to the accuracy of the PWM clock frequency to the selected CLK\_COMP\_REF frequency.

#### Table 1: Conversion from Analog Input Voltage to Digital Command

| duty <sub>PWM/SPD</sub> (V) | mca <sub>extcommand</sub> (LSB)<br>AnaSpd <sub>Max</sub> = 3.6 V |

|-----------------------------|------------------------------------------------------------------|

| 0.5                         | 4551                                                             |

| 2.5                         | 22755                                                            |

| 3.6                         | 32767                                                            |

#### Table 2: Conversion from PWM Input Duty to Digital Command

| duty <sub>PWM/SPD</sub> (%) | mca <sub>extcommand</sub> (LSB) |

|-----------------------------|---------------------------------|

| 25                          | 8192                            |

| 50                          | 16384                           |

| 75                          | 24575                           |

#### FREQUENCY MODE (EXT\_CMD\_SRC, 0X3)

Motor control is proportional to the frequency applied on the PWM/SPD pin. The input frequency range needs to be between 44.5 and 2666 Hz (duty cycle is intended to be 50%, but this mode works with any setting other than 0 or 100%).

If PWM input frequency is greater than 2666 Hz, MCA\_EX\_ COMMAND assumes the maximum value equal to 32767 [LSB]. If PWM input frequency is less than 44.5 Hz, MCA\_EXT\_COM-MAND is equal to 0.

Direction data, when available, is defined in the NVM and the UCC. For further information, refer to the Motor Rotation Direction section.

The frequency command is converted into the digital domain according to:

Equation 3:

$mca_{extcommand} = (pwm_{freq}[Hz] - 44.5) \times map_{coefficient}$

where  $map_{coefficient}$  is a scaling factor equal to 12.496. For example, see Table 3.

#### Table 3: Conversion from PWM Input Duty to Digital Command

| frequency <sub>PWM/SPD</sub> (Hz) | mca <sub>extcommand</sub> (LSB) |  |  |  |  |  |

|-----------------------------------|---------------------------------|--|--|--|--|--|

| 44.5                              | 0                               |  |  |  |  |  |

| 100                               | (100 – 44.5) × 12.496 = 694     |  |  |  |  |  |

| 200                               | (200 – 44.5) × 12.496 = 1943    |  |  |  |  |  |

| 2666                              | (2666 – 44.5) × 12.496 = 32758  |  |  |  |  |  |

#### I<sup>2</sup>C MODE (EXT\_CMD\_SRC, 0X0)

The motor control speed reference command is defined by writing in the REF\_CMD register through I<sup>2</sup>C protocol. The I<sup>2</sup>C clock, SCK, is mapped on the PWM/SPD pin, and I<sup>2</sup>C data is mapped on the FG pin. In this mode, the motor electrical frequency can be read through the register, as well as many other internal parameters.

The value selected in REF\_CMD is copied into MCA\_EXT\_COMMAND. Direction data, when available, is defined in the NVM and UCC.

The A89333 can load a predefined command into the MCA\_EXT\_COMMAND register at power-up (POR) to start the motor without the need for an external command. The default command can be set in DEFAULT\_EXT\_CMD in the NVM and, at power-up, its value is copied into the MCA\_EXT\_COMMAND register. To disable this feature, DEFAULT\_EXT\_CMD must be set to 0.

The command is treated as speed, power, or torque, depending on the mode selected.

When FG is in the high state (not driven) or when the device has been configured in analog, PWM, or frequency external command source, I<sup>2</sup>C communication is always available.

I<sup>2</sup>C data is mapped on the FG pin and, because the pin is an open drain, it can be controlled by the I<sup>2</sup>C when in the high state. The internal NVM register, shadow NVM register, and status register can therefore be read and set during typical operation. However, for reliable communication, use of I<sup>2</sup>C is recommended when the A89333 is in the standby state (motor stopped).

NOTE 1: The internal NVM register and the shadow NVM register are inaccessible in application operation mode. They can be accessed only in user operation mode or in test operation mode. For more information, refer to the Operation Modes and Customer Password Protection section.

NOTE 2: The I<sup>2</sup>C SCK signal on the PWM/SPD pin is interpreted to be the maximum command. This is because, during serial transactions, the pin state is high, which is a valid command that is therefore interpreted as the maximum command.

For reliable communication, it is better to use serial communication in the UV mode to prevent issues related to motor start and proper FG/RD pin state.

For more information, refer to the VBB, UV, and NVM Reprogramming section.

### **Universal Curve Controller: UCC**

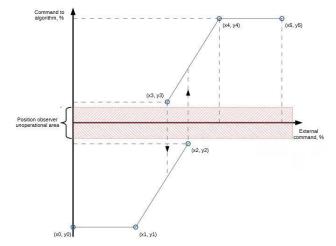

The MCA\_EXT\_COMMAND motor command is passed through a universal curve controller to create an arbitrary command profile, then to the FOC algorithm. The input of the UCC is unsigned(MCA\_EXT\_COMMAND [LSB]) and the output is signed(MCA\_EXT\_COMMAND [LSB]), as shown in Figure 4.

The UCC is a transformer curve defined by corner points. Each point has a specific input value and corresponding output value. Values between points are calculated using linear interpolation. Up to 10 corner points can be defined in NVM (UCC\_X0 to UCC\_Y9). Corner points do not all require definition—only as many as are needed for the desired curve.

A closed-loop nonoperational region, defined by the PO\_OPER parameter in the NVM, marked in the red hatched rectangular area in Figure 4, defines the minimum speed operation for reliable position-observer estimation and proper FOC functionality. Because operation in this area is not reliable, programming the UCC in this area is not recommended. The easiest way to prevent operation in this area is to use hysteresis, as shown in Figure 4.

Some examples of demand curves using screenshots taken from the GUI application follow.

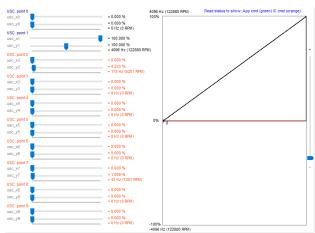

Example 1: The default setting in which the output (Y axis) is same as the input (X axis) is shown in Figure 5. This curve can be used if the transformer is not needed.

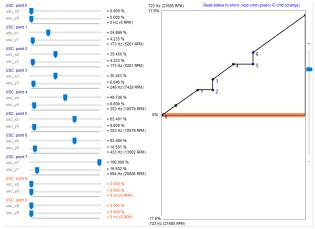

Example 2: When the control loop is set to closed-loop speed, the example shown in Figure 6 can be used to avoid the resonant frequency of the motor, if needed.

Example 3: Hysteresis can be implemented by setting the input value of an address lower than the input value in the previous address. In this example shown in Figure 7, as the input demand rises, the output demand jumps to the next higher level at the vertical lines on the right of each transition. When the input demand falls, the output demand drops to the next lower level following the vertical lines on the left of each transition. This prevents output jitter when the input is around a boundary.

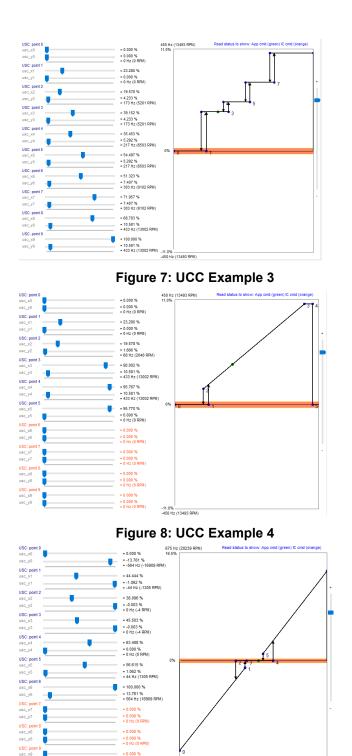

Example 4: In this example shown in Figure 8, the motor does not turn on until the input is approximately 23% and does not turn off until the output falls below about 20%. When the input is between about 90% to 96%, the output is at 10.6% (13002 rpm); when the input is greater than 96%, the motor stops.

Example 5: The curve can be used when bidirectional operation is required. In this case, when input is at 0%, the motor is at the selected maximum speed in the reverse direction; when the input is at 100%, the motor is at the maximum speed in the forward direction; and the motor is stopped when the input is approximately 50%. See Figure 9.

Figure 6: UCC Example 2

## 48 V Sensorless Code-Free FOC BLDC Motor Controller

#### **Motor Rotation Direction**

Information about direction is decoupled from MCA\_COMMAND. As shown in Figure 3, the FOC algorithm has two inputs: direction and command.

The direction of the motor depends on:

- Direction bit in the REF\_CMD register, REF\_CMD[16]

- MSB of MCA\_COMMAND, MCA\_COMMAND[16]:

- □ If the Y values of the UCC are all positive, then MCA\_COMMAND[16] = 0; otherwise, MCA\_COMMAND[16] = 1

- ROT\_DIR\_INVERT configurable NVM parameter

- Operation control mode (speed, power, torque mode, selected according to SFOC\_VAR\_CTRL\_MODE).

In speed control mode, motor direction is defined by:

Motor direction = MCA\_COMMAND[16] XOR ROT\_DIR\_INVERT XOR REF\_CMD[16]

In torque and power control mode, motor direction is defined by:

- Motor direction= ROTDIRINVERT XOR REF CMD[16]

- For torque and power control mode, ensure MCA\_COMMAND[16] is 0 by setting Y values to all positive values.

Figure 9: UCC Example 5

= 0.000 % = 0 Hz (0 R

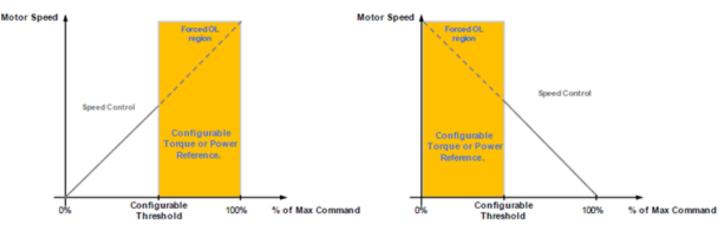

#### Speed, Torque, or Power Control Modes

A89333 includes a control loop able to support three operational modes for motor control: speed, torque, and power. The control variable can be selected with the SFOC\_VAR\_CTRL\_MODE NVM register setting.

#### Speed Mode (0x0)

In speed mode, MCA\_COMMAND is used as a reference for the FOC speed loop to regulate the motor speed to  $f_{ref}$  [Hz].

MCA\_COMMAND is scaled to the maximum frequency [Hz] according to the following formula:

Equation 4:

$$f_{ref}[W] = mca_{command}[LSB] \times \frac{f_{max}}{2^{15} - 1} \frac{[Hz]}{[LSB]}$$

#### Torque Mode (0x2)

In torque mode, MCA\_COMMAND is used as reference for the FOC current loop to regulate the motor torque proportional to  $I_{ref}$  [A].

In this mode, the FOC speed loop is bypassed and the reference command is compared directly with estimated q axis current, Iq<sub>ref</sub>.

MCA\_COMMAND is scaled to the maximum system current [A] according to:

Equation 5:

$$I_{ref}[W] = mca_{command}[LSB] \times \frac{i_{max}}{2^{15} - 1} \frac{[A]}{[LSB]}.$$

In torque control mode, MCA\_COMMAND is downscaled to the current fraction length (11 bits). For this reason, the FOC algorithm command changes only if the external command varies for more than 16 units.

#### Power Mode (0x1)

In power mode, MCA\_COMMAND is used as a reference for the FOC power loop to regulate the motor power to  $P_{ref}$  [W].

MCA\_COMMAND is scaled to the maximum system power [W] according to:

Equation 6:

$$P_{ref}[W] = mca_{command}[LSB] \times \frac{P_{max}}{2^{15} - 1} \frac{[W]}{[LSB]}$$

In power control mode, the command is down-scaled to the voltage fraction length (14 bits) and, for that reason, the FOC algorithm command changes only if the external command varies for more than 2 units.

#### Maximum System Speed

The maximum system speed ( $f_{max}$  [Hz]) is the maximum electrical motor speed that can be commanded. It depends on frequency resolution,  $f_{res}$ , according to:

Equation 7:

$$f_{max} = round(2^{15} \times f_{res})$$

where  $f_{res}$  [Hz/LSB] is the frequency resolution, set through the SFOC\_FREQ\_RES register according to:

Equation 8:

$$f_{res} = \frac{1}{9 \times 2^{sfocFreqRes}} \frac{[Hz]}{[LSB]}.$$

NOTE: The maximum rotation speed can be limited by supply voltage ( $V_{BB}$ ); therefore, high command speed may not result in high motor rotation due to low  $V_{BB}$  voltage.

# Maximum System Current and Bus Current Sensing

The maximum system current is typically set to 110% of the motor-rated current.

A single shunt resistor connecting between SENN and SENP is used to measure the bus current for the FOC algorithm and current limit. The resistor value is typically approximately tens of milliohms, depending on the maximum rated current of the system and the selected gain of the current sense amplifier.

Equation 9:

$$i_{max}[A] = \frac{ADC_{VREF}}{R_{shunt} \times CSA_{GAIN}}$$

where ADC<sub>VREF</sub> is the reference ADC voltage equal to 1.2 V,  $R_{shunt}$  [ $\Omega$ ] is the board shunt resistance, and CSA<sub>GAIN</sub> is the sense amplifier gain that can be set in the SFOC\_CSA\_GAIN NVM parameter to 10 V/V or 20 V/V.

Use of a Kelvin sensing connection is recommended when using the shunt resistor, as shown in Figure 10.

### **DC-Link Voltage**

To enable proper controller operation, set the nominal DC-link voltage in the VBB\_NOM NVM parameter according to:

Equation 10:

$$VBB_{nom} = round \left(\frac{VBB_{nom}[V]}{0.515625}\right),$$

where  $VBB_{nom}$  [V] is the nominal DC-link voltage and 0.515625 [V] is the scaling factor.

NOTE: Proper functioning of the A89333 requires that the nominal VBB used to power the device is correctly configured in the VBB\_NOM NVM.

### **Maximum Electrical Power**

The maximum electrical power value [W] is calculated using: Equation 11:

$$Pmax[W] = \frac{3}{2}i_{max}1.1547 \frac{VBB_{nom}[V]}{2}.$$

For example, with maximum system current,  $\rm I_{Max}$ , of 6.25 A and  $\rm VBB_{nom}$  of 12 V, the maximum electrical power is 64.95 W.

#### SPEED LIMIT

The SFOC\_FREQ\_LMT NVM parameter limits the maximum rotation speed. It works for all speed, torque, and power, and it is normally used in power and torque modes.

#### POWER LIMIT

The SFOC\_PWR\_LMT parameter in NVM limits the maximum power. This parameter is useful when commanding in torque and speed modes.

#### **CURRENT LIMIT**

The SFOC\_DRV\_CURR\_DRV\_LMT parameter in NVM limits the Iq, which subsequently limits the  $I_{BB}$ . This parameter is useful when commanding in power and speed modes.

# Motor Control Application (MCA) Finite State Machine (FSM)

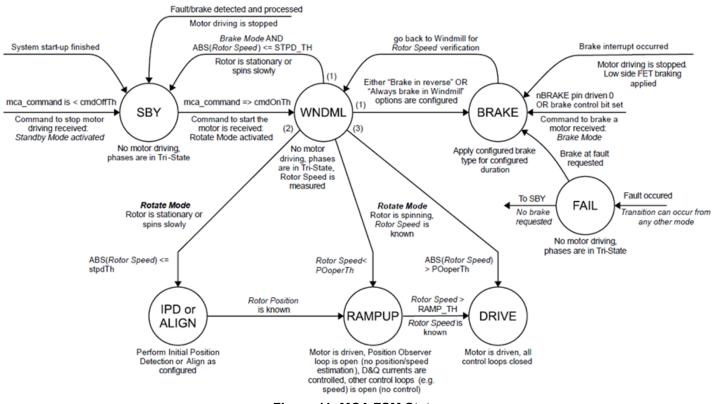

A89333 implements the FOC algorithm through a state machine, composed of four modes and six distinct states. The four modes of the MCA (motor controller application) are:

1. Standby Mode—This mode is activated after completion of

the system startup routine or receipt of the command to stop motor driving (motor control application FSM enters SBY state, as described next).

- 2. Rotate Mode—This mode is activated when a command to start the motor is received (on exit from the SBY state).

- 3. Brake Mode—This mode is activated when a command to brake the motor is received.

- 4. Fail Mode—This mode is activated when one of the enabled faults is detected. Active fail mode is reported by activation of the nFLT pin.

The active mode of MCA can be read in the SW status register via  $I^2C$  communication.

The distinct states of the MCA FSM are shown in Figure 11:

- A89333 powers up in the standby state (SBY) with external power bridge in tri-state mode.

- After the internal initialization is complete and once a command to run the motor is received, the A89333 transitions to the windmill check state (WNDML) to determine the initial status of motor movement and then start to drive the motor as shown in Figure 11.

- If the motor is stationary or spinning at a very low speed that is considered to be stationary (typical startup), the A89333 enters the IPD state or the align state—depending on the NVM option (ALIGN\_TYPE) to determine the initial rotor position or to put rotor into a known position—followed by the openloop ramp-up (RAMPUP) and drive states.

- If the motor spins in the reverse direction (reverse windmill), braking (BRAKE mode) or deceleration with FOC control is applied to stop the motor.

- Once the motor stops, the typical startup routine can be applied as before.

- If the motor is already rotating in the correct direction (forward windmill), depending on the NVM option (described in the Windmilling—WNDML section), the driver can enter the drive state directly, skipping the IPD/align state and the ramp-up phase, or braking/FOC deceleration can be used to stop the motor, such as the reverse windmill, followed by typical startup.

The active state of the MCA can be read in the SW status register via  $I^2C$  communication.

## 48 V Sensorless Code-Free FOC BLDC Motor Controller

Figure 11: MCA FSM States

#### STANDBY-SBY

In the SBY state, the motor is not driven, and the power stage is in tri-state, so the motor can be externally rotated.

The A89333 transitions to the windmill (WNDML) state only when MCA\_COMMAND exceeds the command on threshold of CMD\_ON\_TH and returns to standby when MCA\_COMMAND is less than the command off threshold of CMD\_OFF\_TH.

The A89333 enters standby mode when one of the following conditions is verified:

- After completion of the system startup routine.

- At any point in time (independently, based on current state) after a fault is processed in the fail state.

- In brake mode, after the rotor successfully stops.

- If MCA\_COMMAND reduces to less than CMD\_OFF\_TH. This is the procedure for commanding the motor to stop.

#### WINDMILLING-WNDML

In this state, the motor is not driven; however, the back electromagnetic force (BEMF) signals from the windings of the motor is analyzed to determine the rotation speed of the motor, the position of the rotor, and the direction of movement.

Based on the rotor speed measurement, the state machine reacts as follows:

- If the motor speed is less than the stopped threshold (STPD\_TH, NVM parameter) or if an illegal switching sequence is detected, the device enters initial position detection (IPD) or rotor alignment (ALIGN) to determine the rotor position.

- If motor rotation exceeds the stopped threshold (STPD\_TH) and:

- □ Motor rotation is in the proper direction:

- ♦ If the brake is enabled during the windmill state (BRAKE\_IN\_WNDML\_ALWAYS\_EN = 1, NVM parameter), the device enters the BRAKE state to reduce speed. The brake pattern is applied until the rotor is stationary. When speed is less than STPD\_TH, the device enters the standby state.

## 48 V Sensorless Code-Free FOC BLDC Motor Controller

- If the brake is not enabled during the windmill state, the device enters the drive or ramp-up state, depending on the absolute value of the speed value with respect to the observer operational threshold (PO\_OPER, configurable NVM parameter).

- □ Motor rotation is in the improper direction:

- ◆ If the brake is enabled in the windmill state (BRAKE\_IN\_WNDML\_ALWAYS\_EN = 1 or BRAKE\_IN\_REVERSE\_TYPE = 1), the device enters the brake state to reduce speed. From the brake state, the device returns to the windmill state to verify the speed condition. When the speed is less than STPD\_TH, the device enters the standby state.

- If the brake is not enabled in the windmill state, the motor is decelerated by FOC. Once it stops, it restarts in the opposite direction.

#### IPD AND ALIGN

The startup of a motor from stationary requires a known rotor position. A89333 supports both initial position detection (IPD) and alignment techniques.

- IPD (ALIGN\_TYPE = 1, configurable NVM parameter), initial rotor position is determined by measuring the stator inductance difference caused by rotor flux. The IPD technique offers smoother and faster startup, without reverse spinning by using salient characteristics and winding saturation characteristics to determine the rotor position. IPD is performed in two stages:

- □ In the first stage, test-pulse sequences are applied to the motor. If there is sufficient saliency  $(L_q \neq L_d)$ , A89333 locks the rotor position within 30° of 0° to 180° or 180° to 360°.

- □ When the first stage completes, A89333 applies a test sequence that uses the saturation property of the phase inductances of the motor to determine the current magnetic polarity of the rotor. Once the entire sequences complete, A89333 can determine the rotor angle within 30° accuracy.

- Align mode (ALIGN\_TYPE = 0). A89333 supports both AC and DC alignment.

- □ DC alignment is enabled by configuring SFOC\_ACDC\_ALIGN\_TYPE = 0. A DC current is injected for a fixed length of time that is configured by the SFOC\_ALGN\_TIME parameter, such that the rotor aligns with the stator in a known position. The current limit during DC alignments is configured through the SFOC\_ALGN\_D\_CURR\_REF parameter. The

SFOC\_ALGN\_TIME and SFOC\_ALGN\_D\_CURR\_REF parameters are generally related to the inertia of the system, and it is advisable to increase these two parameters if the inertia is large or if a load is applied on the shaft.

□ AC alignment is enabled by configuring SFOC\_ACDC\_ALIGN\_TYPE = 1. A low-currentcontrolled driving frequency is applied to the winding to generate a known-position flux in the rotor. The integrated permanent magnet rotor gravitates to the generated stator flux. The AC alignment mode spins the rotor in openloop control mode for the configured amount of time (ALGN\_DUR, SFOC\_ALGN\_TIME) with constant frequency (AC\_ALGN\_FREQ, 1/ALGN\_DUR) and current reference (SFOC\_ALGN\_D\_CURR\_REF). The alignment period should be chosen to match with the load torque required to gravitate the rotor. Longer alignment periods are more likely to catch the rotor than shorter alignment periods.

In align mode, the rotor may oscillate for some time before it starts to accelerate. This mode is typically used when the rotor position cannot be detected by the IPD. It is also a default action if the IPD fails to detect the initial rotor position (IPD\_FAIL\_ACTION).

After alignment or IPD completes, the FOC algorithm assumes that the rotor is stationary and is in the expected position, and the device enters the ramp-up state.

#### RAMP-UP-RAMPUP

During ramp-up, the driving frequency increases in open-loop mode until sufficient BEMF is generated to allow the observer to accurately detect the rotor speed and position for the transition into the closed-loop state (drive state).

Open-loop ramp-up increases rotor frequency up to RAMP\_UP\_FREQ based on the following parameters:

- SFOC\_RAMP\_TIME, which defines the length of the ramp-up phase.

- SFOC\_RAMP\_STEP, which defines the acceleration [freq/s] during the ramp-up phase only.

- SFOC\_RUP\_D\_CURR\_REF, which defines the current during ramp-up. Ramp-up speed is not affected by the value of the current. The appropriate current level depends on the properties of the motor and the connected load.

The choice of SFOC\_RAMP\_STEP and SFOC\_RAMP\_TIME affects the frequency of occurrences of transitions between open-loop and closed-loop states.

For reliable start-up, an OL-CL transition frequency greater than 35 Hz is advised. This is achieved by selecting: 1) a RAMP\_STEP value that is not excessively large, to allow use of a current equal to 60% of the rated current; and 2) a RAMP\_TIME that is not excessively small.

Motors with larger inertia typically require smaller SFOC\_RAMP\_STEP and longer SFOC\_RAMP\_TIME.

For fast start-up with minimized start time, the ramp-up time in the open-loop state must be minimized. This may require an OL-CL transition frequency of less than 35 Hz at the expense of reliability. In addition, the value of RAMP\_STEP must be increased, the value of the current to start the motor must be increased to the value of 80% to 100% of the nominal current, and the RAMP\_TIME value must be reduced.

Generally, fast start-up demands high current.

#### DRIVE—DRIVE

In the drive state the motor spins using a sensorless field-oriented control (SFOC) technique.

In sensorless operation, the motor angle and speed are estimated based on the motor electrical model (inductance, resistance) and the voltage and current that are applied.

In the drive state, the current can be further controlled and limited by the following parameters:

- SFOC\_DRV\_CURR\_DRV\_LMT sets the maximum current driving capability of the Q axis.

- SFOC\_DRV\_CURR\_RATE\_LMT and SFOC\_DWN\_CURR\_RATE\_LIMIT limit the rate of growth and decrease of the current on the Q axis.

To prevent sudden changes in the torque applied to the motor, which could result in acoustic noise, the A89333 provides the option to limit the maximum rate of change of the speed command by using the SFOC\_REF\_RATE\_LMT parameter.

#### **REGENERATIVE MODE**

In case of strong deceleration, the motor can operate as a generator and transfer energy back to the power. If the power supply is not able to absorb the energy,  $V_{BB}$  voltage is increased [pumped up; PUP], with the potential to damage the system.

The A89333 can limit the  $V_{BB}$  pump-up using the SFOC\_VBB\_LMT and SFOC\_VBB\_LMT\_TH parameters. Alternatively, the Iq regenerative current can be limited using the SFOC\_CURR\_GEN\_LMT and SFOC\_GEN\_CURR\_RATE\_LMT parameters.

#### BRAKE—BRAKE

Brake mode enables rapid motor shutdown, when desired. During braking, the three low-side drivers—connecting the three motor terminals together and short the motor BEMF—are enabled. In brake mode, the current of the winding is limited only by the motor and the resistance of the external FETs. Because of this, care must be taken to avoid excessive current in the FETs when braking. Several configuration options are available for programming in the NVM to allow for safe braking, such as pulsed braking and braking hold-off based on motor frequency.

In the brake state, the device activates the low-side MOSFET, braking the motor according to these parameters:

- BRAKE\_FET\_ON\_DURATION

- BRAKE\_FET\_OFF\_DURATION

If motor speed exceeds BRAKE\_FREQ\_TOO\_HIGH\_TH, the motor coasts before the brake is activated. This prevents generation of excessively high current that could damage the MOSFET or the motor.

The device enters the brake state when one of these conditions is verified:

- Pin nBRAKE is driven low.

- Brake bit is set in the BRAKE\_CTRL register.

- Windmill state is active and a braking feature is required, as described in the Windmilling—WNDML section.

- Speed command MCA\_COMMAND is less than CMD\_OFF\_TH and BRAKE\_IF\_OFF\_EN = 1. If BRAKE\_IF\_OFF\_EN = 0, the device enters the standby state and the motor coasts.

If BRAKE\_IF\_OFF\_EN = 1, the device also keeps the motor braked (low-side MOSFET on) after the motor stops.

NOTE: If SOFT\_OFF\_EN is set, the motor can be decelerated in the closed-loop state (drive state). For more information about soft deceleration of the motor, refer to the APEK89333 user manual available on the Allegro website.

### FOC Algorithm Speed and Current Loop

In speed mode, the command from MCA\_COMMAND is used as a reference set point to the speed loop, and the output of the speed loop is used as the reference for the Q-axis current in the current loop.

In torque mode, the command from MCA\_COMMAND is passed directly to the current loop as the reference for the Q-axis current.

The reference for the D-axis current can be set using the regis-

ter SFOC\_DRV\_D\_CURR\_REF; however—to ensure that the stator and rotor field are 90° out of phase with each other, which allows for the maximum available torque and system efficiency—the recommended setting is zero.

PI controllers, one for speed and one for current loop, can be tuned using SFOC\_D\_CURR\_KP, SFOC\_D\_CURR\_KI, SFOC\_Q\_CURR\_KP, and SFOC\_Q\_CURR\_KI NVM settings.

The A89333 integrates a space-vector modulation (SVM) technique that optimizes use of the supply voltage and increases the base motor speed. The algorithm also implements a  $V_{BB}$  compensation feature that automatically adjusts the duty cycle to correct disturbances or sudden voltage variations on the supply voltage. The system works as a percentage of the nominal  $V_{BB}$  (VBB\_NOM NVM parameter) and calculates the duty cycle,  $\delta$ , for phase voltages according to:

Equation 12:

$$\delta = \frac{V_{phase}}{VBB_{measured}(\%) \times VBB_{nom}}$$

Example 1:

$VBB_{nom} = 12 V$

$v_{phase}$  calculated from FOC algorithm is 50% of VBB<sub>nom</sub> VBB<sub>measured</sub> from ADC = 12 V, so it is 100% of VBB<sub>nom</sub> Calculation of  $\delta$ :

Equation 13:

$$\delta = \frac{V_{phase}}{VBB_{measured}(\%) \times VBB_{nom}}$$

$$= \frac{50\% VBB_{nom}}{100\% \times VBB_{nom}}$$

$$= 50\%$$

Example 2:

$VBB_{nom} = 12 V$

$v_{phase}$  calculated from FOC algorithm is 50% of VBB<sub>nom</sub> VBB<sub>measured</sub> from ADC = 6 V, so it is 50% of VBB<sub>nom</sub> Calculation of  $\delta$ :

Equation 14:

$$\delta = \frac{V_{phase}}{VBB_{measured}(\%) \times VBB_{nom}}$$

$$= \frac{50\% VBB_{nom}}{50\% \times VBB_{nom}}$$

$$= 100\%$$

The compensation of  $V_{BB}$  is guaranteed until  $V_{BB}$  measured is less than  $2\times VBB_{nom}.$

#### OBSERVER

For sensorless-mode operation, the motor angle and speed data are estimated in the observer block—without the need for an external sensor.

The machine parameters required in the A89333 observer are the motor phase inductance, sfocLs, and the motor phase resistance, sfocRs, according to:

Equation 15:

$$sfocLs = round \left(\frac{2\pi \times i_{max} \times f_{res} \times motorLs \times 2^{(sfocLsFl+21)}}{0.298 \times VBB_{nom}}\right),$$

where:

- sfocLs [unitless] is the stator inductance NVM setting.

- i<sub>max</sub> [A] is the maximum system current.

•

$$f_{res} = \frac{1}{9 \times 2^{sfocFreqRes}} [Hz/LSB]$$

is the frequency resolution.

- motorLs [H] is the motor phase to neutral inductance (phase-to-phase/2).

- sfocLsFl [unitless] is the SFOC stator inductance fractional length NVM setting (signed).

- VBB<sub>nom</sub> [V] is the nominal DC link voltage (should be in alignment with VBB\_NOM setting).

Equation 16:

$$sfocRs = round \left(\frac{motorRs \times i_{max} \times 2^{(sfocRsFl+11)}}{0.298 \times VBB_{nom}}\right)$$

where:

- sfocRs [unitless] is the stator resistance NVM setting.

- i<sub>max</sub> [A] is the maximum system current.

- motorRs [Ω] is the motor phase to neutral resistance (phase-to-phase/2).

- sfocRsFl [unitless] is the SFOC stator inductance fractional length NVM setting (signed).

- VBB<sub>nom</sub> [V] is the nominal DC link voltage (should be in alignment with VBB\_NOM setting).

Proper functioning of the observer requires proper tuning of the controller parameters SFOC\_PO\_FREQ\_K and SFOC\_PO\_THETA\_K.

### DIAGNOSTIC AND PROTECTION FEATURES

A89333 integrates advanced diagnostics for critical hardware protection and motor control diagnostics. Hardware protections include overvoltage, undervoltage, over temperature, and shortcircuit protection. Motor control diagnostics include lock detection (loss of sync) and no-motor start.

If a fault event occurs, the nFLT pin is pulled low to indicate a fault condition. The nFLT pin can also be connected to the nBRAKE pin to brake the motor in case of an overcurrent fault. Braking is not allowed for the OVP, UV, OT, and lock detection states.

Every fault can be enabled or disabled (masked) using the NVM parameters UVS\_DISABLE, OVT\_DISABLE, OVP\_ENABLE, OCP\_ENABLE, ROT\_STALL\_DET\_CTR = 0, and NO\_MOTOR\_START\_EN.

Fault data flags can be read in the SW status register via  $\mathrm{I}^2\mathrm{C}$  communication.

Table 4: Fault Table

| Table 4: Fault Table                                      |                                                                                |                    |  |  |  |  |  |

|-----------------------------------------------------------|--------------------------------------------------------------------------------|--------------------|--|--|--|--|--|

| Fault                                                     | Fault Action                                                                   | Latched            |  |  |  |  |  |

| V <sub>BB</sub><br>Undervoltage                           | Disable outputs                                                                | Ν                  |  |  |  |  |  |

| Over Temp.<br>Protection                                  | Disable outputs                                                                | Ν                  |  |  |  |  |  |

| V <sub>BB</sub><br>Overvoltage<br>Protection<br>(VBB OVP) | Disable outputs                                                                | N                  |  |  |  |  |  |

| Overcurrent<br>Protection<br>(OCP)                        | Disable outputs<br>Latch reset with command off/<br>on sequence or power-cycle | Y                  |  |  |  |  |  |

| Loss of Sync<br>(Lock Det)                                | Set lock detect timeout—<br>disable outputs                                    | (SW latched fault) |  |  |  |  |  |

| No-Motor Start                                            | Set lock detect timeout—<br>disable outputs                                    | (SW latched fault) |  |  |  |  |  |

#### VBB UNDERVOLTAGE—VBB UVS

When digital logic is running and the supply voltage on the VBB pin reduces to less than the UVS\_TH, the A89333 disables the outputs until the supply voltage reduces to less than the operating threshold, which is lower than the  $V_{BBUVLO}$  threshold.

After the  $V_{BB}$  undervoltage is detected, the outputs are disabled, the controller enters the fail mode, and fault reporting is performed by pulling low the nFLT pin and setting the corresponding fault flag in the SW status register. When the  $V_{BB}$  level rises to greater than UVS\_TH (plus the hysteresis level), the outputs are re-enabled automatically (not latched), the fault flag is cleared, and the controller transitions to the standby mode and state. In the standby state, the controller verifies that the command exceeds the threshold of CMD\_ON\_TH, then transitions to the windmill state, where a speed check is performed and used by the device to determine if the start is from a stationary position or with a moving rotor.

The  $V_{BB}$  undervoltage protection level is programmable in NVM using the UVS\_TH parameter (see Table 5). The  $V_{BB}$  undervoltage diagnostic is independently activated by the control method and state. If needed, the fault can be masked using the UVS\_DISABLE parameter in NVM.

| Table | 5: | UVS_ | TH | Parar | neter |

|-------|----|------|----|-------|-------|

|-------|----|------|----|-------|-------|

| UVS_TH | V <sub>BB</sub> UVS (V) |

|--------|-------------------------|

| 0      | 32                      |

| 1      | 25                      |

| 2      | 7                       |

#### **VBB, UV, AND NVM REPROGRAMMING**

When the device is in an undervoltage (UV) state but the  $V_{\rm BB}$  exceeds the operating threshold of the supply voltage for digital logic, if in user mode, it is possible to reprogram the NVM (EEPROM) registers regardless of the selected external command source and the state of the FG pin. Changes to NVM take effect only after POR.

The UV condition prevents incorrect transactions that can result from FG/RD pin toggling and guarantees that the FG/RD pin is in the proper state for I<sup>2</sup>C for any NVM configuration. To program the EEPROM, increase  $V_{BB}$  beyond 25 V after I<sup>2</sup>C communication is established.

If the FG/RD pin configuration cannot cause toggling (FG/RD pin is in the high state), it is possible to use I<sup>2</sup>C without UV and the EXT\_CMD\_SRC is not I<sup>2</sup>C. This allows NVM shadow programming when in user mode or SW status register consultation for diagnostic purposes. In this case, serial communication should be performed when the controller is in the standby state (motor stopped), and it can lead to unexpected motor starts.

#### OVERTEMPERATURE PROTECTION—OVT/TSD

The A89333 protects itself from overheating with an internal thermal monitoring circuit. If the junction temperature exceeds the upper threshold  $T_{J_TSD}$ , when the OVT is detected, the outputs are disabled, the controller enters the fail mode, and fault reporting is performed by pulling low the nFLT pin and setting the corresponding fault flag in the SW status register.

When device temperature returns to less than the  $T_{J_TSD}$  threshold minus the hysteresis level,  $\Delta T_J$ , the outputs are re-enabled automatically (not latched), the fault flag is cleared, and the controller transitions to the standby mode and state. In the standby state, the controller verifies that the command exceeds the threshold of CMD\_ON\_TH, then transitions to the windmill state, where a

## 48 V Sensorless Code-Free FOC BLDC Motor Controller

speed check is performed and used for the device to determine if the start is from a stationary position or with a moving rotor.

The over-temperature protection diagnostic is independently activated by the control method and state. If not needed, the fault can be masked using the OVT\_DISABLE parameter in NVM.

#### VBB OVERVOLTAGE PROTECTION—VBB OVP

Overvoltage protection is intended to protect the IC and the threephase inverter in applications where the motor could be rotated at high velocity or where quick decelerations of motor speed are needed, which can result in significant energy fed back from motor coils to the power supply. Overvoltage could also be relevant when low-side FET braking is applied; because the A89333 switches the low-side FETs during braking, during the off time ( $t_{off}$ ) the voltage generated on the inductors of the motor force the current to flow in the body diode of the high-side FETs, charging the capacity of the DC-link and generating a pump-up of V<sub>BB</sub>.

When  $V_{BB}$  voltage exceeds OVP\_TH, A89333 disables the outputs. After the  $V_{BB}$  overvoltage is detected, the outputs are disabled, the controller enters the fail mode, and fault reporting is performed by pulling low the nFLT pin and setting the corresponding fault flag in the SW status register. When the  $V_{BB}$  level reduces to less than the OVP\_TH, the outputs are re-enabled automatically (not latched), the fault flag is cleared, and the controller transitions to the standby mode and state. In the standby state, the controller verifies that the command exceeds the threshold of CMD\_ON\_TH, then transitions to the windmill state, where a speed check is performed and used by the device to determine if the start is from a stationary position or with a moving rotor.

The  $V_{BB}$  overvoltage protection level is programmable using the OVP\_TH parameter in NVM, in the range of approximately 0 V to 80 V. The  $V_{BB}$  overvoltage diagnostic is independently activated by the control method and state. If needed, the fault can be masked using the OVP EN parameter in NVM.

#### OVERCURRENT PROTECTION—OCP (SHORT PRO-TECTION)