# AHV85111

## Self-Powered Single-Channel Isolated GaNFET Driver with Regulated Bipolar Output Drive

### FEATURES AND BENEFITS

- Power-Thru integrated isolated bias

No high-side bootstrap or external secondary-side bias

- Bipolar drive output, with adjustable regulated positive rail

- Regulated 3.3 V low power bias output

- 50 ns propagation delay, with excellent device-to-device matching of 5 ns

- Separate drive output pins: pull-up (2.8 Ω) and pull-down (1.0 Ω)

- Supply voltage 10.5 V < V<sub>DRV</sub> < 13.2 V

- + Undervoltage lockout on primary  $V_{\text{DRV}}$  and secondary  $V_{\text{SEC}}$

- Enable pin with fast response

- Overtemperature protection

- CMTI > 100 V/ns dv/dt immunity

- Creepage distance > 8 mm

- Distance-through-insulation  $DTI \ge 450 \ \mu m$

- Safety regulatory approvals (pending)

□ 5.7 kV RMS V<sub>ISO</sub> per UL 1577

- 8 kV pk V<sub>IOTM</sub> maximum transient isolation voltage per VDE0884-11

- $\square$  630 V pk maximum working isolation voltage

### **APPLICATIONS**

- AC-DC and DC-DC converters: Totem-pole PFC, LLC half-/full-bridge, SR drive, multi-level converters, phase-shifted full-bridge

- Automotive: OBC, traction drive

- Industrial: transportation, robotics

- Grid Infrastructure: micro-inverters, solar

### DESCRIPTION

The AHV85111 isolated gate driver is optimized for driving GaNFETs in multiple applications. An isolated dual positive/ negative output bias supply is integrated into the driver device, eliminating external gate drive auxiliary bias supply or high-side bootstrap. The bipolar output rails with adjustable and regulated positive rail improves dv/dt immunity, greatly simplifies the system design, and reduces EMI through reduced total common-mode (CM) capacitance. It also allows the driving of a floating switch in any location in a switching power topology.

The driver has fast propagation delay and high peak source/ sink capability to efficiently drive GaNFETs in high-frequency designs. High CMTI combined with isolated outputs for both bias power and drive make it ideal in applications requiring isolation, level-shifting, or ground separation for noise immunity.

The device is available in a compact low-profile surface-mount NH package. Several protection features are integrated, including undervoltage lockout on primary and secondary bias rails, internal pull-down on IN pin and OUTPD pin, fast response enable input, and overtemperature shutdown.

## PACKAGE

Not to scale

10 mm × 7.66 mm × 2.53 mm 12-pin low-profile surface mount

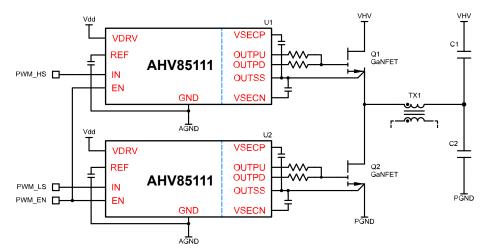

### **TYPICAL APPLICATION**

Figure 1: Typical AHV85111 half-bridge application—eliminates high-side bootstrap

## Self-Powered Single-Channel Isolated GaNFET Driver with Regulated Bipolar Output Drive

#### **SELECTION GUIDE**

| Part Number   | Switch     | # of Channels | Output   | Isolation | Package                                                       |

|---------------|------------|---------------|----------|-----------|---------------------------------------------------------------|

| AHV85111KNHTR | GaN Driver | 1             | Unipolar | Isolated  | 10 mm × 7.66 mm × 2.53 mm<br>12-pin low-profile surface mount |

#### ABSOLUTE MAXIMUM RATINGS [1]

| Characteristic         | Symbol                                | Notes                         | Rating                        | Unit |

|------------------------|---------------------------------------|-------------------------------|-------------------------------|------|

| Drive Supply Voltage   | V <sub>DRV</sub>                      | VDRV, wrt to GND              | V <sub>GND</sub> – 0.5 to 15  | V    |

| Input Data             | V <sub>IN</sub>                       | IN, wrt to GND                | V <sub>GND</sub> – 0.5 to 15  | V    |

| Enable                 | V <sub>EN</sub>                       | EN, wrt to GND                | V <sub>GND</sub> – 0.5 to 15  | V    |

| Select                 | V <sub>SEL</sub>                      | SEL to GND; internal use only | V <sub>GND</sub> – 0.5 to 15  | V    |

| Reference Voltage      | V <sub>REF</sub>                      | 3.3 V reference, wrt GND      | V <sub>GND</sub> – 0.5 to 4   | V    |

| Output Drive Pull-Up   | V <sub>OUTPU</sub>                    | OUTPU to OUTSS                | V <sub>SECN</sub> – 0.5 to 15 | V    |

| Output Drive Pull-Down | V <sub>OUTPD</sub>                    | OUTPU to OUTSS                | V <sub>SECN</sub> – 0.5 to 15 | V    |

| Isolated Bias Supply   | V <sub>SECP</sub> – V <sub>SECN</sub> | Total rail                    | -0.5 to 15                    | V    |

| Junction Temperature   | TJ                                    |                               | -40 to 150                    | °C   |

<sup>[1]</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## VSECP AND VSECN PIN CAPACITORS: -40°C < T<sub>J</sub>< 125°C, 10.5 V < V<sub>DRV</sub> < 13.2 V, C<sub>SEC(NET)</sub> = 22 nF, C<sub>out</sub> = 1 nF, unless otherwise stated. Note that C<sub>SEC(NET)</sub> is the net equivalent of C<sub>SECP</sub> in series with C<sub>SECN</sub>, i.e. (C<sub>SECP</sub> × C<sub>SECN</sub>) / (C<sub>SECP</sub> + C<sub>SECN</sub>).

| - 360(NE                | 1)                |                                                                                        | - 3ECF -          | SECIN (             | 3ECF - 3 | BECIN/ |

|-------------------------|-------------------|----------------------------------------------------------------------------------------|-------------------|---------------------|----------|--------|

| Characteristic          | Symbol            | Test Conditions                                                                        | Min.              | Typ. <sup>[3]</sup> | Max.     | Unit   |

| VSEC Pin Capacitor CSEC | C <sub>SECP</sub> | External capacitance connected between VSECP and OUTSS pins; external $C_{OUT}$ = 1 nF | 5 [1]             | 27                  | 100 [1]  | nF     |

|                         | C <sub>SECN</sub> | External capacitance connected between VSECN and OUTSS pins; external $C_{OUT}$ = 1 nF | 15 <sup>[1]</sup> | 100                 | 330 [1]  | nF     |

<sup>[1]</sup> Smaller C<sub>SEC</sub> values than the recommended typical value can give higher voltage ripple on CSEC.

<sup>[2]</sup> Larger C<sub>SEC</sub> values will mean longer startup times.

<sup>[3]</sup> Typical values should be chosen to match the ratio of  $V_{SECP}$  to  $V_{SECN}$ .

#### **ESD RATINGS**

| Characteristic       | Symbol           | Test Conditions | Value | Unit |

|----------------------|------------------|-----------------|-------|------|

| Human Body Model     | V <sub>HBM</sub> |                 | ±2    | kV   |

| Charged Device Model | V <sub>CDM</sub> |                 | ±500  | V    |

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic                         | Symbol                | Test Conditions* | Value | Unit |

|----------------------------------------|-----------------------|------------------|-------|------|

| Junction-to-Ambient Thermal Resistance | R <sub>θJA</sub>      |                  | TBD   | °C/W |

| Junction-to-Case Thermal Resistance    | $R_{	extsf{	heta}JC}$ |                  | TBD   | °C/W |

\*Additional thermal information available on the Allegro website.

## Self-Powered Single-Channel Isolated GaNFET Driver with Regulated Bipolar Output Drive

#### **Revision History**

|   | Number | Date            | Description     |

|---|--------|-----------------|-----------------|

| Γ | -      | August 30, 2022 | Initial release |

Copyright 2022, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com