# ACS710 Evaluation Board Getting Started Guide

#### Dear Customer:

Thank you for purchasing an Allegro<sup>®</sup> MicroSystems, Inc., product evaluation kit. This kit is intended for evaluation use only, and is not intended for use in a production environment.

The instructions in this kit are designed for use with the following product evaluation boards:

• ACS710, PN: 85-0350-001, Rev. 5

This document includes:

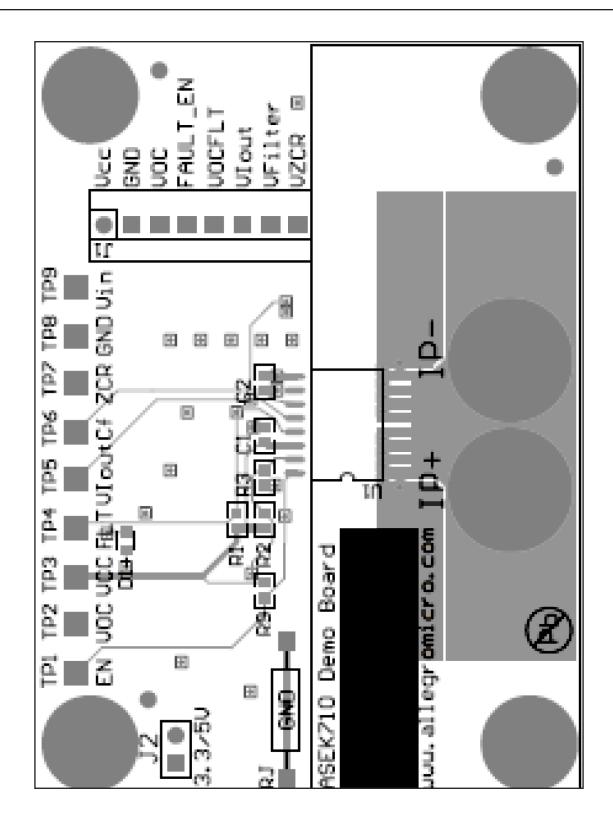

- Top side layout of the evaluation board

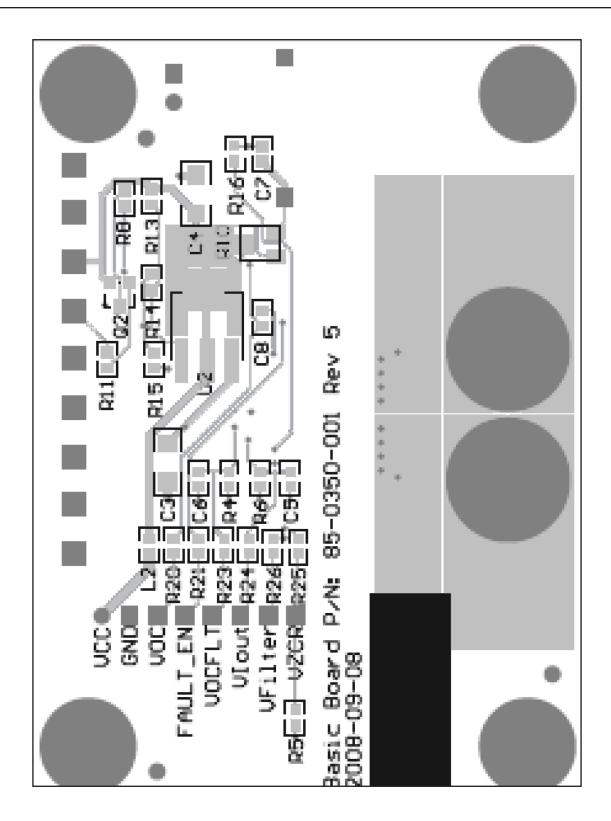

- Bottom side layout of the evaluation board

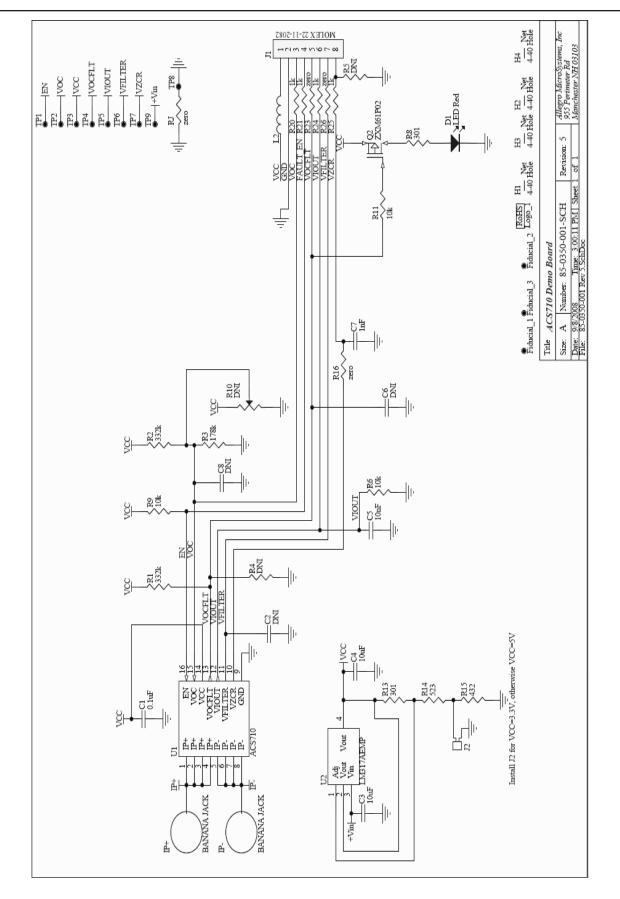

- Electrical schematic of the evaluation board

- Basic instructions for completing a fault test using the evaluation board

Additional information may be available on the Allegro MicroSystems website page for the ACS710:

- Bill of materials of the evaluation board

- Gerber files of the evaluation board

- Datasheet for the ACS710

This document provides a basic guide for providing power and signal to the evaluation board and product. The datasheet provides the specific details about the product to best understand how the product can be in a typical application. If you should need any further assistance please call 1-508-854-5428 or contact the field application engineer for your area by visiting the Design Center > <u>Technical Assistance</u> link on the Allegro MicroSystems website.

- Allegro MicroSystems

## Introduction

This evaluation board enable verification of the ACS710 functionality by simply powering on the board and connecting an adjustable current source from board contacts IP+ to IP–.

The test points (TP) are identified in the following table. Refer to the top-side layout diagram for locations on the board.

| Test<br>Point<br>Name | Device<br>Pin Name | Function                                                 |

|-----------------------|--------------------|----------------------------------------------------------|

| TP1                   | FAULT_EN           | Must be high to enable fault algorithm                   |

| TP2                   | VOC                | Sets fault threshold                                     |

| TP3                   | VCC                | Regulated voltage: 5 V with J2 open 3.3 V with J2 closed |

| TP4                   | FAULT              | Overcurrent fault flag output                            |

| TP5                   | VIOUT              | Analog voltage output; proportional to<br>current        |

| TP6                   | VFILTER            | Filters the output of the device                         |

| TP7                   | VZCR               | Zero-ampere current reference                            |

| TP8                   | GND                | Ground                                                   |

| TP9                   | VIN                | Board supply voltage: $V_{CC}$ + 3 V < $V_{IN}$ < 25 V   |

## **Creating a Fault Condition:**

Resistors R2 (332 k $\Omega$ ) and R3 (178 k $\Omega$ ) on the evaluation board create a resistive voltage divider that sets the overcurrent fault threshold, input to the VOC pin. The installed resistor values set  $V_{OC}$  to be about  $1/_3 \times V_{CC}$ .

- For unidirectional current sensing this means that a fixed fault threshold will occur at about:

- 32 A for the ACS710KLATR-12CB-T (Sens 56 mV/A)

- º 64 A for the ACS710KLATR-25CB-T2 (Sens 28 mV/A)

In either case, the fault is tripped independently of V<sub>CC</sub>.

• For bidirectional current sensing this means that a fixed fault threshold will occur at about:

□ ±32 A for the ACS710KLATR-12CB-T (Sens 56 mV/A)

□ ±64 A for the ACS710KLATR-25CB-T2 (Sens 28 mV/A)

To set a different current fault threshold, users can either apply a voltage to VOC pin from an external source or place a potentiometer (R10) on the board. Refer to the Functional Description section of the ACS710 datasheet for detailed information about calculating  $V_{\rm OC}$  for the required fault level.

When the FAULT\_EN pin is high, and the current threshold is exceed, a fault condition will occur. LED D1 will turn on when the fault is latched. See the datasheet for more details on the fault algorithm, as well as how to reset the fault using FAULT\_EN.

Figure 1. Top-side layout of the evaluation board

Figure 2. Bottom-side layout of the evaluation board

Figure 3. Electrical schematic of the evaluation board

Copyright ©2012, Allegro MicroSystems, Inc.

The information contained in this document does not constitute any representation, warranty, assurance, guaranty, or inducement by Allegro to the customer with respect to the subject matter of this document. The information being provided does not guarantee that a process based on this information will be reliable, or that Allegro has explored all of the possible failure modes. It is the customer's responsibility to do sufficient qualification testing of the final product to insure that it is reliable and meets all design requirements.

For the latest version of this document, visit our website:

#### www.allegromicro.com