# MC Package Bare Evaluation Board User Guide

### **DESCRIPTION**

Bare evaluation boards offer a method for evaluating Allegro current sensors in a lab environment. This document describes the use of the MC current sensor evaluation board. This evaluation board (ACSEVB-MC16, TED-0004115) is intended for use with any MC package (16-pin SOICW Allegro current sensor).

### FEATURES OF THE BARE BOARD

- Enhanced thermal performance

- □ 6-layer PCB with 2 oz copper weight on all layers

- □ Nonconductive-filled via-in-pad

- ☐ High-performance FR4 material with 180°C glass transition temperature

- Flexible layout for user-installed connection points

- ☐ Standard Keystone test points

- □ SMA/SMB connector

- □ 2-pin headers

- Integrated current loop resistance can be measured directly on the evaluation board after test point installation; voltage drop can be measured for approximating power loss in the package.

#### BARE EVALUATION BOARD CONTENTS

- NOTE: It is up to the user to assemble the board with the desired current sensor and supporting circuitry. This board does not come populated with an Allegro current sensor or other components.

- Recommended supporting circuitry for all compatible current sensor are listed in the Supporting Circuitry section below.

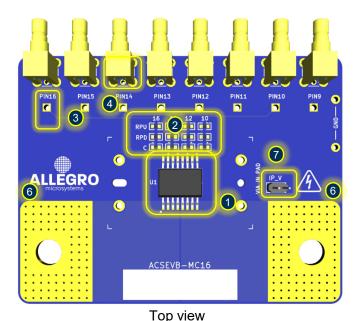

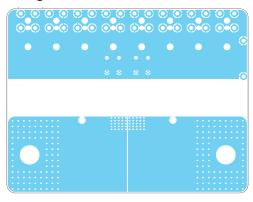

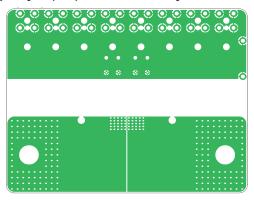

Figure 1: MC Bare Evaluation Board

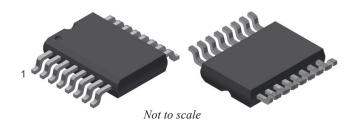

Figure 2: MC Package (SOIC-W Package)

#### Table of Contents

| Description                           | 1 |

|---------------------------------------|---|

| Features of the Bare Board            | 1 |

| Bare Evaluation Board Contents        | 1 |

| Using the Evaluation Board            | 2 |

| Performance Data                      | 3 |

| Schematic                             | 4 |

| Layout                                | 5 |

| Supporting Circuitry                  | 6 |

| Related Links and Application Support | 7 |

| Revision History                      | 8 |

### **USING THE EVALUATION BOARD**

#### **Evaluation Board Procedure**

#### SETTING UP THE EVALUATION BOARD

Upon receiving the evaluation board, it us up to the user to populate the evaluation board with the desired Allegro current sensor. It is also up to the user to install test points, SMA/SMB connectors, header connectors, and supporting circuitry, as needed.

#### CONNECTING TO THE EVALUATION BOARD

The most reliable way to connect measurement instruments to the evaluation board is to use SMB/SMA or 2-pin headers connectors along with coaxial cables. This configuration will be most resilient to external coupling and is the most mechanically stable and it is the preferred way for measurement for high-speed signal.

Keystone test points are a convenient way to connect any instrument, but is it recommended for DC setups only.

### **Evaluation Board Detailed Description**

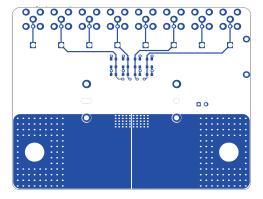

- 1. U1 is a MC package footprint (pin 1 is on bottom left side of the package footprint, see the small white dot to the left of the package footprint).

- 2. U1 pins (16 to 9; see top and bottom view of EVB) allow the option to connect:

- ♦ RPU: pull-up resistor to VCC

- ♦ RPD: pull-down resistor to GND

- ♦ C: decoupling or load capacitor to GND

NOTE: Even pin number components are on the top layer of the evaluation board (16, 14, 12, and 10) and odd pin numbers are on the bottom layer of the board (9, 11, 13, and 15). All passive components are 0603 package size.

- 3. Optional through hole test points (Keystone 5005 test points, e.g., Digikey# 36-5005-ND)

- Optional standard SMB or SMA connection points (e.g., Digikey# 1868-1429-ND)

- 5. Optional 2-pin 100 mil header connector (note: either SMB or header can be assembled)

- 6. Primary current cables mounting positions (positive current flow direction is left to right)

- 7. Optional 2-pin 100 mil header connector for voltage drop measurement across the integrated current loop of the current sensor

- 8. RB1, RB2, RB3, and RB4: rubber bumper mounting positions (e.g., Digikey# SJ61A6-ND)

Bottom view

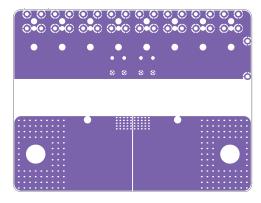

Figure 3: MC Current Sensor Evaluation Board Reference Image

### **EVALUATION BOARD PERFORMANCE DATA**

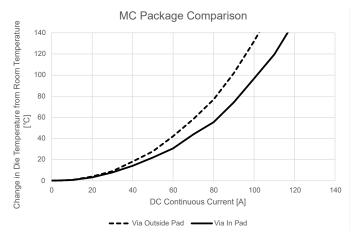

### Thermal Rise vs. Primary Current

Self-heating due to the flow of current in the package IP conductor should be considered during the design of any current sensing system. The sensor, printed circuit board (PCB), and contacts to the PCB will generate heat and act as a heat sink as current moves through the system.

The thermal response is highly dependent on PCB layout, copper thickness, cooling techniques, and the profile of the injected current. The current profile includes peak current value, current on-time, and duty cycle.

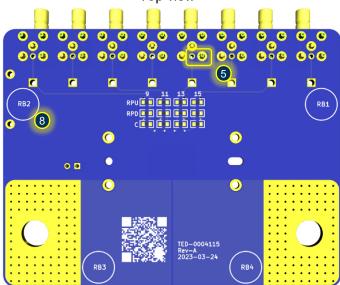

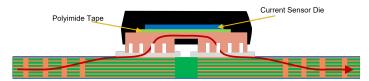

Placing vias under the copper pads of the Allegro current sensor evaluation board minimize the current path resistance and improves heatsinking to the PCB, while vias outside of the pads limit the current path to the top of the PCB trace and have worse heatsinking under the part (see Figure 4 and Figure 5 below). The ACSEVB-MC16 does include vias in pad and is recommended to improve thermal performance.

Figure 4: Vias Under Copper Pads Example

Figure 5: No Vias Under Copper Pads Example

The plot in Figure 6 shows the measured rise in steady-state die temperature of the MC package versus DC continuous current at an ambient temperature, T<sub>A</sub>, of 25 °C for two board designs: filled vias under copper pads and no vias under copper pads.

Note: Using in-pad vias has better thermal performance that no in-pad vias, and this is the design the ACSEVB-MC16 uses.

Figure 6: MC Package Comparison with and without In-Pad Vias

The thermal capacity of the MC package should be verified by the end user in the application's specific conditions. The maximum junction temperature,  $T_{J(max)}$  (165°C), should not be exceeded. Measuring the temperature of the top of the package is a close approximation of the die temperature.

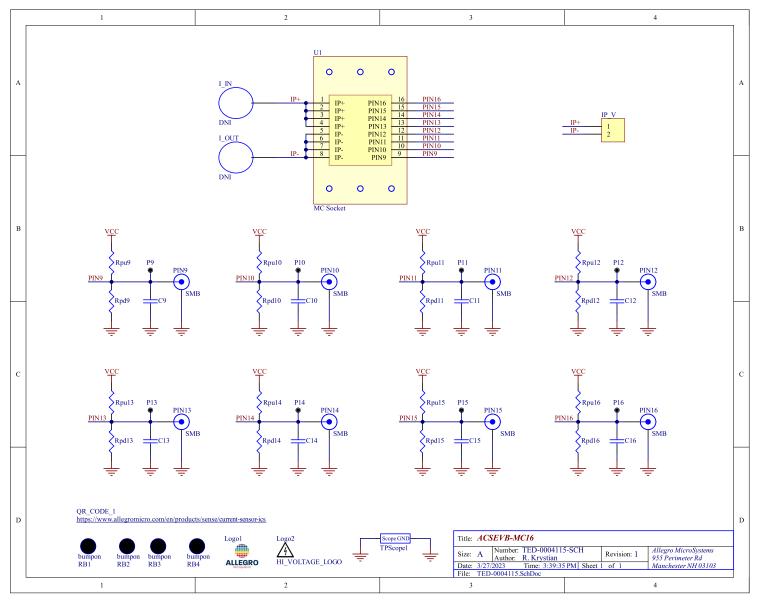

### **SCHEMATIC**

Figure 7: MC Generic Evaluation Board Schematic

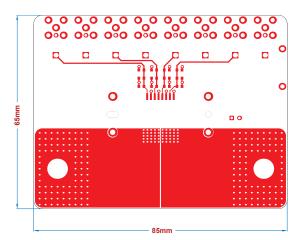

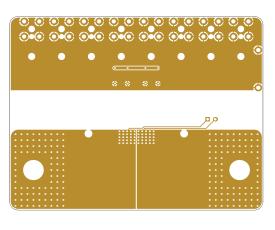

### **LAYOUT**

The MC current sensor evaluation board has the option for a 2-pin 100 mil header connector, which allows the integrated current loop resistance to be measured directly from the evaluation board. The voltage drop sensing is routed in the first internal layer (as to not reduce isolation spec of the package). As a consequence, the voltage drop will include the parasitic resistance of the vias between the top layer and the first interior layer.

Figure 8: MC Bare Evaluation Board Top Layer (left) and Interior Layer 1

Figure 9: MC Bare Evaluation Board Interior Layer 2 (left) and Interior Layer 3

Figure 10: MC Bare Evaluation Board Interior Layer 4 (left) and Bottom Layer

### **SUPPORTING CIRCUITRY**

Components listed are based on the typical application circuit given in the respective device datasheet. In the event of a conflict between this document and the main datasheet, the datasheet takes precedence.

Table 1: Evaluation Board Circuitry ACS37002 ASSEMBLY VARIANT (MC)

| Pin        | Terminal   | Components                                                                                              |  |

|------------|------------|---------------------------------------------------------------------------------------------------------|--|

| 1, 2, 3, 4 | IP+        | Tamain de fau aumant hairm anna de fuar d'intermalle.                                                   |  |

| 5, 6, 7, 8 | IP-        | Terminals for current being sensed; fused internally                                                    |  |

| 9          | OCF        | Overcurrent fault, open-drain, requires pull-up resistor                                                |  |

| 10         | VCC        | Device power supply terminal, connected to supply voltage                                               |  |

| 11         | VREF       | Zero current voltage reference                                                                          |  |

| 12         | VOUT       | Analog output representing the current flowing through IP, optional load capacitance or load resistance |  |

| 13         | VOC        | Overcurrent fault operation point input, connected to resistor divider or external power source         |  |

| 14         | GAIN_SEL_1 | Gain selection bit 1, connected to high or GND                                                          |  |

| 15         | GND        | Device ground terminal, connected to GND                                                                |  |

| 16         | GAIN_SEL_0 | Gain selection bit 0, connected to high or GND                                                          |  |

### ACS37003 ASSEMBLY VARIANT (MC)

| Pin           | Terminal | Components                                                                                              |  |

|---------------|----------|---------------------------------------------------------------------------------------------------------|--|

| 1, 2, 3, 4    | IP+      | Townian Information and Constitution alle                                                               |  |

| 5, 6, 7, 8    | IP-      | Terminals for current being sensed; fused internally                                                    |  |

| 9, 10, 14, 15 | OCF      | Overcurrent fault, open-drain, requires pull-up resistor                                                |  |

| 11            | VREF     | Overcurrent fault operation point input, connected to resistor divider or external power source         |  |

| 12            | VOUT     | Analog output representing the current flowing through IP, optional load capacitance or load resistance |  |

| 13            | VREF     | Zero current voltage reference                                                                          |  |

| 16            | GND      | Device ground terminal, connected to GND                                                                |  |

### ACS724/25 ASSEMBLY VARIANT (MC)

| Pin           | Terminal | Components                                                                                              |  |

|---------------|----------|---------------------------------------------------------------------------------------------------------|--|

| 1, 2, 3, 4    | IP+      | Townsiands for compact being considerated intermedia.                                                   |  |

| 5, 6, 7, 8    | IP-      | Terminals for current being sensed; fused internally                                                    |  |

| 9, 11, 14, 16 | NC       | No internal connection; recommended to be left unconnected in order to maintain high creepage           |  |

| 10            | VCC      | Device power supply terminal, connected to supply voltage                                               |  |

| 12            | VOUT     | Analog output representing the current flowing through IP, optional load capacitance or load resistance |  |

| 13            | FILTER   | Terminal for external capacitor that sets bandwidth                                                     |  |

| 15            | GND      | Device ground terminal, connected to GND                                                                |  |

## **RELATED LINKS AND APPLICATION SUPPORT**

**Table 2: Related Documentation and Application Support**

| Documentation                                                                                                                                          | Summary                                                                                                                               | Location                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Allegro Current Sensors Webpage                                                                                                                        | Product datasheet defining common electrical characteristics and performance characteristics                                          | https://www.allegromicro.com/en/products/<br>sense/current-sensor-ics                                                                                                                               |

| Allegro Current Sensor Package Documentation                                                                                                           | Schematic files, step files, package images                                                                                           | https://www.allegromicro.com/en/design-<br>support/packaging                                                                                                                                        |

| An Effective Method for Characterizing<br>System Bandwidth in Complex Current Sensor<br>Applications                                                   | Application note describing methods used by Allegro to measure and quantify system bandwidth                                          | https://allegromicro.com/en/insights-and-innovations/technical-documents/hall-effect-sensor-ic-publications/an-effective-method-for-characterizing-system-bandwidth-an296169                        |

| DC and Transient Current Capability/Fuse<br>Characteristics of Surface Mount Current<br>Sensor ICs                                                     | DC and Transient Current Capability/Fuse<br>Characteristics of Surface Mount Current<br>Sensor ICs                                    | https://www.allegromicro.com/en/Insights-and-Innovations/Technical-Documents/Hall-Effect-Sensor-IC-Publications/DC-and-Transient-Current-Capability-Fuse-Characteristics.aspx                       |

| High-Current Measurement with Allegro Current<br>Sensor IC and Ferromagnetic Core: Impact of<br>Eddy Currents                                          | Application note focusing on the effects of alternating current on current measurement                                                | https://allegromicro.com/en/insights-and-innovations/technical-documents/hall-effect-sensor-ic-publications/an296162_a1367_current-sensor-eddy-current-core                                         |

| Secrets of Measuring Currents Above 50 Amps                                                                                                            | Application note regarding current measurement greater than 50 A                                                                      | https://allegromicro.com/en/insights-and-innovations/technical-documents/hall-effect-sensor-ic-publications/an296141-secrets-of-measuring-currents-above-50-amps                                    |

| Allegro Hall-Effect Sensor ICs                                                                                                                         | Application note describing Hall-effect principles                                                                                    | https://allegromicro.com/en/insights-and-innovations/technical-documents/hall-effect-sensor-ic-publications/allegro-hall-effect-sensor-ics                                                          |

| Hall-Effect Current Sensing in Electric and<br>Hybrid Vehicles                                                                                         | Application note providing a greater understanding of hybrid electric vehicles and the contribution of Hall-effect sensing technology | https://allegromicro.com/en/insights-and-innovations/technical-documents/hall-effect-sensor-ic-publications/hall-effect-current-sensing-in-electric-and-hybrid-vehicles                             |

| Hall-Effect Current Sensing in Hybrid Electric Vehicle (HEV) Applications                                                                              | Application note providing a greater understanding of hybrid electric vehicles and the contribution of Hall-effect sensing technology | https://allegromicro.com/en/insights-<br>and-innovations/technical-documents/<br>hall-effect-sensor-ic-publications/hall-effect-<br>current-sensing-in-hybrid-electric-vehicle-hev-<br>applications |

| Achieving Closed-Loop Accuracy in Open-Loop Current Sensors                                                                                            | Application note regarding current sensor IC solutions that achieve near closed-loop accuracy using open-loop topology                | https://allegromicro.com/en/insights-and-innovations/technical-documents/hall-effect-sensor-ic-publications/achieving-closed-loop-accuracy-in-open-loop-current-sensors                             |

| Allegro Current Sensor ICs Can Take the Heat!<br>Unique Packaging Options for Every Thermal<br>Budget                                                  | Application note regarding current sensors and package selection based on thermal capabilities                                        | https://www.allegromicro.com/-/media/files/<br>application-notes/an296190-current-sensor-<br>thermals.pdf                                                                                           |

| Explanation Of Error Specifications For<br>Allegro Linear Hall-Effect-Based Current Sensor<br>ICs And Techniques For Calculating Total<br>System Error | Application note describing error sources and their effect on the current sensor output                                               | https://www.allegromicro.com/-/media/files/<br>application-notes/an296181-acs72981-error-<br>calculation.pdf                                                                                        |

### **Revision History**

| Number | Date            | Description             |

|--------|-----------------|-------------------------|

| _      | August 17, 2023 | Initial release         |

| 1      | January 5, 2024 | Minor editorial updates |

Copyright 2024, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.