## A8283

## LNB Supply and Control-Voltage Regulator

## **Discontinued Product**

These parts are no longer in production The device should not be purchased for new design applications. Samples are no longer available.

Date of status change: June 21, 2005

#### **Recommended Substitutions:**

For new customers or new applications, refer to the <u>A8282</u>.

NOTE: For detailed information on purchasing options, contact your local Allegro field applications engineer or sales representative.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, revisions to the anticipated product life cycle plan for a product to accommodate changes in production capabilities, alternative product availabilities, or market demand. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

# PRELIMINARY INFORMATION (subject to change without notice) June 18, 2002

Dwa. PP-072A

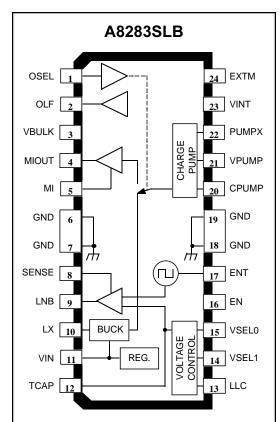

Note that the A8283SB (dual in-line package) and A8283SLB (small-outline IC package) are electrically identical and share a common terminal number assignment.

#### ABSOLUTE MAXIMUM RATINGS

| Supply Voltage, V <sub>IN</sub> 47 V      |

|-------------------------------------------|

| Output Current, I <sub>O</sub> 1.0 A      |

| Logic Input Voltage Range,                |

| V <sub>1</sub> 0.5 V to +7 V              |

| Bypass Switch Current,                    |

| I <sub>SW</sub> Internally Limited        |

| Flag Output Voltage, V <sub>OLF</sub> 7 V |

| Operating Temperature Range,              |

| T <sub>A</sub> 20°C to +85°C              |

| Storage Temperature Range,                |

| $T_{\rm S}$ 40°C to +150°C                |

# LNB SUPPLY AND CONTROL-VOLTAGE REGULATOR

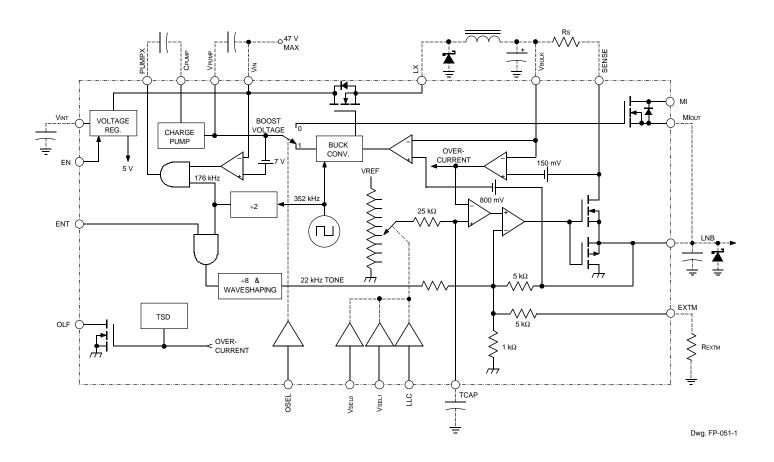

Intended for analog and digital satellite receivers, the low-noise block converter regulator (LNBR) is a monolithic linear and switching voltage regulator designed to provide power and interface signals to the LNB down converter via the coaxial cable. If the device is in stand-by mode (EN terminal LOW), the regulator output is disabled, allowing the antenna downconverters to be supplied or controlled by other satellite receivers sharing the same coaxial cable. Similar two-output LNB supply and control voltage regulators are the A8284SB/SLB.

For slave operation in single-dish dual-receiver systems, the bypass function is implemented by an electronic switch between the master input terminal (MI) and the LNB terminal, leaving all LNB power and control functions to the master receiver. This electronic switch is closed if the device is powered, EN is HIGH, and OSEL is LOW.

The regulator outputs are set to 12, 13, 18, or 20 V by the VSEL terminals. Additionally, it is possible to increase the selected voltage by 1 V to compensate for the voltage drop in the coaxial cable (LLC terminal HIGH). The LNBR combines a tracking switching regulator and low-noise linear regulator. Logic inputs ( $V_{\rm SEL0}$ ,  $V_{\rm SEL1}$ , and LLC) select the desired output voltage. A tracking current-mode buck converter provides the linear regulator with an input voltage that is set to the output voltage plus typically 0.8 V. This maintains constant voltage drop across the linear regulator while permitting adequate voltage range for tone injection.

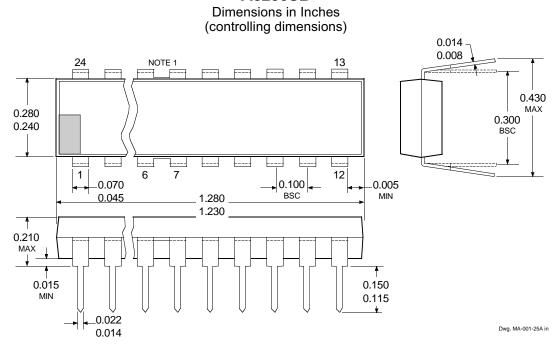

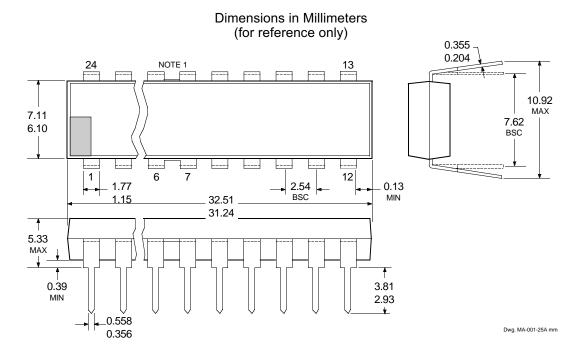

The device is supplied in a 24-pin plastic DIP with batwing tabs (A8283SB), or a 24-lead SOIC power-tab package (A8283SLB). In both cases, the power tab is at ground potential and needs no electrical isolation.

#### **FEATURES**

- Short-Circuit Protected Bypass Function for Slave Operation

- LNB Selection and Stand-By Function

- Built-In Tone Oscillator Factory Trimmed to 22 kHz, Facilitates DiSEqC<sup>TM</sup> (a trademark of EUTELSAT) Encoding

- Full Modulation With No Load

- Tracking Switch-Mode Power Converter for Lowest Dissipation

- Externally Adjustable Short-Circuit Protection

- LNB Short-Circuit Protection and Diagnostics

- Auxiliary Modulation Input

- Cable Length Compensation

- Internal Over-Temperature Protection

This device incorporates features that have patents pending.

Always order by complete part number, e.g., A8283SLB

#### **FUNCTIONAL BLOCK DIAGRAM**

#### **Output Voltage Select Table**

| VSEL1 | LLC                   | $V_{LNB(typ)}$              |

|-------|-----------------------|-----------------------------|

| L     | L                     | 13 V                        |

| L     | Н                     | 14 V                        |

| Н     | L                     | 18 V                        |

| Н     | Н                     | 19 V                        |

| L     | L                     | 12 V                        |

| L     | Н                     | 13 V                        |

| Н     | L                     | 20 V                        |

| Н     | Н                     | 21 V                        |

|       | L<br>H<br>H<br>L<br>L | L L H H L L L H H L L H H L |

## ELECTRICAL CHARACTERISTICS at T $_{\rm A}$ = 70°C, ENT = L, EN = H, OSEL = H, LLC = L, I $_{\rm O}$ = 50 mA (unless otherwise noted).

|                                     |                                 |                                                                                    | Limits               |      |      |       |

|-------------------------------------|---------------------------------|------------------------------------------------------------------------------------|----------------------|------|------|-------|

| Characteristic                      | Symbol                          | Test Conditions                                                                    | Min.                 | Тур. | Max. | Units |

| Supply Voltage                      | V <sub>IN</sub>                 | I <sub>O</sub> = 500 mA, VSEL0 = L, VSEL1 = L, LLC = L                             | 5.5 + V <sub>O</sub> | _    | 47   | V     |

| Output Voltage                      | Vo                              | I <sub>O</sub> = 500 mA, VSEL0 = L, VSEL1 = L, LLC = L                             | 12.5                 | 13   | 13.8 | V     |

|                                     |                                 | I <sub>O</sub> = 500 mA, VSEL0 = L, VSEL1 = L, LLC = H                             | 13.4                 | 14   | 14.9 | V     |

|                                     |                                 | I <sub>O</sub> = 500 mA, VSEL0 = L, VSEL1 = H, LLC = L                             | 17.3                 | 18   | 18.7 | V     |

|                                     |                                 | I <sub>O</sub> = 500 mA, VSEL0 = L, VSEL1 = H, LLC = H                             | 18.2                 | 19   | 19.8 | V     |

|                                     |                                 | I <sub>O</sub> = 500 mA, VSEL0 = H, VSEL1 = L, LLC = L                             | 11.5                 | 12   | 12.8 | V     |

|                                     |                                 | I <sub>O</sub> = 500 mA, VSEL0 = H, VSEL1 = L, LLC = H                             | 12.5                 | 13   | 13.8 | V     |

|                                     |                                 | I <sub>O</sub> = 500 mA, VSEL0 = H, VSEL1 = H, LLC = L                             | 19.2                 | 20   | 20.8 | V     |

|                                     |                                 | I <sub>o</sub> = 500 mA, VSEL0 = H, VSEL1 = H, LLC = H                             | 20.2                 | 21   | 21.8 | V     |

| Load Regulation                     | $\Delta V_{O}$                  | V <sub>O</sub> = 13 or 18 V, I <sub>O</sub> = 50 to 500 mA                         | _                    | 80   | 220  | mV    |

| Current-Limiting Threshold          | V <sub>OM(th)</sub>             |                                                                                    | 125                  | 145  | 160  | mV    |

| Tone Frequency                      | f <sub>tone</sub>               | ENT = H                                                                            | 20                   | 22   | 24   | kHz   |

| Tone Amplitude                      | V <sub>tone(PP)</sub>           | ENT = H, V <sub>O</sub> = 13 or 18 V, I <sub>O</sub> = 500 mA                      | 400                  | 680  | 800  | mV    |

| External Modulation Output          | V <sub>mod(out)</sub>           | ENT = L, $I_O$ = 500 mA, $R_{EXTM}$ = 200 kΩ, $V_{mod(PP)}$ = 130 mV, f = 22 kHz   | 400                  | 500  | 800  | mV    |

| Tone Duty Cycle                     | dc <sub>tone</sub>              | ENT = H                                                                            |                      | 50   | _    | %     |

| Tone Rise or Fall Time              | t <sub>r</sub> , t <sub>f</sub> | ENT = H                                                                            | _                    | 10   |      | μs    |

| External Modulation Gain            | A <sub>mod</sub>                | $R_{EXTM} = 200 \text{ k}\Omega, V_{mod(PP)} = 130 \text{ mV}, f = 22 \text{ kHz}$ | _                    | 4.6  | _    | V/V   |

| External Modulation Input Voltage   | $V_{mod(PP)}$                   | AC coupling                                                                        | _                    | _    | 160  | mV    |

| External Modulation Input Impedance | Z <sub>mod</sub>                | f = 22 kHz                                                                         | 4.0                  | 7.0  | 10   | kΩ    |

continued next page ...

www.allegromicro.com 3

## ELECTRICAL CHARACTERISTICS at $T_A = 25^{\circ}C$ , ENT = L, EN = H, OSEL = H, LLC = L, $V_{IN} = 24 \text{ V}$ , $V_O = 13 \text{ V}$ or 18 V, $I_O = 50 \text{ mA}$ , $R_{EXTM} = \text{open}$ (unless otherwise noted).

|                                           |                   |                                                                    | Limits |       |      |       |

|-------------------------------------------|-------------------|--------------------------------------------------------------------|--------|-------|------|-------|

| Characteristic                            | Symbol            | Test Conditions                                                    | Min.   | Тур.  | Max. | Units |

| Overload Flag Logic Low                   | V <sub>OL</sub>   | I <sub>OL</sub> = 8 mA                                             | _      | 0.28  | 8.0  | V     |

| Overload Flag Leakage Current             | I <sub>oz</sub>   | V <sub>OH</sub> = 6 V                                              | _      | <1.0  | 10   | μΑ    |

| Logic Input Voltage                       | V <sub>IL</sub>   |                                                                    | _      | _     | 8.0  | V     |

|                                           | V <sub>IH</sub>   |                                                                    | 2.0    | _     | _    | V     |

| Logic Input Current                       | I <sub>IL</sub>   | V <sub>IL</sub> = 0 V                                              | _      | <-1.0 | -10  | μΑ    |

|                                           | I <sub>IH</sub>   | V <sub>IH</sub> = 5 V                                              | _      | <1.0  | 10   | μΑ    |

| Supply Current                            | I <sub>IN</sub>   | Output disabled (EN = L)                                           | _      | 0.2   | 1.0  | mA    |

|                                           |                   | Output enabled, ENT = H, I <sub>O</sub> = 0, V <sub>O</sub> = 13 V | _      | 7.5   | 15   | mA    |

| Thermal Shutdown Temp.                    | T <sub>J</sub>    |                                                                    | _      | 165   | _    | °C    |

| Linear Regulator Voltage Drop             | $\Delta V_{BUCK}$ | V <sub>BULK</sub> – V <sub>O</sub>                                 | _      | 8.0   | _    | V     |

| Switching Frequency                       | f <sub>O</sub>    | 16 x f <sub>tone</sub>                                             | 320    | 352   | 384  | kHz   |

| Bypass Switch Current Limit               | l <sub>swM</sub>  | OSEL = L                                                           | 400    | 900   | _    | mA    |

| Bypass Switch Voltage Drop<br>(MI to LNB) | V <sub>sw</sub>   | OSEL = L, I <sub>sw</sub> = 300 mA                                 | _      | 0.15  | _    | V     |

#### **FUNCTIONAL DESCRIPTION**

The ENT (Tone Enable) terminal activates the internal tone signal, modulating the dc output with a  $\pm 0.3$  V, 22 kHz symmetrical waveform. The internal oscillator is factory-trimmed to provide a tone of 22 kHz  $\pm 2$  kHz. No further adjustment is required. The internal oscillator operates the buck converter at 16 times the tone frequency.

Burst coding of the 22 kHz tone can be accomplished due to the fast response of the ENT input and rapid tone response. This allows implementation of the DiSEqC<sup>TM</sup> protocols.

To improve design flexibility and to allow implementation of proposed LNB remote control standards, an analog modulation input terminal is available (EXTM). An appropriate dc-blocking capacitor must be used to couple the modulating signal source to the EXTM terminal. If external modulation is not used, the EXTM terminal should be decoupled with a 0.1 µF capacitor.

Applications that are required to deliver more than 400 mA and use the external modulation terminal should be rebiased to increase the voltage drop across the linear regulator. This will allow full modulation under all conditions.

#### FUNCTIONAL DESCRIPTION (cont'd)

This can be accomplished by connecting a 200 k $\Omega$  resistor from the external modulation terminal (24) to ground. This will reduce the LNB output voltage by typically 300 mV without effecting the  $V_{BULK}$  voltage. The output voltage can be restored to the programmed value by connecting a 1  $M\Omega$  resistor from the  $V_{INT}$  terminal (23) to the  $T_{CAP}$  terminal (12). This raises both  $V_{BULK}$  and  $V_O$  by typically 300 mV.

The output linear regulator will sink and source current. This feature allows full modulation capability into capacitive loads as high as  $0.25~\mu F$ .

The programmed output voltage rise and fall times can be set by an internal 25  $k\Omega$  resistor and an external capacitor located on the TCAP terminal. Typical values are 0.0047  $\mu F$  to 0.047  $\mu F$ . This feature only affects the turn on and programmed voltage rise and fall times. Modulation is unaffected by the choice of TCAP.

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Two terminals are dedicated to the over-current protection/monitoring: SENSE and OLF. The LNB output is current limited. The short-circuit protection threshold is set by the value of an external resistor,  $R_{\rm S}$ , between terminals 3 and 8.  $R_{\rm S} = V_{\rm OM(th)}/I_{\rm OM}$  where  $V_{\rm OM(th)}$  is the current-limiting threshold voltage and  $I_{\rm OM}$  is the desired current limit value. The minimum recommended value for  $R_{\rm S}$  is 0.15  $\Omega$ .

In operation, the short-circuit protection produces current fold-back at the input due to the tracking converter. If the output is shorted, the linear regulator will limit the output current to  $I_{OM}$ . The tracking converter will maintain a constant voltage drop of 0.8 V across the linear regulator. This condition results in typically 550 mW dissipation ( $I_{OM} \times 0.8 \ V$ ). Short-circuit or thermal-shutdown activation will cause the OLF terminal, an open-drain diagnostic output flag, to go LOW.

Thermal resistance:

DIP —  $R_{\theta JA} = 40^{\circ}\text{C/W}$ ,  $R_{\theta JT} = 6^{\circ}\text{C/W}$ , or SOIC —  $R_{\theta JA} = 77^{\circ}\text{C/W}$ ,  $R_{\theta JT} = 6^{\circ}\text{C/W}$ . The device junction temperature should be kept below 150°C. Thermal shut-down circuitry turns off the device if junction temperature exceeds +165°C typically.

$R_{\theta JA}$  is measured on typical two-sided PCB with minimal copper ground area. For the SOIC, adding 3.572 in copper ground area will reduce the thermal resistance to 49°C/W. See Application Note 29501.5, *Improving Batwing Power Dissipation*.

www.allegromicro.com 5

## **TerminalConfiguration**

| Symbol            | Terminal | Function                                                                                                                                            |

|-------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| OSEL              | 1        | Logic input: selects between LNB on (when high) and bypass switch closed (when low)                                                                 |

| OLF               | 2        | Overload flag output: low when $I_O > I_{OM}$ or $I_O > I_{SWM}$ or $T_J > 165$ °C, high when $I_O < I_{OM}$ and $I_O < I_{SWM}$ and $T_J < 130$ °C |

| V <sub>BULK</sub> | 3        | Tracking supply voltage to linear regulators                                                                                                        |

| MI <sub>OUT</sub> | 4        | Output voltage from MI (connect to terminal 9)                                                                                                      |

| MI                | 5        | Master input                                                                                                                                        |

| GND               | 6, 7     | Ground                                                                                                                                              |

| SENSE             | 8        | Current limit setup resistor                                                                                                                        |

| LNB               | 9        | Output voltage (V <sub>O</sub> ) to LNB (connect to terminal 4)                                                                                     |

| LX                | 10       | Inductor drive point                                                                                                                                |

| V <sub>IN</sub>   | 11       | Supply input voltage (minimum, V <sub>LNB</sub> + 2.5 V)                                                                                            |

| TCAP              | 12       | Capacitor for setting the rise and fall time of the outputs                                                                                         |

| LLC               | 13       | Logic input: when high, increases output voltage by 1 V for line length compensation                                                                |

| V <sub>SEL1</sub> | 14       | Logic input: output voltage select                                                                                                                  |

| V <sub>SEL0</sub> | 15       | Logic input: output voltage select                                                                                                                  |

| EN                | 16       | Logic input: when high, enables device                                                                                                              |

| ENT               | 17       | Logic input: when high, enables internal 22 kHz modulation                                                                                          |

| GND               | 18, 19   | Ground                                                                                                                                              |

| C <sub>PUMP</sub> | 20       | High side of charge-pump capacitor                                                                                                                  |

| $V_{PUMP}$        | 21       | Gate supply voltage for high-side drivers                                                                                                           |

| PUMPX             | 22       | Charge-pump drive                                                                                                                                   |

| V <sub>INT</sub>  | 23       | Bypass capacitor for internal voltage reference                                                                                                     |

| EXTM              | 24       | External modulation input                                                                                                                           |

7

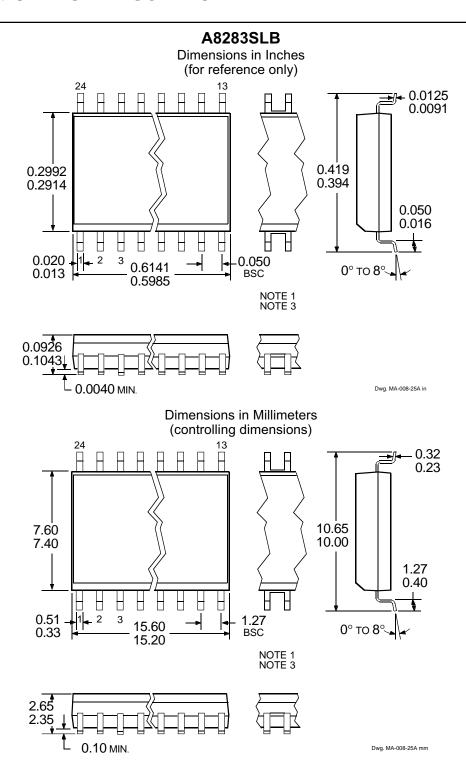

#### A8283SB

- NOTES: 1. Webbed lead frame. Leads 6, 7, 18, and 19 are internally one piece.

- 2. Exact body and lead configuration at vendor's option within limits shown.

- 3. Lead spacing tolerance is non-cumulative.

- 4. Lead thickness is measured at seating plane or below.

- 5. Supplied in standard sticks/tubes of 15 devices.

www.allegromicro.com

- NOTES: 1. Exact body and lead configuration at vendor's option within limits shown.

- 2. Lead spacing tolerance is non-cumulative.

- 3. Webbed lead frame. Leads 6, 7, 18, and 19 are internally one piece.

- 4. Supplied in standard sticks/tubes of 31 devices or add "TR" to part numbr for tape and reel.