# 80 V Automotive Half-Bridge MOSFET Driver

## FEATURES AND BENEFITS

- Half-bridge MOSFET driver

- Bootstrap gate drive for N-channel MOSFET bridge

- Independent control of high-side and low-side gate drives with cross-conduction capability

- Charge pump regulator for low supply voltage operation

- 5.5 to 80 V supply voltage operating range

- Integrated logic I/O supply

- SPI-compatible serial interface

- Bridge control by direct logic inputs or serial interface

- Programmable gate drive

- Current sense amplifier

- Programmable diagnostics

- AEC-Q100 Grade 0 qualified

- ASIL-Compliant: ASIL B safety element out-of-context (SEooC) developed in accordance with ISO 26262, when used as specified in the safety manual

ISO 26262

ASIL Compliant

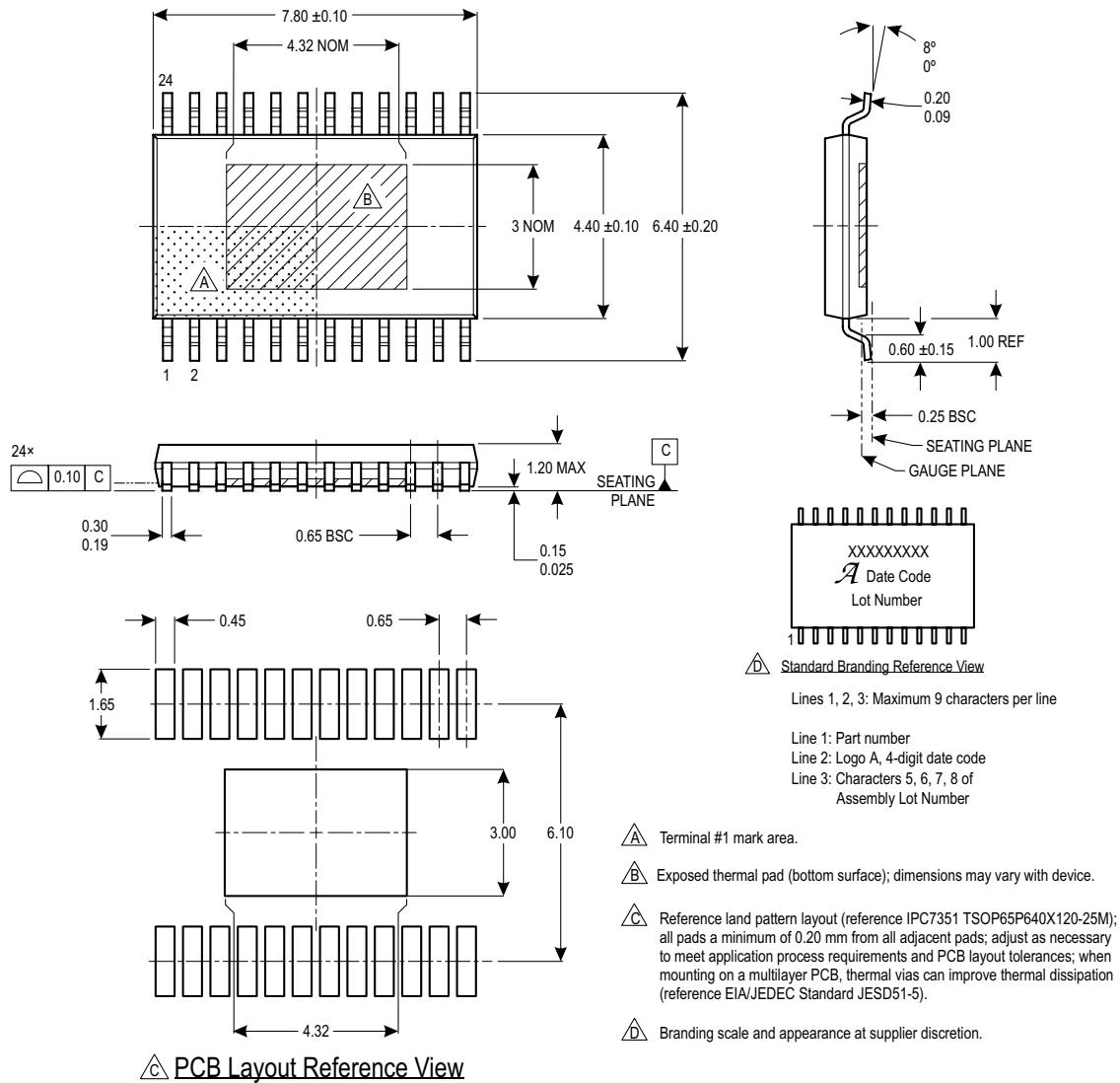

## PACKAGE:

24-lead TSSOP with exposed pad (suffix LP)

*Not to scale*

## DESCRIPTION

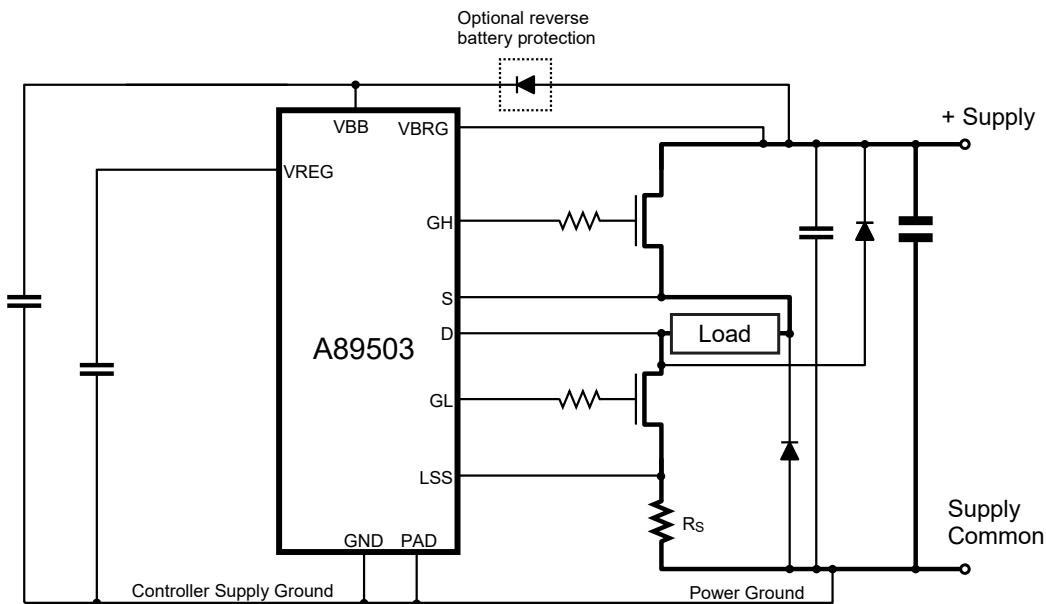

The A89503 is an N-channel power MOSFET driver capable of controlling MOSFETs connected in a half-bridge arrangement and is specifically designed for automotive applications with high-power inductive loads, such as brush DC motors, BLDC motors, VR/SR motors, solenoids, and actuators.

A unique charge pump regulator provides full gate drive over the full supply voltage range from 5.5 to 80 V for most applications. A bootstrap capacitor is used to provide the above-battery supply voltage required for N-channel MOSFETs.

Each MOSFET can be independently controlled by logic-level inputs or through the SPI-compatible serial interface. Fully independent control allows both external FETs to be turned on at the same time.

Integrated diagnostics provide indication of multiple internal faults, system faults, and power bridge faults, and can be configured to protect the power MOSFETs under most short circuit conditions.

In addition to providing full access to the bridge control, the serial interface is also used to alter programmable settings such as VDS threshold and fault blank time. Detailed diagnostic information can be read through the serial interface.

The A89503 was developed in accordance with ISO 26262 as a hardware safety element out-of-context with ASIL B capability for use in automotive safety-related systems when integrated and used in the manner prescribed in the applicable safety manual and datasheet.

The A89503 is supplied in a 24-lead eTSSOP (suffix LP). This package is lead (Pb) free, with 100% matte-tin leadframe plating (suffix -T).

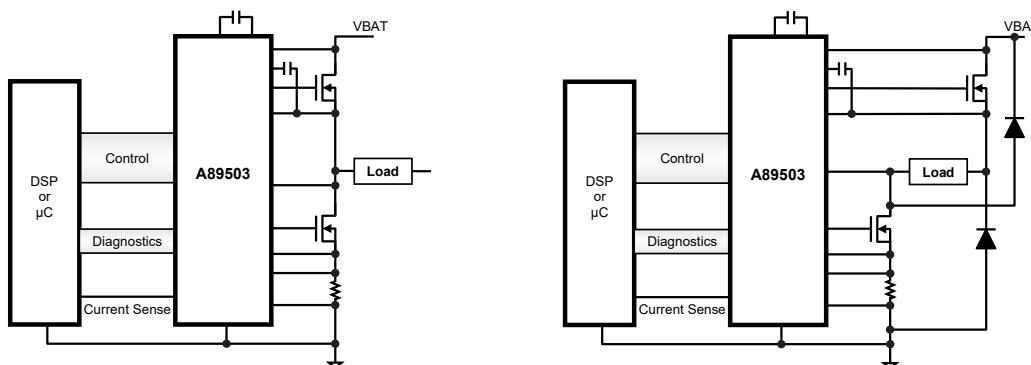

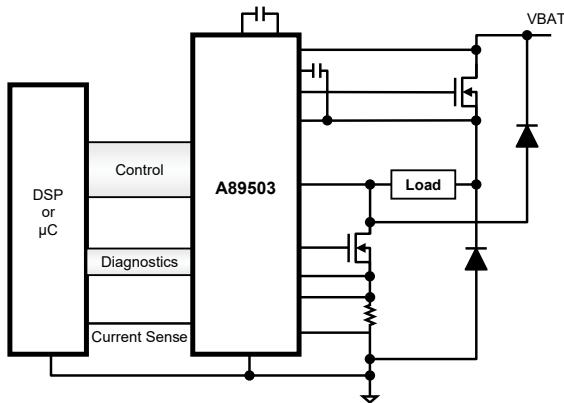

Figure 1: Typical Applications

## SELECTION GUIDE

| Part Number      | I/O Logic | Packing              | Package                                                                      |

|------------------|-----------|----------------------|------------------------------------------------------------------------------|

| A89503KL PTR-3-1 | 3.3 V     | 4000 pieces per reel | 7.8 mm × 4.4 mm, 1.2 mm max height<br>24-lead TSSOP with exposed thermal pad |

| A89503KL PTR-5-1 | 5 V       |                      |                                                                              |

ABSOLUTE MAXIMUM RATINGS <sup>[1]</sup>

| Characteristic                          | Symbol       | Notes                                                                                                                            | Rating                             | Unit |

|-----------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------|

| Load Supply Voltage                     | $V_{BB}$     |                                                                                                                                  | −0.3 to 80                         | V    |

| Regulator Output                        | $V_{REG}$    | VREG                                                                                                                             | −0.3 to 16                         | V    |

| Charge Pump Capacitor Terminal          | $V_{CP1}$    | CP1                                                                                                                              | −0.3 to 16                         | V    |

| Charge Pump Capacitor Terminal          | $V_{CP2}$    | CP2                                                                                                                              | $V_{CP1} - 0.3$ to $V_{REG} + 0.3$ | V    |

| Battery-Compliant Logic Input Terminals | $V_{IB}$     | HS, LSn, RESETn, ENABLE                                                                                                          | −0.3 to 80                         | V    |

| Logic Input Terminals                   | $V_I$        | STRn, SCK, SDI                                                                                                                   | −0.3 to 6                          | V    |

| Logic Output Terminal                   | $V_O$        | SDO                                                                                                                              | −0.3 to 6                          | V    |

| Diagnostics Output                      | $V_{DIAG}$   | DIAG                                                                                                                             | −0.3 to 80                         | V    |

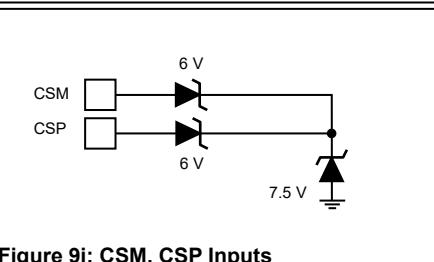

| Sense Amplifier Inputs                  | $V_{CSI}$    | CSP, CSM                                                                                                                         | −4 to 6.5                          | V    |

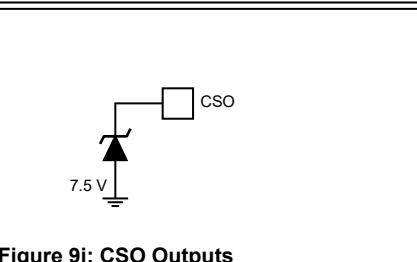

| Sense Amplifier Output                  | $V_{CSO}$    | CSO                                                                                                                              | −0.3 to 6                          | V    |

| Bridge Drain Monitor Terminal           | $V_{BRG}$    | VBRG                                                                                                                             | −5 to 85                           | V    |

| Bootstrap Supply Terminal               | $V_C$        | C                                                                                                                                | −0.3 to $V_{REG} + 80$             | V    |

| High-Side Gate Drive Output Terminal    | $V_{GH}$     | GH                                                                                                                               | $V_C - 16$ to $V_C + 0.3$          | V    |

|                                         |              | GH (transient)                                                                                                                   | −18 to $V_C + 0.3$                 | V    |

| High-Side Source (Load) Terminal        | $V_S$        | S                                                                                                                                | $V_C - 16$ to $V_C + 0.3$          | V    |

|                                         |              | S (transient)                                                                                                                    | −18 to $V_C + 0.3$                 | V    |

| Low-Side Drain (Load) Terminal          | $V_D$        | D                                                                                                                                | −16 to $V_S$                       | V    |

| Low-Side Gate Drive Output Terminal     | $V_{GL}$     | GL                                                                                                                               | $V_{REG} - 16$ to 18               | V    |

|                                         |              | GL (transient)                                                                                                                   | −8 to 18                           | V    |

| Bridge Low-Side Source Terminal         | $V_{LSS}$    | LSS                                                                                                                              | $V_{REG} - 16$ to 18               | V    |

|                                         |              | LSS (transient)                                                                                                                  | −8 to 18                           | V    |

| Ambient Operating Temperature Range     | $T_A$        | Limited by power dissipation                                                                                                     | −40 to 150                         | °C   |

| Maximum Continuous Junction Temperature | $T_{J(max)}$ |                                                                                                                                  | 165                                | °C   |

| Transient Junction Temperature          | $T_{Jt}$     | Overtemperature event not exceeding 10 seconds, lifetime duration not exceeding 10 hours, guaranteed by design characterization. | 180                                | °C   |

| Storage Temperature Range               | $T_{stg}$    |                                                                                                                                  | −55 to 150                         | °C   |

[1] With respect to GND. Ratings apply when no other circuit operating constraints are present.

## Table of Contents

|                                              |    |                                              |    |

|----------------------------------------------|----|----------------------------------------------|----|

| Features and Benefits.....                   | 1  | Gate Drive Control .....                     | 18 |

| Description.....                             | 1  | Logic Control Inputs .....                   | 19 |

| Package .....                                | 1  | Output Disable.....                          | 19 |

| Typical Application .....                    | 1  | Sleep Mode.....                              | 19 |

| Selection Guide.....                         | 2  | Current Sense Amplifier.....                 | 20 |

| Absolute Maximum Ratings .....               | 2  | Diagnostic Monitors.....                     | 20 |

| Thermal Characteristics .....                | 3  | DIAG Output .....                            | 20 |

| Pinout Diagram and Terminal List Table ..... | 4  | Status and Diagnostic Registers .....        | 21 |

| Functional Block Diagram .....               | 5  | Chip-Level Protection .....                  | 21 |

| Electrical Characteristics.....              | 6  | Operational Monitors .....                   | 22 |

| Supply and Reference .....                   | 6  | Power Bridge and Load Faults.....            | 23 |

| Gate Output Drive.....                       | 7  | Fault Action .....                           | 26 |

| Logic Inputs and Outputs .....               | 8  | Fault Masks .....                            | 27 |

| Logic I/O – Dynamic Parameters.....          | 8  | Serial Interface.....                        | 28 |

| Current Sense Amplifier .....                | 9  | Configuration Registers .....                | 30 |

| Diagnostics and Protection.....              | 10 | Stop On Fault Register .....                 | 30 |

| Timing Diagrams .....                        | 12 | Diagnostic Registers .....                   | 30 |

| Logic Truth Tables.....                      | 14 | Control Register.....                        | 30 |

| Functional Description .....                 | 15 | Status Register .....                        | 31 |

| Input and Output Terminal Functions .....    | 15 | Serial Register Reference.....               | 32 |

| Power Supplies.....                          | 16 | Application Information .....                | 40 |

| Pump Regulator.....                          | 16 | Bootstrap Capacitor Selection .....          | 40 |

| Gate Drives .....                            | 16 | Bootstrap Charging .....                     | 40 |

| Operational Configurations.....              | 16 | VREG Capacitor Selection .....               | 40 |

| Bootstrap Supply .....                       | 17 | Current Sense Amplifier Configuration .....  | 41 |

| Bootstrap Charge Cycle Considerations.....   | 17 | Current Sense Amplifier Output Signals ..... | 41 |

| Top-Off Charge Pump.....                     | 17 | Input/Output Structures.....                 | 42 |

| High-Side Gate Drive.....                    | 17 | Layout Recommendations .....                 | 43 |

| Low-Side Gate Drive .....                    | 18 | Package Outline Drawing .....                | 44 |

| Gate Drive Passive Pull-Down.....            | 18 |                                              |    |

### THERMAL CHARACTERISTICS: May require derating at maximum conditions

| Characteristic             | Symbol          | Test Conditions [2]                                    | Value | Unit |

|----------------------------|-----------------|--------------------------------------------------------|-------|------|

| Package Thermal Resistance | $R_{\theta JA}$ | 4-layer PCB based on JEDEC standard                    | 28    | °C/W |

|                            |                 | 2-layer PCB with 3.8 in. <sup>2</sup> copper each side | 38    | °C/W |

|                            | $R_{\theta JP}$ |                                                        | 2     | °C/W |

[2] Additional thermal information available on the Allegro website.

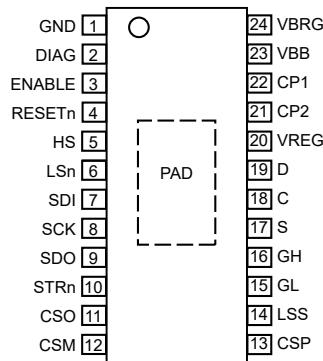

## PINOUT DIAGRAM AND TERMINAL LIST TABLE

**24-Lead eTSSOP (suffix LP)

Pinout Diagram**

Terminal List Table

| Name   | Number | Function                          |

|--------|--------|-----------------------------------|

| C      | 18     | Bootstrap Capacitor               |

| CP1    | 22     | Pump Capacitor CCP Connection     |

| CP2    | 21     | Pump Capacitor CCP Connection     |

| CSM    | 12     | Current Sense Amp -Input          |

| CSO    | 11     | Current Sense Amp Output          |

| CSP    | 13     | Current Sense Amp +Input          |

| DIAG   | 2      | Diagnostic Output                 |

| ENABLE | 3      | Gate drive output control Input   |

| GH     | 16     | High-side Gate Drive Output       |

| GL     | 15     | Low-side Gate Drive Output        |

| GND    | 1      | Power Ground                      |

| HS     | 5      | High-side control Input           |

| LSn    | 6      | Low-side control Input            |

| LSS    | 14     | Low-side Source                   |

| D      | 19     | Low-side Drain Connection         |

| RESETn | 4      | Standby Mode Control Input        |

| S      | 17     | Load Connection                   |

| SCK    | 8      | Serial Clock Input                |

| SDI    | 7      | Serial Data Input                 |

| SDO    | 9      | Serial Data Output                |

| STRn   | 10     | Serial Strobe (chip select) Input |

| VBB    | 23     | Main Power Supply                 |

| VBRG   | 24     | High-side Drain voltage sense     |

| VREG   | 20     | Regulated gate drive supply       |

| PAD    | —      | Thermal pad; connect to GND       |

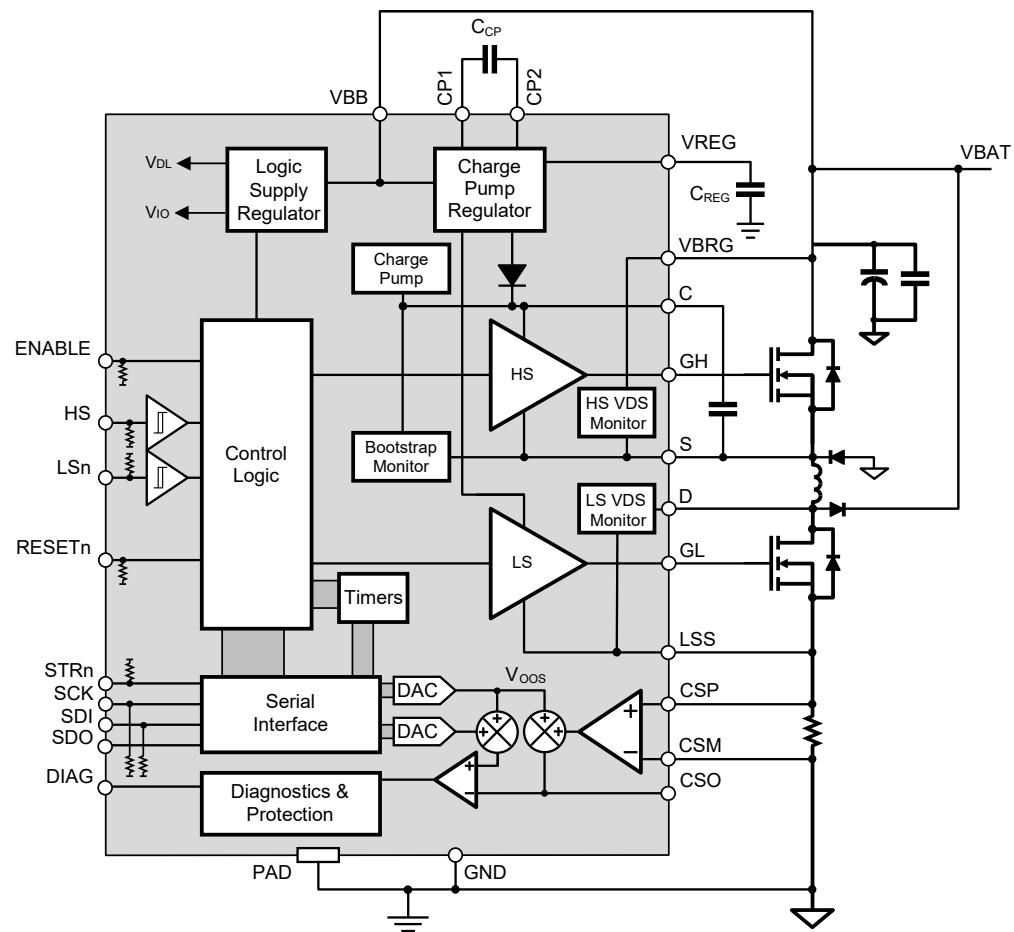

Figure 2: Functional Block Diagram

**ELECTRICAL CHARACTERISTICS:** Valid for  $T_J = -40$  to  $150^\circ\text{C}$ ,  $V_{BB} = 5.5$  to  $80$  V, unless otherwise specified

| Characteristics                                | Symbol      | Test Conditions                                                       | Min. | Typ. | Max. | Unit             |

|------------------------------------------------|-------------|-----------------------------------------------------------------------|------|------|------|------------------|

| <b>SUPPLY AND REFERENCE</b>                    |             |                                                                       |      |      |      |                  |

| VBB Functional Operating Range                 | $V_{BB}$    | Operating; outputs active                                             | 5.5  | —    | 80   | V                |

|                                                |             | Operating; outputs disabled                                           | 5    | —    | 80   | V                |

|                                                |             | No unsafe states                                                      | 0    | —    | 80   | V                |

| VBB Quiescent Current                          | $I_{BBQ}$   | RESETn = high, $V_{BB} = 48$ V,<br>All gate drive outputs low         | —    | 8    | 20   | mA               |

|                                                | $I_{BBS}$   | RESETn $\leq 300$ mV, sleep mode, $V_{BB} < 70$ V                     | —    | —    | 30   | $\mu\text{A}$    |

| Internal Logic Supply Regulator Voltage [3][4] | $V_{DL}$    |                                                                       | 3.1  | 3.3  | 3.5  | V                |

| Logic I/O Regulator Voltage [3][4]             | $V_{IO}$    | A89503KL PTR-3                                                        | 3    | 3.3  | 3.6  | V                |

|                                                |             | A89503KL PTR-5; $V_{BB} > 6$ V                                        | 4.5  | 5    | 5.5  | V                |

| VREG Output Voltage                            | $V_{REG}$   | $6.5 \text{ V} < V_{BB}$ , $I_{VREG} = 0$ to $33$ mA                  | 9    | 11   | 11.7 | V                |

|                                                |             | $6 \text{ V} < V_{BB} \leq 6.5 \text{ V}$ , $I_{VREG} = 0$ to $20$ mA | 9    | 11   | 11.7 | V                |

|                                                |             | $5.5 \text{ V} < V_{BB} \leq 6 \text{ V}$ , $I_{VREG} = 0$ to $15$ mA | 9    | 11   | 11.7 | V                |

| Bootstrap Diode Forward Voltage                | $V_{FBOOT}$ | $I_D = 10$ mA                                                         | 0.4  | 0.7  | 1.0  | V                |

|                                                |             | $I_D = 100$ mA                                                        | 1.35 | 2.2  | 2.8  | V                |

| Bootstrap Diode Current Limit                  | $I_{DBOOT}$ |                                                                       | 250  | 500  | 750  | mA               |

| Top-Off Charge Pump Current Limit              | $I_{TOCPM}$ |                                                                       | 43   | 100  | —    | $\mu\text{A}$    |

| High-Side Gate Drive Static Load Resistance    | $R_{GSH}$   |                                                                       | 250  | —    | —    | $\text{k}\Omega$ |

| System Clock Period                            | $t_{osc}$   |                                                                       | 45   | 50   | 55   | ns               |

Continued on the next page...

**ELECTRICAL CHARACTERISTICS (continued):** Valid for  $T_J = -40$  to  $150^\circ\text{C}$ ,  $V_{BB} = 5.5$  to  $80$  V, unless otherwise specified

| Characteristics                         | Symbol          | Test Conditions                                                             | Min.             | Typ. | Max.             | Unit             |

|-----------------------------------------|-----------------|-----------------------------------------------------------------------------|------------------|------|------------------|------------------|

| <b>GATE OUTPUT DRIVE</b>                |                 |                                                                             |                  |      |                  |                  |

| Turn-On Time (High-Side)                | $t_{r(HS)}$     | $C_{LOAD} = 15 \text{ nF}$ , 2 V to 8 V, $V_C - V_S = 11 \text{ V}$         | 86               | 235  | 434              | ns               |

| Turn-On Time (Low-Side)                 | $t_{r(LS)}$     | $C_{LOAD} = 15 \text{ nF}$ , 2 V to 8 V, $V_{REG} - V_{LSS} = 11 \text{ V}$ | 86               | 235  | 434              | ns               |

| Turn-Off Time (High-Side)               | $t_{f(HS)}$     | $C_{LOAD} = 15 \text{ nF}$ , 8 V to 2 V, $V_C - V_S = 11 \text{ V}$         | 44               | 97   | 205              | ns               |

| Turn-Off Time (Low-Side)                | $t_{f(LS)}$     | $C_{LOAD} = 15 \text{ nF}$ , 8 V to 2 V, $V_{REG} - V_{LSS} = 11 \text{ V}$ | 44               | 97   | 205              | ns               |

| Pull-Up Peak Source Current (High-Side) | $I_{PUPK(HS)}$  | $V_C - V_S = 11 \text{ V}$                                                  | -1150            | -    | -250             | mA               |

| Pull-Up Peak Source Current (Low-Side)  | $I_{PUPK(LS)}$  | $V_{REG} - V_{LSS} = 11 \text{ V}$                                          | -1150            | -    | -250             | mA               |

| Pull-Up On Resistance                   | $R_{DS(on)UP}$  | $T_J = 25^\circ\text{C}$ , $I_{GH} = -150 \text{ mA}$ <sup>[1]</sup>        | 5.6              | -    | 15.6             | $\Omega$         |

|                                         |                 | $T_J = 150^\circ\text{C}$ , $I_{GH} = -150 \text{ mA}$ <sup>[1]</sup>       | 9.1              | -    | 23.9             | $\Omega$         |

| Pull-Down Peak Sink Current (High-Side) | $I_{PDPK(HS)}$  | $V_C - V_S = 11 \text{ V}$                                                  | 570              | -    | 2100             | mA               |

| Pull-Down Peak Sink Current (Low-Side)  | $I_{PDPK(LS)}$  | $V_{REG} - V_{LSS} = 11 \text{ V}$                                          | 570              | -    | 2100             | mA               |

| Pull-Down On Resistance                 | $R_{DS(on)DN}$  | $T_J = 25^\circ\text{C}$ , $I_{GL} = 150 \text{ mA}$                        | 1.25             | -    | 2.8              | $\Omega$         |

|                                         |                 | $T_J = 150^\circ\text{C}$ , $I_{GL} = 150 \text{ mA}$                       | 2.1              | -    | 4.7              | $\Omega$         |

| Turn-On Time Set Point Range            | $t_R$           |                                                                             | 60               | -    | 300              | ns               |

| Minimum Turn-On Time                    | $t_{RM}$        | $TR = 0$                                                                    | 45               | 60   | 75               | ns               |

| Turn-On Time Mean Step Size             | $t_{RS}$        | $TR > 0$                                                                    | 12               | 16   | 22               | ns               |

| Turn-On Current I1                      | $I_{R1}$        | $V_{GS} = 0 \text{ V}$ , $IR1 = 15$                                         | -511             | -120 | -86              | mA               |

|                                         |                 | Programmable set point range                                                | -8               | -    | -120             | mA               |

| Turn-On Current I2                      | $I_{R2}$        | $V_{GS} = 0 \text{ V}$ , $IR2 = 15$                                         | -511             | -120 | -86              | mA               |

|                                         |                 | Programmable set point range                                                | -8               | -    | -120             | mA               |

| Turn-Off Time Set Point Range           | $t_F$           |                                                                             | 60               | -    | 300              | ns               |

| Minimum Turn-Off Time                   | $t_{FM}$        | $TF = 0$                                                                    | 45               | 60   | 75               | ns               |

| Turn-Off Time Mean Step Size            | $t_{FS}$        | $TF > 0$                                                                    | 12               | 16   | 22               | ns               |

| Turn-Off Current I1                     | $I_{F1}$        | $V_{GS} = 9 \text{ V}$ , $IF1 = 15$                                         | 84               | 120  | 148              | mA               |

|                                         |                 | Programmable set point range                                                | 8                | -    | 120              | mA               |

| Turn-Off Current I2                     | $I_{F2}$        | $V_{GS} = 9 \text{ V}$ , $IF2 = 15$                                         | 84               | 120  | 148              | mA               |

|                                         |                 | Programmable set point range                                                | 8                | -    | 120              | mA               |

| GH Output Voltage High                  | $V_{GHH}$       | Bootstrap capacitor fully charged                                           | $V_C - 0.02$     | -    | -                | V                |

| GH Output Voltage Low                   | $V_{GHL}$       | $-10 \mu\text{A} < I_{GH} < 10 \mu\text{A}$                                 | -                | -    | $V_S + 0.02$     | V                |

| GL Output Voltage High                  | $V_{GLH}$       |                                                                             | $V_{REG} - 0.02$ | -    | -                | V                |

| GL Output Voltage Low                   | $V_{GLL}$       | $-10 \mu\text{A} < I_{GL} < 10 \mu\text{A}$                                 | -                | -    | $V_{LSS} + 0.02$ | V                |

| GH Passive Pull-Down                    | $R_{GHPD}$      | $V_{GH} - V_S = 0.1 \text{ V}$                                              | 0.25             | -    | 1.8              | $\text{M}\Omega$ |

| GL Passive Pull-Down                    | $R_{GLPD}$      | $V_{GL} - V_{LSS} = 0.1 \text{ V}$                                          | 0.25             | -    | 1.8              | $\text{M}\Omega$ |

| GH Active Pull-Down                     | $R_{GHPA}$      | $V_{C-S} > 4 \text{ V}$                                                     | 0.7              | -    | 20               | $\Omega$         |

| GL Active Pull-Down                     | $R_{GLPA}$      | $V_{VREG-LSS} > 4 \text{ V}$                                                | 0.7              | -    | 20               | $\Omega$         |

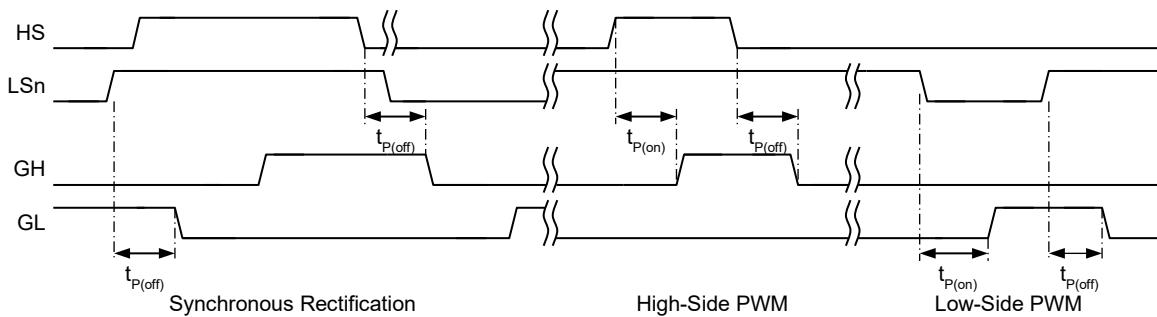

| Turn-Off Propagation Delay              | $t_{P(off)}$    | Input Change to unloaded Gate output change (Figure 5)                      | 30               | -    | 103              | ns               |

| Turn-On Propagation Delay               | $t_{P(on)}$     | Input Change to unloaded Gate output change (Figure 5)                      | 30               | -    | 103              | ns               |

| Propagation Delay Matching (On-to-Off)  | $\Delta t_{OO}$ |                                                                             | -                | -    | 25               | ns               |

| Propagation Delay Matching (GH-to-GL)   | $\Delta t_{HL}$ | Same state change                                                           | -                | -    | 25               | ns               |

Continued on the next page...

**ELECTRICAL CHARACTERISTICS (continued):** Valid for  $T_J = -40$  to  $150^\circ\text{C}$ ,  $V_{BB} = 5.5$  to  $80$  V, unless otherwise specified

| Characteristics                        | Symbol       | Test Conditions                            | Min.                | Typ. | Max.                | Unit |

|----------------------------------------|--------------|--------------------------------------------|---------------------|------|---------------------|------|

| <b>LOGIC INPUT AND OUTPUTS</b>         |              |                                            |                     |      |                     |      |

| Input Low Voltage                      | $V_{IL}$     | Except RESETn                              | —                   | —    | $0.3 \times V_{IO}$ | V    |

|                                        |              | RESETn                                     | —                   | —    | 0.8                 | V    |

| Input High Voltage                     | $V_{IH}$     | Except RESETn                              | $0.7 \times V_{IO}$ | —    | —                   | V    |

|                                        |              | RESETn                                     | 2.4                 | —    | —                   | V    |

| Input Hysteresis                       | $V_{Ihys}$   | Except RESETn                              | 250                 | 550  | —                   | mV   |

|                                        |              | RESETn                                     | 200                 | 500  | —                   | mV   |

| Input Pull-Down HS, ENABLE, RESETn     | $R_{PD}$     | $0 < V_{IN} < V_{IO}$                      | —                   | 50   | —                   | kΩ   |

|                                        |              | $V_{IO} < V_{IN} < 80$ V                   | —                   | 100  | —                   | μA   |

| Input Pull-Up LSn                      | $R_{PD}$     | $0 < V_{IN} < V_{IO}$                      | —                   | 50   | —                   | kΩ   |

|                                        |              | $V_{IO} < V_{IN} < 80$ V                   | —                   | 100  | —                   | μA   |

| Input Pull-Down SDI, SCK               | $R_{PDS}$    | $0 < V_{IN} < V_{IO}$                      | —                   | 50   | —                   | kΩ   |

| Input Pull-Up STRn (to $V_{IO}$ )      | $R_{PUS}$    |                                            | —                   | 50   | —                   | kΩ   |

| Output Low Voltage                     | $V_{OL}$     | $I_{OL} = 1$ mA                            | —                   | 0.2  | 0.4                 | V    |

| Output High Voltage                    | $V_{OHS}$    | $I_{OS} = -1$ mA <sup>[1]</sup>            | $V_{IO} - 0.4$      | —    | —                   | V    |

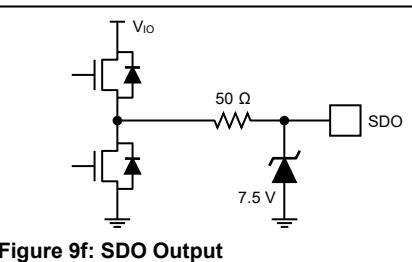

| Output Leakage SDO <sup>[1]</sup>      | $I_{OS}$     | $0$ V $< V_{OS} < V_{IO}$ , STRn = 1       | —1                  | —    | 1                   | μA   |

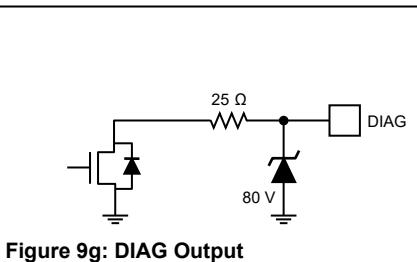

| Output Current Limit (DIAG)            | $I_{OLDLIM}$ | $0$ V $< V_{OD} < 12$ V, DIAG active       | —                   | 10   | 17                  | mA   |

|                                        |              | $18$ V $\leq V_{OD} < 80$ V, DIAG active   | —                   | —    | 2.5                 | mA   |

| Output Leakage <sup>[1]</sup> (DIAG)   | $I_{OD}$     | $0$ V $< V_{OD} < 12$ V, DIAG inactive     | —1                  | —    | 1                   | μA   |

|                                        |              | $18$ V $\leq V_{OD} < 80$ V, DIAG inactive | —                   | —    | 2.5                 | mA   |

| <b>LOGIC I/O – DYNAMIC PARAMETERS</b>  |              |                                            |                     |      |                     |      |

| Reset Pulse Width                      | $t_{RST}$    |                                            | 0.5                 | —    | 4.5                 | μs   |

| Reset Shutdown Time                    | $t_{RSD}$    |                                            | 30                  | —    | —                   | μs   |

| Input Pulse Filter Time                | $t_{PIN}$    | HS, LSn                                    | —                   | 35   | —                   | ns   |

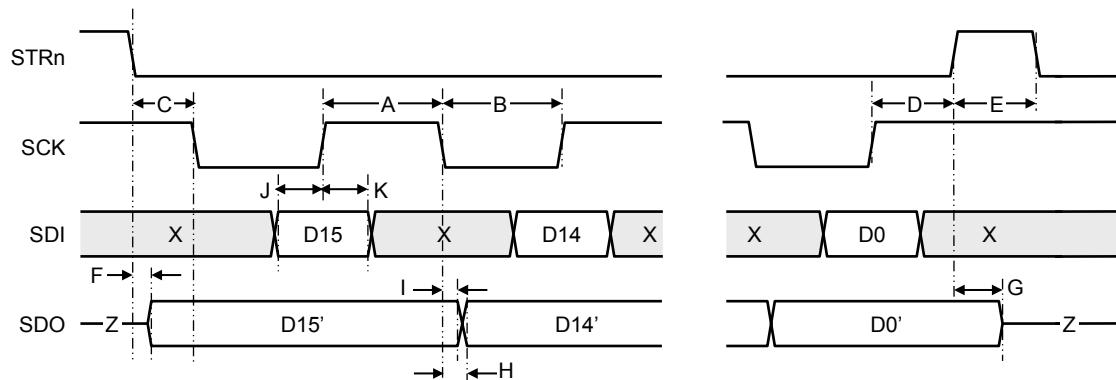

| Clock High Time                        | $t_{SCKH}$   | A in Figure 4                              | 50                  | —    | —                   | ns   |

| Clock Low Time                         | $t_{SCKL}$   | B in Figure 4                              | 50                  | —    | —                   | ns   |

| Strobe Lead Time                       | $t_{STLD}$   | C in Figure 4                              | 100                 | —    | —                   | ns   |

| Strobe Lag Time                        | $t_{STLG}$   | D in Figure 4                              | 30                  | —    | —                   | ns   |

| Strobe High Time                       | $t_{STRH}$   | E in Figure 4                              | 350                 | —    | —                   | ns   |

| Data Out Enable Time                   | $t_{SDOE}$   | F in Figure 4, $C_{LOAD} = 10$ pF          | —                   | —    | 40                  | ns   |

| Data Out Disable Time                  | $t_{SDOD}$   | G in Figure 4                              | —                   | —    | 30                  | ns   |

| Data Out Valid Time From Clock Falling | $t_{SDOV}$   | H in Figure 4, $C_{LOAD} = 10$ pF          | —                   | —    | 40                  | ns   |

| Data Out Hold Time From Clock Falling  | $t_{SDOH}$   | I in Figure 4                              | 5                   | —    | —                   | ns   |

| Data In Set-Up Time To Clock Rising    | $t_{SDIS}$   | J in Figure 4                              | 15                  | —    | —                   | ns   |

| Data In Hold Time From Clock Rising    | $t_{SDIH}$   | K in Figure 4                              | 10                  | —    | —                   | ns   |

| Wake Up From Sleep                     | $t_{EN}$     | $C_{CP} = 2.2$ μF, $C_{REG} = 10$ μF       | —                   | —    | 3                   | ms   |

Continued on the next page...

**ELECTRICAL CHARACTERISTICS (continued):** Valid for  $T_J = -40$  to  $150^\circ\text{C}$ ,  $V_{BB} = 5.5$  to  $80$  V, unless otherwise specified

| Characteristics                              | Symbol           | Test Conditions                                                                               | Min. | Typ.    | Max. | Unit                         |

|----------------------------------------------|------------------|-----------------------------------------------------------------------------------------------|------|---------|------|------------------------------|

| <b>CURRENT SENSE AMPLIFIER</b>               |                  |                                                                                               |      |         |      |                              |

| Input Offset Voltage                         | $V_{IOS}$        | $-1.5 \text{ V} < V_{CM} < 2 \text{ V}$                                                       | -10  | -       | 10   | mV                           |

| Input Offset Voltage Drift Over Temperature  | $\Delta V_{IOS}$ |                                                                                               | -    | $\pm 4$ | -    | $\mu\text{V}/^\circ\text{C}$ |

| Input Bias Current [1]                       | $I_{BIAS}$       | $V_{ID} = 0 \text{ V}$ , $V_{CM}$ in range                                                    | -50  | -       | 5    | $\mu\text{A}$                |

| Input Offset Current [1]                     | $I_{OS}$         | $V_{ID} = 0 \text{ V}$ , $V_{CM}$ in range                                                    | -1.5 | -       | +1.5 | $\mu\text{A}$                |

| Input Common-Mode Range (DC)                 | $V_{CM}$         | $V_{ID} = 0 \text{ V}$                                                                        | -1.5 | -       | +2   | V                            |

| Gain                                         | $A_V$            | Default power-up value                                                                        | -    | 35      | -    | V/V                          |

|                                              |                  | Programmable range, SAG[2:0], nominal                                                         | 10   | -       | 50   | V/V                          |

| Gain Error                                   | $E_A$            | $V_{CM}$ in range                                                                             | -1.6 | -       | +1.6 | %                            |

| Output Offset                                | $V_{OOS}$        | Default power-up value                                                                        | -    | 2.5     | -    | V                            |

|                                              |                  | Programmable range, SAO[3:0], nominal                                                         | 0    | -       | 2.5  | V                            |

| Output Offset Error                          | $E_{VO}$         | $V_{CM}$ in range, $V_{OOS} > 0 \text{ V}$                                                    | -10  | $\pm 2$ | +10  | %                            |

| Small Signal -3 dB Bandwidth at Gain = 25    | $BW$             | $V_{IN} = 10 \text{ mV}_{pp}$                                                                 | 2    | -       | -    | MHz                          |

| Output Settling Time (to within 40 mV)       | $t_{SET}$        | $V_{CSO} = 1 \text{ V}_{pp}$ square wave, Gain = 20, $C_{OUT} = 50 \text{ pF}$                | -    | -       | 1    | $\mu\text{s}$                |

| Output Dynamic Range                         | $V_{CSOUT}$      | $-100 \mu\text{A} < I_{CSO} < 100 \mu\text{A}$                                                | 0.3  | -       | 4.8  | V                            |

| Output Voltage Clamp                         | $V_{CSC}$        | $I_{CSO} = -2 \text{ mA}$                                                                     | 4.9  | 5.2     | 5.7  | V                            |

| Output Current Sink [1]                      | $I_{CSsink}$     | $V_{ID} = 0 \text{ V}$ , $V_{CSO} = 1.5 \text{ V}$ , Gain = 20                                | 230  | -       | 470  | $\mu\text{A}$                |

| Output Current Sink (Boosted) [1][5]         | $I_{CSsinkb}$    | $V_{OOS} = 1.5 \text{ V}$ , $V_{ID} = -50 \text{ mV}$ , $V_{CSO} = 1.5 \text{ V}$ , Gain = 20 | 1.8  | -       | 4.4  | mA                           |

| Output Current Source [1]                    | $I_{CSsource}$   | $V_{OOS} = 0 \text{ V}$ , $V_{ID} = 200 \text{ mV}$ , $V_{CSO} = 1.5 \text{ V}$ , Gain = 20   | -5.5 | -       | -1.8 | mA                           |

| VBB Supply Ripple Rejection Ratio            | $PSRR$           | $V_{ID} = 0 \text{ V}$ , 100 kHz, Gain = 20                                                   | 56   | 65      | -    | dB                           |

|                                              |                  | $V_{CSP} = V_{CSM} = 0 \text{ V}$ , DC, Gain = 20                                             | 77   | -       | -    | dB                           |

| DC Common-Mode Rejection Ratio               | $CMRR$           | $V_{CM}$ step from 0 to 200 mV, Gain = 20                                                     | 52   | 100     | -    | dB                           |

| AC Common-Mode Rejection Ratio               | $CMRR$           | $V_{CM} = 200 \text{ mV}_{pp}$ , 100 kHz, Gain = 20                                           | -    | 62      | -    | dB                           |

|                                              |                  | $V_{CM} = 200 \text{ mV}_{pp}$ , 1 MHz, Gain = 20                                             | -    | 43      | -    | dB                           |

|                                              |                  | $V_{CM} = 200 \text{ mV}_{pp}$ , 10 MHz, Gain = 20                                            | -    | 25      | -    | dB                           |

| Common Mode Recovery Time (to within 100 mV) | $t_{CMrec}$      | $V_{CM}$ step from $-4 \text{ V}$ to $+1 \text{ V}$ , Gain = 20, $C_{OUT} = 50 \text{ pF}$    | -    | -       | 2.1  | $\mu\text{s}$                |

| Output Slew Rate 10% to 90%                  | $SR$             | $V_{ID}$ step from 0 to 175 mV, Gain = 20, $C_{OUT} = 50 \text{ pF}$                          | 1.8  | -       | -    | $\text{V}/\mu\text{s}$       |

| Input Overload Recovery (to within 40 mV)    | $t_{IDrec}$      | $V_{ID}$ step from 250 mV to 0 V, Gain = 20, $C_{OUT} = 50 \text{ pF}$                        | -    | -       | 2.1  | $\mu\text{s}$                |

Continued on the next page...

**ELECTRICAL CHARACTERISTICS (continued):** Valid for  $T_J = -40$  to  $150^\circ\text{C}$ ,  $V_{BB} = 5.5$  to  $80$  V, unless otherwise specified

| Characteristics                               | Symbol         | Test Conditions                                                                       | Min.              | Typ.            | Max.              | Unit    |

|-----------------------------------------------|----------------|---------------------------------------------------------------------------------------|-------------------|-----------------|-------------------|---------|

| <b>DIAGNOSTICS AND PROTECTION</b>             |                |                                                                                       |                   |                 |                   |         |

| VREG Undervoltage                             | $V_{RON}$      | $V_{REG}$ rising                                                                      | 7.6               | 7.95            | 8.3               | V       |

|                                               | $V_{ROFF}$     | $V_{REG}$ falling                                                                     | 6.9               | 7.2             | 7.5               | V       |

| VREG Overvoltage Warning                      | $V_{ROV}$      | $V_{REG}$ rising                                                                      | 15.2              | 15.9            | 16.6              | V       |

| VREG Overvoltage Hysteresis                   | $V_{ROVHys}$   |                                                                                       | 1130              | 1500            | 1850              | mV      |

| VBRG Overvoltage Warning Threshold            | $V_{BRGOV}$    | VPO = 0, $V_{BRG}$ rising                                                             | 52                | 54              | 58                | V       |

|                                               |                | VPO = 1, $V_{BRG}$ rising                                                             | 57                | 60              | 63                | V       |

| VBRG Overvoltage Hysteresis                   | $V_{BRGOVHys}$ |                                                                                       | 1.9               | 2.8             | 3.6               | V       |

| VBRG Undervoltage Threshold                   | $V_{BRGUV}$    | VPU = 0, $V_{BRG}$ falling                                                            | 18                | 19              | 20                | V       |

|                                               |                | VPU = 1, $V_{BRG}$ falling                                                            | 32                | 34              | 36                | V       |

| VBRG Undervoltage Hysteresis                  | $V_{BRGUvhys}$ |                                                                                       | 1.2               | 1.6             | 1.9               | V       |

| VBB POR Voltage                               | $V_{BBR}$      | $V_{BB}$                                                                              | —                 | —               | 3.8               | V       |

| Bootstrap Undervoltage                        | $V_{BCUV}$     | $V_{BOOT}$ rising, $V_{BOOT} = V_C - V_S$                                             | 6.2               | 7               | 8.5               | V       |

|                                               |                | $V_{BOOT}$ falling, $V_{BOOT} = V_C - V_S$                                            | 5.15              | 6               | 7.1               | V       |

| Gate Drive Undervoltage Warning HS            | $V_{GSHUV}$    | $V_{GSH}$ falling                                                                     | $V_{BOOT} - 1.35$ | $V_{BOOT} - 1$  | $V_{BOOT} - 0.85$ | V       |

| Gate Drive Undervoltage Warning LS            | $V_{GSLUV}$    | $V_{GSL}$ falling                                                                     | $V_{REG} - 1.35$  | $V_{REG} - 1$   | $V_{REG} - 0.85$  | V       |

| Off-State Gate Drive Overvoltage Warning HS   | $V_{GSHOV}$    | $V_{GSH}$ rising                                                                      | $V_S + 0.85$      | $V_S + 1.2$     | $V_S + 1.8$       | V       |

| Off-State Gate Drive Overvoltage Warning LS   | $V_{GSLOV}$    | $V_{GSL}$ rising                                                                      | $V_{LSS} + 0.85$  | $V_{LSS} + 1.2$ | $V_{LSS} + 1.8$   | V       |

| VIO Undervoltage Threshold                    | $V_{IOON}$     | A89503KL PTR-3, $V_{IO}$ rising                                                       | 2.8               | 2.9             | 3.1               | V       |

|                                               | $V_{IOOFF}$    | A89503KL PTR-3, $V_{IO}$ falling                                                      | 2.4               | 2.6             | 2.8               | V       |

|                                               | $V_{IOON}$     | A89503KL PTR-5, $V_{IO}$ rising                                                       | 4.3               | 4.5             | 4.7               | V       |

|                                               | $V_{IOOFF}$    | A89503KL PTR-5, $V_{IO}$ falling                                                      | 3.7               | 3.9             | 4.1               | V       |

| VBRG Input Voltage                            | $V_{BRG}$      | When VDS monitor is active                                                            | 5.5               | $V_{BB}$        | 80                | V       |

| VBRG Input Current                            | $I_{VBRG}$     | $V_{DSTH}$ = default, $V_{BB} = 12$ V                                                 | —                 | —               | 5                 | mA      |

|                                               | $I_{VBRGQ}$    | Sleep mode $V_{BB} < 70$ V                                                            | —                 | —               | 5                 | $\mu$ A |

| VDS Threshold – High Side                     | $V_{DSTH}$     | Default power-up value                                                                | —                 | 1.2             | —                 | V       |

|                                               |                | Programmable range, $7\text{ V} \leq V_{BRG} < 80\text{ V}$                           | 0                 | —               | 3.15              | V       |

|                                               |                | Programmable range VT[5:0]<br>$5.5\text{ V} \leq V_{BRG} < 7\text{ V}$ <sup>[6]</sup> | 0                 | —               | 2.5               | V       |

|                                               |                | High-side on, $V_{DSTH} \geq 1\text{ V}$ , $V_{BRG} > 7\text{ V}$                     | -200              | $\pm 100$       | 200               | mV      |

| High-Side VDS Threshold Offset <sup>[2]</sup> | $V_{DSTHO}$    | High-side on, $V_{DSTH} < 1\text{ V}$                                                 | -150              | $\pm 50$        | 150               | mV      |

|                                               |                | Default power-up value                                                                | —                 | 1.2             | —                 | V       |

| VDS Threshold – Low Side                      | $V_{DSTL}$     | Programmable range, $V_{BB} \geq 5.5\text{ V}$ <sup>[6]</sup>                         | 0                 | —               | 3.15              | V       |

|                                               |                | Default power-up value                                                                | —                 | 1.2             | —                 | V       |

| Low-Side VDS Threshold Offset <sup>[2]</sup>  | $V_{DSTLO}$    | Low-side on, $V_{DSTL} \geq 1\text{ V}$ , $V_{BRG} > 7\text{ V}$                      | -200              | $\pm 100$       | 200               | mV      |

|                                               |                | Low-side on, $V_{DSTL} < 1\text{ V}$                                                  | -150              | $\pm 50$        | 150               | mV      |

Continued on the next page...

**ELECTRICAL CHARACTERISTICS (continued):** Valid for  $T_J = -40$  to  $150^\circ\text{C}$ ,  $V_{BB} = 5.5$  to  $80$  V, unless otherwise specified

| Characteristics                               | Symbol       | Test Conditions                                 | Min.  | Typ.  | Max.   | Unit             |

|-----------------------------------------------|--------------|-------------------------------------------------|-------|-------|--------|------------------|

| <b>DIAGNOSTICS AND PROTECTION (CONTINUED)</b> |              |                                                 |       |       |        |                  |

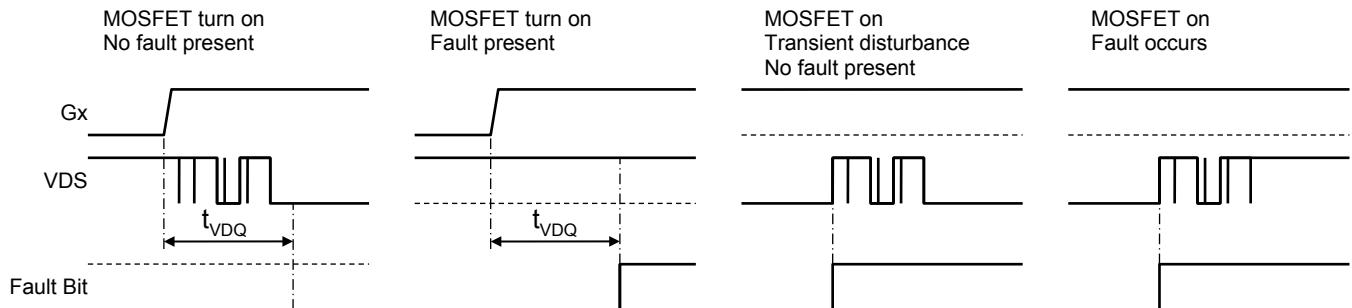

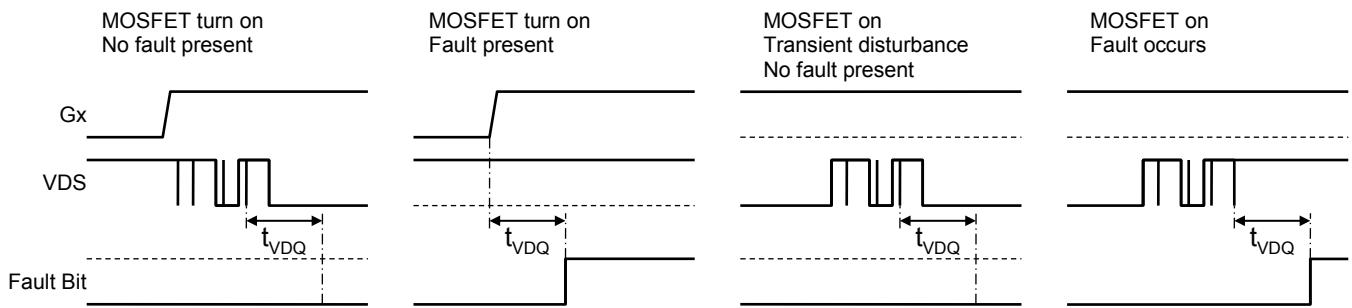

| VDS and VGS Qualify Time                      | $t_{VDQ}$    | Default power-up value (Figure 6)               | 86.96 | 102.3 | 117.65 | $\mu\text{s}$    |

|                                               |              | Programmable range $\text{TVD}[9:0]$ , nominal  | 0     | —     | 102.3  | $\mu\text{s}$    |

| Overcurrent Voltage                           | $V_{OCT}$    | Default power-up value                          | 0.45  | 0.6   | 0.75   | V                |

|                                               |              | Programmable range, $\text{OCT}[3:0]$ , nominal | 0.3   | —     | 4.8    | V                |

| Overcurrent Qualify Time                      | $t_{OCQ}$    |                                                 | 6.75  | 8.6   | 9.45   | $\mu\text{s}$    |

| Temperature Warning Threshold [7]             | $T_{JWH}$    | Temperature increasing                          | 125   | 135   | 145    | $^\circ\text{C}$ |

| Temperature Warning Hysteresis [7]            | $T_{JWHhys}$ | Recovery = $T_{JWH} - T_{JWHhys}$               | —     | 15    | —      | $^\circ\text{C}$ |

| Overtemperature Threshold [7]                 | $T_{JF}$     | Temperature increasing                          | 165   | 175   | 185    | $^\circ\text{C}$ |

| Overtemperature Hysteresis [7]                | $T_{JHys}$   | Recovery = $T_{JF} - T_{JHys}$                  | —     | 15    | —      | $^\circ\text{C}$ |

[1] For input and output current specifications, negative current is defined as coming out of (being sourced by) the specified device terminal.

[2] VDS offset is the difference between the programmed threshold,  $V_{DSTH}$  or  $V_{DSTL}$  and the actual trip voltage.

[3] VIO, VDL derived from VBB for internal use only. VDL not accessible on any device terminal.

[4] Verified by design and characterization. Not production tested.

[5] If the amplifier output voltage ( $V_{CSO}$ ) is more positive than the value demanded by the applied differential input ( $V_{ID}$ ) and output offset ( $V_{OOS}$ ) conditions, then output current sink capability is boosted to enhance negative-going transient response.

[6] Maximum value of VDS threshold that should be set in the configuration registers for correct operation when  $V_{BRG}$  is within the stated range.

[7] Stated values confirmed by design and characterization (not production tested). Associated function production tested.

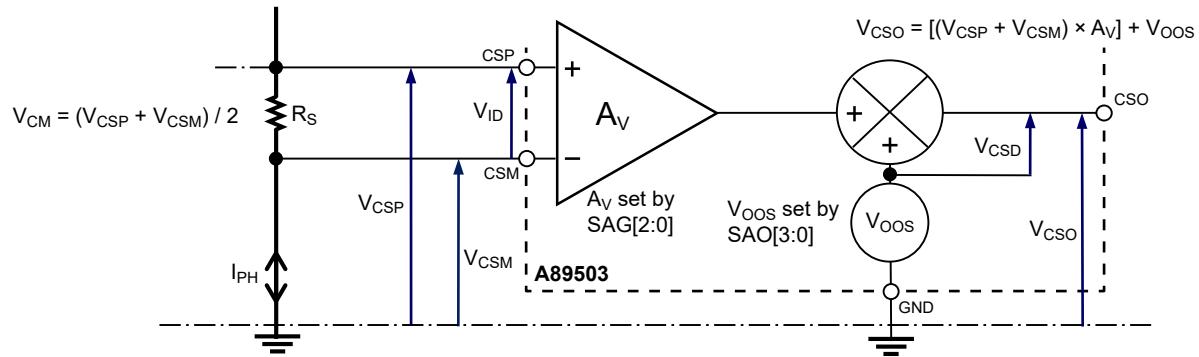

Figure 3: Sense Amplifier Voltage Definitions

Figure 4: Serial Interface Timing (X = don't care, Z = high impedance (tri-state))

Figure 5: Gate Drive Timing – Control Inputs

Figure 6a: VDS Fault Monitor – Blank Mode Timing (VDQ = 1)

Figure 6b: VDS Fault Monitor – Debounce Mode Timing (VDQ = 0)

## LOGIC TRUTH TABLES

Table 1: Control Logic (Control by Logic Inputs)

| HS | LSn | GH | GL | S                 |

|----|-----|----|----|-------------------|

| 0  | 1   | LO | LO | Z                 |

| 0  | 0   | LO | HI | LO                |

| 1  | 1   | HI | LO | HI                |

| 1  | 0   | HI | HI | HI <sup>[1]</sup> |

HI = high-side FET active

LO = low-side FET active

Z = high impedance, both FETs off

All control register bits set to 0, RESETn = 1, ENABLE = 1

[1] Load connection assumed between S terminal and drain of low-side MOSFET.

Table 2: Control Logic (Control by Serial Register)

| HSR | LSR | GH | GL | S                 |

|-----|-----|----|----|-------------------|

| 0   | 0   | LO | LO | Z                 |

| 0   | 1   | LO | HI | LO                |

| 1   | 0   | HI | LO | HI                |

| 1   | 1   | HI | HI | HI <sup>[1]</sup> |

HI = high-side FET active

LO = low-side FET active

Z = high impedance, both FETs off

HS = 0, LSn = 1, RESETn = 1, ENABLE = 1

[1] Load connection assumed between S terminal and drain of low-side MOSFET.

Table 3: Control combination logic table – Logic Inputs and Serial Register

| Terminal | Register | Internal |

|----------|----------|----------|

| HS       | HSR      | HI       |

| 0        | 0        | 0        |

| 0        | 1        | 1        |

| 1        | 0        | 1        |

| 1        | 1        | 1        |

| Terminal | Register | Internal |

|----------|----------|----------|

| LSn      | LSR      | LO       |

| 1        | 0        | 0        |

| 1        | 1        | 1        |

| 0        | 0        | 1        |

| 0        | 1        | 1        |

| ENABLE | HI | LO | GH | GL | S                | Comment          |

|--------|----|----|----|----|------------------|------------------|

| 1      | 0  | 0  | L  | L  | Z                | Bridge Disabled  |

| 1      | 0  | 1  | L  | H  | LO               | Bridge Sinking   |

| 1      | 1  | 0  | H  | L  | HI               | Bridge Sourcing  |

| 1      | 1  | 1  | H  | H  | U <sup>[1]</sup> | Cross-Conduction |

| 0      | X  | X  | L  | L  | Z                | Bridge Disabled  |

RESETn = 1

HI = high-side FET active

LO = low-side FET active

X = don't care

Z = high impedance, both FETs off

U = undefined, both FETs on

Internal control signals (HI, LO) are derived by combining the logic states applied to the control input terminals (HS, LSn) with the bit patterns held in the Control register (HSR, LSR).

Normally the input terminals or the Control register method is used for control with the other being held inactive (all terminals or bits at logic 0).

[1] If the MOSFETs are configured as a half bridge the state of S will be undefined.

If the load is connected between the S terminal and drain of low-side MOSFET then S will be HI

## FUNCTIONAL DESCRIPTION

The A89503 is a half-bridge (H-bridge) MOSFET driver (pre-driver) requiring a single unregulated supply of 5.5 to 80 V. It includes an integrated linear regulator to supply the internal logic. All logic inputs are compatible with 3.3 V logic (A89503KL PTR-3) or 5 V logic (A89503KL PTR-5) depending on part number selection.

The two high-current gate drives are capable of driving a wide range of N-channel power MOSFETs, and are configured as a half-bridge driver with one high-side drive and one low-side drive. The A89503 provides all necessary circuits to ensure that the gate-source voltage of both high-side and low-side external FETs are above 10 V, at supply voltages down to 7 V. For extreme battery voltage drop conditions, correct functional operation is guaranteed at supply voltages down to 5.5 V, but with a reduced gate drive voltage.

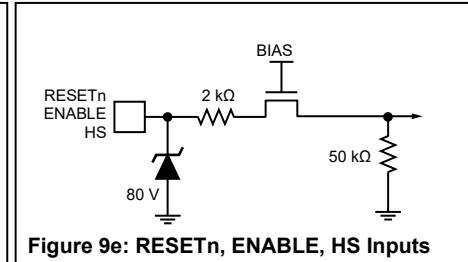

Gate drives can be controlled directly through the logic input terminals or through an SPI-compatible serial interface. Fully independent control allows both external FETs to be turned on at the same time. All logic inputs, except RESETn, are standard CMOS levels and can be compatible with 3.3 V (A89503KL PTR-3) or 5 V (A89503KL PTR-5) logic outputs depending on part number selection. The logic inputs are battery voltage compliant, meaning they can be shorted to ground or supply without damage, up to the maximum battery voltage of 80 V.

A low-power sleep mode allows the A89503, the power bridge, and the load to remain connected to a vehicle battery supply without the need for an additional supply switch.

The A89503 includes several diagnostic features to provide indication and/or protection against undervoltage, overtemperature, and power bridge faults. A single diagnostic output provides basic fault indication and detailed diagnostic information is available through the serial interface. The serial interface also provides access to programmable fault blanking time and programmable VDS threshold for short detection.

The A89503 includes a low-side current sense amplifier with programmable gain and offset. The amplifier is specifically designed for current sensing in the presence of high voltage and current transients.

### Input and Output Terminal Functions

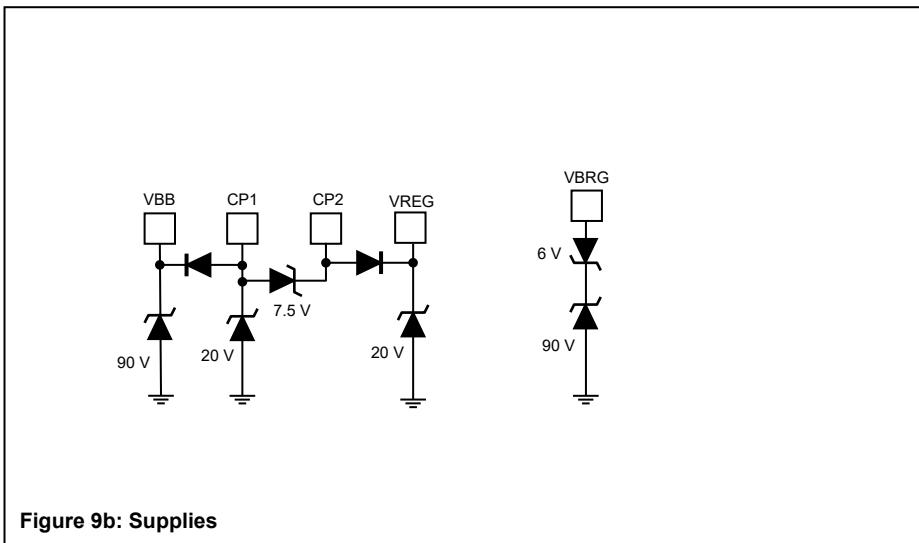

**VBB:** Main power supply for internal regulators and charge pump. The main power supply should be connected to VBB through a reverse voltage protection circuit and should be decoupled with ceramic capacitors connected close to the supply and ground terminals.

**VBRG:** Sense input to the top of the external MOSFET bridge. Allows accurate measurement of the voltage at the drain of the high-side MOSFET in the bridge.

**CP1, CP2:** Pump capacitor connection for charge pump. Connect a ceramic capacitor with a recommended nominal value of 2.2  $\mu$ F between CP1 and CP2. This should have a rated working voltage of at least 25 V and a tolerance of  $\pm 20\%$  or better.

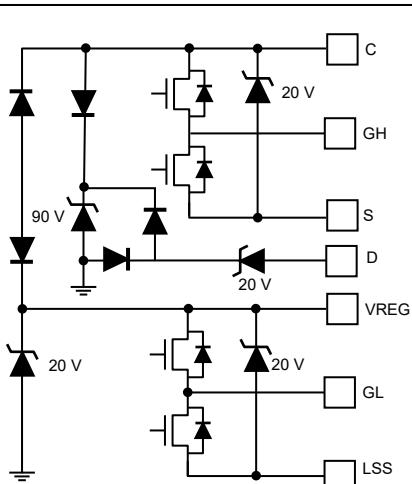

**VREG:** Regulated voltage, 11 V, used to supply the low-side gate drivers and to provide current for the above supply charge pump. A sufficiently large storage capacitor must be connected to this terminal to provide the required transient charging current.

**GND:** Analog, digital, and power ground. Connect to supply ground—see Layout Recommendations.

**C:** High-side connection for the bootstrap capacitor and positive supply for the high-side gate driver.

**GH:** High-side, gate-drive output for an external N-channel MOSFET.

**S:** Source connection for high-side MOSFET providing the negative supply connections for the floating high-side driver.

**GL:** Low-side gate-drive output for an external N-channel MOSFET.

**LSS:** Low-side return path for discharge of the capacitance on the low-side MOSFET gate, connected to the source of the low-side external MOSFET independently through a low-impedance track.

**HS:** Logic inputs with pull-down to control the high-side gate drive. Battery voltage compliant terminal.

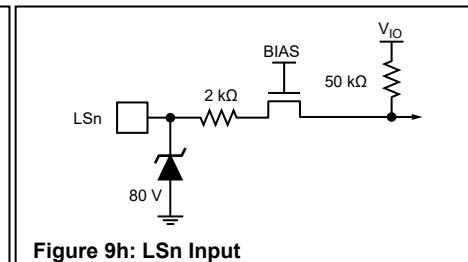

**LSn:** Logic input with pull-up to control the low-side gate drive. Active-low input. Battery voltage compliant terminal.

**ENABLE:** Logic input to enable the gate drive outputs. Battery voltage compliant terminal.

**RESETn:** Clears latched fault states that may have disabled the outputs when taken low for the reset pulse width,  $t_{RST}$ . Forces low-power shutdown (sleep) when held low for more than the RESET shutdown time,  $t_{RSD}$ . Battery voltage compliant terminal.

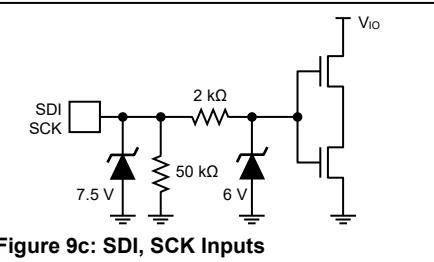

**SDI:** Serial data logic input with pull-down. 16-bit serial word input msb first.

**SDO:** Serial data output. High impedance when STRn is high. Outputs bit 15 of the diagnostic register, the fault flag, as soon as STRn goes low.

**SCK:** Serial clock logic input with pull-down. Data is latched in from SDI on the rising edge of SCK. There must be 16 rising edges per write and SCK must be held high when STRn changes.

**STRn:** Serial data strobe and serial access enable logic input with pull-up. When STRn is high, any activity on SCK or SDI is ignored and SDO is high impedance, allowing multiple SDI slaves to have common SDI, SCK, and SDO connections.

**CSP, CSM:** Current sense amplifier inputs.

**CSO:** Current sense amplifier output.

**D:** Drain connection for low-side MOSFET.

**DIAG:** Diagnostic output. Provides general fault flag output.

## Power Supplies

A single power supply voltage is required. The main power supply,  $V_{BB}$ , should be connected to VBB through a reverse voltage protection circuit. A 100 nF ceramic decoupling capacitor must be connected close to the supply and ground terminals.

A low power independent internal regulator provides the supply voltage,  $V_{DL}$ , to the internal logic. A second integrated linear regulator provides the supply voltage,  $V_{IO}$ , to all logic inputs and push-pull outputs. This digital I/O is set to 3.3 V (A89503KL PTR-3) or 5 V (A89503KL PTR-5).

All internal logic is guaranteed to operate correctly to below the regulator undervoltage levels, ensuring that the A89503 will continue to operate safely until all logic is reset when a power-on-reset state is present.

The A89503 will operate within specified parameters with  $V_{BB}$  from 7 to 80 V and will function correctly with a supply down to 5.5 V. This provides a rugged solution for use in the harsh automotive environment.

## Pump Regulator

The gate drivers are powered by an internal regulator which limits the supply to the drivers and therefore the maximum gate voltage. This regulator uses a charge pump scheme with switching frequency of 62.5 kHz. At low supply voltage, the regulated supply is maintained by a charge pump boost converter which requires a pump capacitor connected between the CP1 and CP2 terminals. This capacitor should have a nominal value of 2.2  $\mu$ F, rated working voltage of at least 25 V, and a tolerance of  $\pm 20\%$

or better. At supply voltage greater than 14 V, the pump regulator stops boosting and becomes a linear regulator.

The regulated voltage,  $V_{REG}$ , is available on the VREG terminal. A sufficiently large storage capacitor (see Applications section) must be connected to this terminal to provide the transient charging current to the low side drivers and the bootstrap capacitors.

## Gate Drives

The A89503 is designed to drive external, low on-resistance, power N-channel MOSFETs. It will supply the large transient currents necessary to quickly charge and discharge the external MOSFET gate capacitance in order to reduce dissipation in the external MOSFET during switching. The charge current for the low-side drive is provided by the capacitor on the VREG terminal. The charge current for the high-side drives is provided by the bootstrap capacitor connected between the C and S terminals. MOSFET gate charge and discharge rates may be controlled by setting a group of parameters via the serial interface or by using an external gate resistor between the gate drive output and the gate terminal of the MOSFET.

## Operational Configurations

The high-side and low-side gate drives are completely independent. The A89503 permits any combination of active high-side and low-side MOSFETs and does not provide any lockout or internally generated dead time. This allows the A89503 to be used in a complementary half-bridge configuration or to drive independent high-side and low-side MOSFETs.

In a simple half-bridge configuration, this allows more precise control of the timing of the MOSFET switching. In some circumstances, simultaneous activation of both high-side and low-side MOSFETs can be used to reduce diode conduction during synchronous rectification, which improves overall efficiency and reduces electromagnetic emissions. The precise timing and any required dead time must be provided by the external controller.

An example of independent driving is to use one gate drive output as a PWM control and the other as an on-off control. For example, the low-side drive can be used to enable current flow through the load and the high-side drive can be used to provide PWM current control. This example is shown in Figure 7. The low-side MOSFET enables or disables the flow of current, and the high-side MOSFET is used with the low-side recirculation diode to provide PWM current control.

Figure 7: PWM Load current control

## Bootstrap Supply

When the high-side drivers are active, the reference voltage for the driver will rise to close to the bridge supply voltage. The supply to the driver will then have to be above the bridge supply voltage to ensure that the driver remains active. This temporary high-side supply is provided by a bootstrap capacitor connected between the bootstrap supply terminal, C, and the high-side reference terminal, S.

The bootstrap capacitor is independently charged to approximately  $V_{REG}$  when the associated reference S terminal is low. When the output swings high, the voltage on the bootstrap supply terminal rises with the output to provide the boosted gate voltage needed for the high-side N-channel power MOSFETs.

## Bootstrap Charge Cycle Considerations

The user must ensure that the bootstrap capacitor does not become discharged below the bootstrap undervoltage threshold,  $V_{BCUV}$ , or a bootstrap fault will be indicated and the outputs disabled. This can happen if the S terminal is not low enough for a long enough period to charge the bootstrap capacitor—for example, when the PWM duty cycles is very high and the charge time for the bootstrap capacitor is insufficient to ensure a sufficient recharge to match the MOSFET gate charge transfer during turn on.

If for any reason the bootstrap capacitor cannot be sufficiently charged, a bootstrap fault will occur—see Diagnostics section for further details.

Note that when the A89503 is used in the configuration shown in Figure 7 with an inductive load, the bootstrap capacitor is

charged in two ways depending on the current flowing in the load.

When no current is flowing in the load, the high-side MOSFET will be off and the bootstrap capacitor can be charged directly through the load by turning on the low-side MOSFET. This procedure should be followed before the first attempt to turn on the high-side MOSFET.

When current is flowing in the load and is controlled by PWM switching the high-side MOSFET, the bootstrap capacitor is charged through the load during a PWM off time. During the PWM off time, the current will continue to flow through the load inductance, pulling the voltage at the S terminal to a negative value in order to forward bias the recirculation diode.

## Top-Off Charge Pump

If the high-side MOSFET is used as an enabling switch—for example, with a simple resistive load or when using low-side PWM switching—then once the MOSFET has been switched on, it will be held in the on state by an additional charge pump in the A89503 referred to as the “top-off” charge pump.

The top-off charge pump will allow the high-side drive to maintain the gate voltage on the external MOSFET indefinitely if required. This is a low current trickle charge pump and is only operated after a high side has been turned on. A small amount of bias current is drawn from the C terminal to operate the floating high-side circuit and the charge pump simply provides enough drive to ensure the bootstrap voltage, and hence the gate voltage, will not droop due to this bias current.

In some applications, a safety resistor is added between the gate and source of each MOSFET in the bridge. When a high-side MOSFET is held in the on state, the current through the associated high-side gate-source resistor ( $R_{GSH}$ ) is provided by the high side driver and therefore appears as a static resistive load on the top-off charge pump. The minimum value of  $R_{GSH}$  for which the top-off charge pump can provide current, without dropping below the bootstrap undervoltage threshold, is defined in the Electrical Characteristics table.

In all cases, the charge required for initial turn-on of the high-side gate is always supplied by the bootstrap capacitor. If the bootstrap capacitor becomes discharged, the top-off charge pump alone will not provide sufficient current to allow the MOSFET to turn on.

## High-Side Gate Drive

A high-side gate-drive output for external N-channel MOSFETs is provided on the GH terminal. GH = 1 (or “high”) means that

the upper half of the driver is turned on and its drain will source current to the gate of the high-side MOSFET in the external load-driving bridge, turning it on.  $GH = 0$  (or “low”) means that the lower half of the driver is turned on and its drain will sink current from the external MOSFET’s gate circuit to the S terminal, turning it off.

The reference point for the high-side drive is the load connections, S. This terminal senses the voltage at the load connections. This terminal is also connected to the negative side of the bootstrap capacitor and is the negative supply reference connections for the floating high-side driver. The discharge current from the high-side MOSFET gate capacitance flows through these connections which should have low-impedance traces to the MOSFET bridge.

### Low-Side Gate Drive

The low-side gate-drive output on GL is referenced to the LSS terminal. This output is designed to drive an external N-channel power MOSFET.  $GL = 1$  (or “high”) means that the upper half of the driver is turned on and its drain will source current to the gate of the low-side MOSFET in the external power bridge, turning it on.  $GL = 0$  (or “low”) means that the lower half of the driver is turned on and its drain will sink current from the external MOSFET’s gate circuit to the LSS terminal, turning it off.

The LSS terminal provides the return path for discharge of the capacitance on the low-side MOSFET gate. This terminal is connected independently to the source of the low-side external MOSFETs through a low-impedance track.

An integrated slew control feature allows the MOSFET gate charge and discharge rates to be controlled via the serial interface as detailed in the Gate Drive Control section.

Either the internal slew control or an external resistor between the gate drive output and the gate connection to the MOSFET (as close as possible to the MOSFET) can be used to control the slew rate seen at the gate, thereby controlling the  $di/dt$  and  $dv/dt$  of the voltage at the S terminal.

### Gate Drive Passive Pull-Down

Each gate drive output includes a discharge circuit to ensure that any external MOSFET connected to the gate drive output is held off when the power is removed. This discharge circuit appears as  $950\text{ k}\Omega$  between the gate drive and the source connections for each MOSFET. It is only active when the A89503 is not driving the output to ensure that any charge accumulated on the MOSFET gate has a discharge path even when the power is not connected.

### Gate Drive Control

MOSFET gate drives are controlled according to the values set in Config 6, 7, and 8 registers.

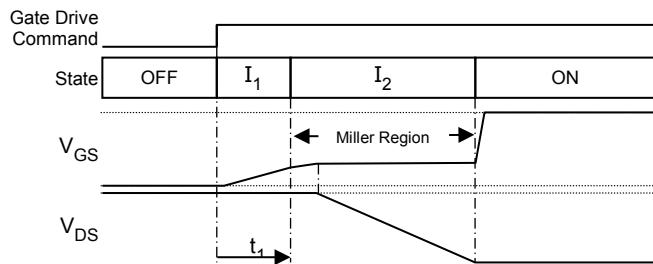

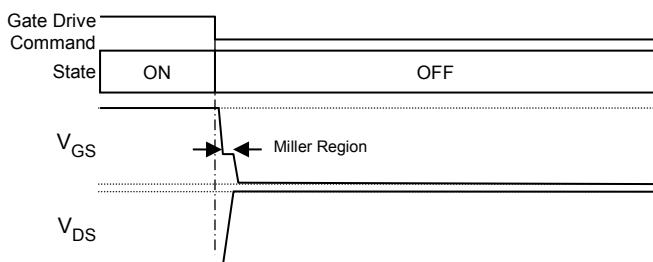

MOSFET off-to-on transitions are controlled as detailed in Figure 8a. When a gate drive is commanded to turn on a current,  $I_1$  (as defined by  $IR1[3:0]$ ), is sourced on the GH or GL terminal for a duration,  $t_1$  (defined by  $TR[3:0]$ ). These parameters should typically be set to quickly charge the MOSFET input capacitance to the start of the Miller region as drain-source voltage does not change during this period. Thereafter the current sourced on GH or GL is set to a value of  $I_2$  (as defined by  $IR2[3:0]$ ) and remains at this value while the MOSFET transitions through the Miller region and reaches the fully on state. For low-side gate drives, the MOSFET fully on state is defined as the voltage on GL gate drive output rising to a value within 1 V(typ) of  $V_{REG}$ . For the high-side gate drives the MOSFET fully on state is defined as the voltage on GH gate drive output rising to a value within 1 V(typ) of the C terminal.  $I_2$  should be set to achieve the required input capacitance charge time. Once in the fully on state, the GH or GL output switches from current to voltage drive to hold the MOSFET in the on state.

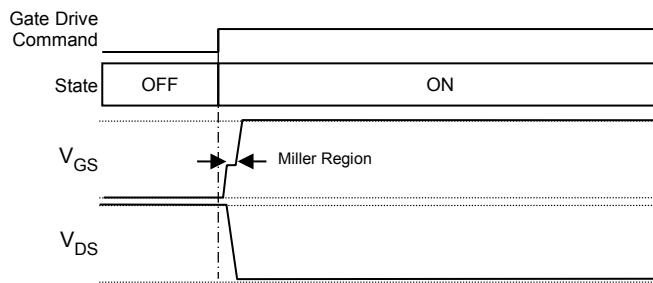

If the values of  $IR1[3:0]$  and  $IR2[3:0]$  are set to 0, GH or GL produces maximum drive to turn on the MOSFET as quickly as possible without attempting to control the MOSFET input capacitance charge time (Figure 8b). The value of  $TR[3:0]$  has no effect on switching speed.

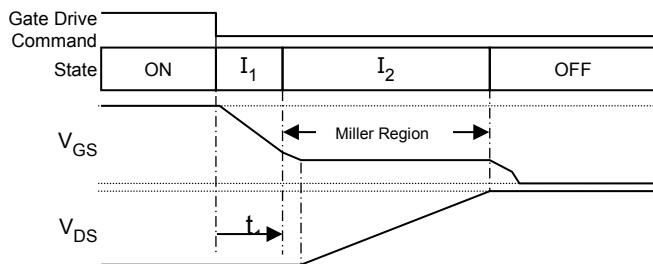

MOSFET on-to-off transitions are controlled as detailed in Figure 8c. When a gate drive is commanded to turn off a current,  $I_1$  (as defined by  $IF1[3:0]$ ), is sunk by the GH or GL terminal for a duration,  $t_1$  (defined by  $TF[3:0]$ ). These parameters should typically be set to quickly discharge the MOSFET input capacitance to the start of the Miller region as drain-source voltage does not change during this period. Thereafter, the current sunk by GH or GL is set to a value of  $I_2$  (as defined by  $IF2[3:0]$ ) and remains at this value while the MOSFET transitions through the Miller region and reaches the fully off state. For the low-side gate drives, the MOSFET fully off state is defined as the voltage on the GL gate drive output falling to a value within 1 V(typ) of LSS. For the high-side gate drives, the MOSFET fully off is defined as the voltage on the GH gate drive output falling to a value within 1 V(typ) of the S terminal.  $I_2$  should be set to achieve the required MOSFET input capacitance discharge time. Once in the fully off condition, the GH or GL output switches from current to voltage drive to hold the MOSFET in the off state. If the values of  $IF1[3:0]$  and  $IF2[3:0]$  are set to 0, GH or GL produces maximum drive to turn off the MOSFET as quickly

as possible without attempting to control the MOSFET input capacitance discharge time (Figure 8d). The value of TF[3:0] has no effect on switching speed.

Figure 8a: Off-to-On Transition (Gate Drive)

Figure 8b: Off-to-On Transition (Switched)

Figure 8c: On-to-Off Transition (Gate Drive)

Figure 8d: On-to-Off Transition (Switched)

## Logic Control Inputs

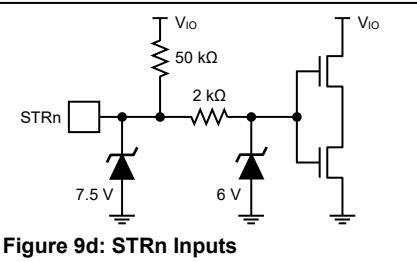

Two logic level digital inputs provide direct control for the gate drives, one for each drive. These are standard CMOS levels referenced to the voltage of the logic I/O regulator. All have a typical hysteresis of 500 mV to improve noise performance. Each input can be shorted to the VBB supply, up to the absolute maximum supply voltage, without damage to the input.

Input HS is active high and controls the high-side drive. LSn is active low and controls the low-side drive. HS has a pull-down resistor and LSn has a pull-up resistor to ensure an off state should the control signal become disconnected. The logical relationship between the inputs and the gate drive outputs is defined in Table 1.

The gate drive outputs can also be controlled through the serial interface by setting the appropriate bit in the control register. In the control register, all bits are active high. The logical relationship between the register bit setting and the gate drive outputs is defined in Table 2.

The logic inputs are combined, using logical OR, with the corresponding bits in the serial interface control register to determine the state of the gate drive. The logical relationship between the combination of logic input and register bit setting and the gate drive outputs is defined in Table 3. In most applications, either the logic inputs or the serial control will be used. When using only the logic inputs to control the bridge, the serial register should be left in the reset condition with all control bits set to 0. When using only the serial interface to control the bridge, the inputs should be tied such that the active low inputs are pulled high and the active high inputs connected to GND, i.e., HS tied to GND and LSn tied high.

## Output Disable

The ENABLE input is connected directly to the gate drive output command signal, bypassing all gate drive control logic. This can be used to provide a fast output disable (emergency cutoff).

## Sleep Mode

RESETn is an active-low input which allows the A89503 to enter sleep mode, in which the current consumption from the VBB supply and internal logic regulator is reduced to its minimum level. When RESETn is held low for longer than the reset shutdown time,  $t_{RSD}$ , the regulator and all internal circuitry is disabled and the A89503 enters sleep mode. In sleep mode, the latched faults and corresponding fault flags are cleared. When coming out of sleep mode, the protection logic ensures that the gate drive

outputs are off until the charge pump reaches its correct operating condition. The charge pump will stabilize in less than 3 ms under nominal conditions.

To allow the A89503 to start up without the need for an external logic input, the RESETn terminal can be pulled to VBB with an external pull-up resistor.

RESETn can also be used to clear any fault conditions without entering sleep mode by taking it low for the reset pulse width,  $t_{RST}$ . Any latched short detection fault, which disables the outputs, will be cleared, as will the serial fault register.